(54) ЦИФРОВОЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 1986 |

|

SU1374218A2 |

| Цифровой преобразователь координат | 1983 |

|

SU1163322A1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Цифровой преобразователь координат | 1979 |

|

SU842801A1 |

| Преобразователь кода угла в коды синуса и косинуса | 1977 |

|

SU684554A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1257638A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1290307A1 |

| Устройство для вычисления полинома @ -ой степени | 1985 |

|

SU1305670A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1141404A1 |

| Цифровой преобразователь координат | 1981 |

|

SU960834A1 |

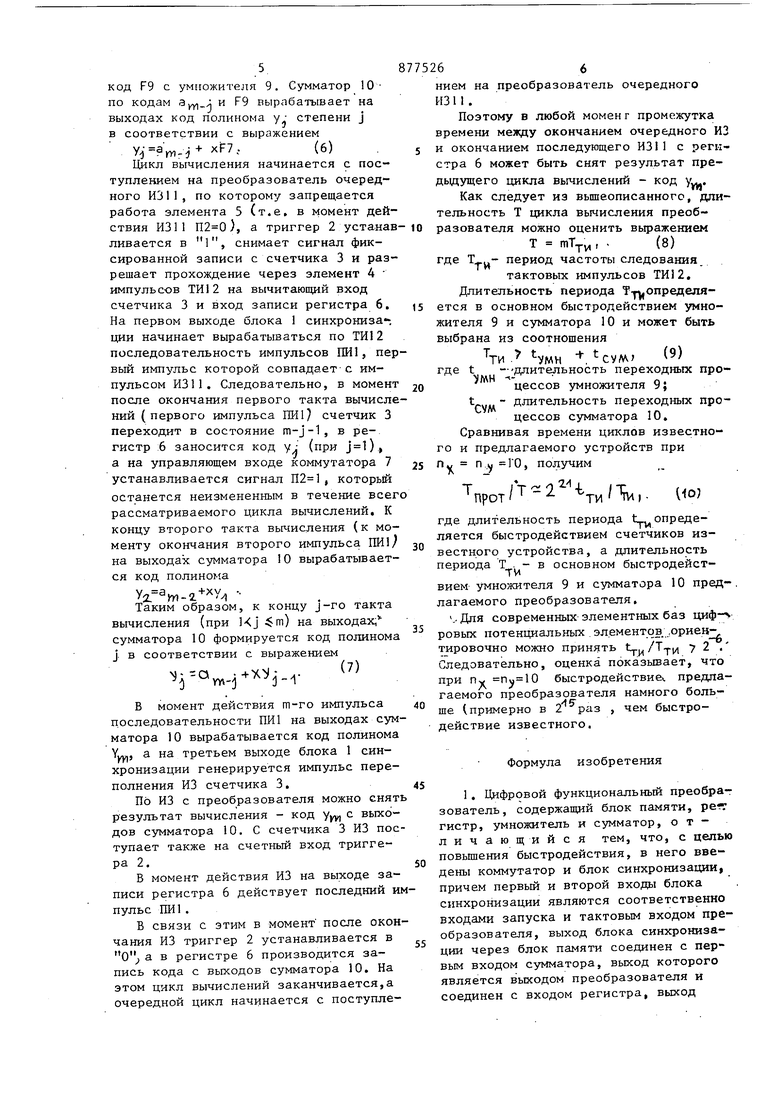

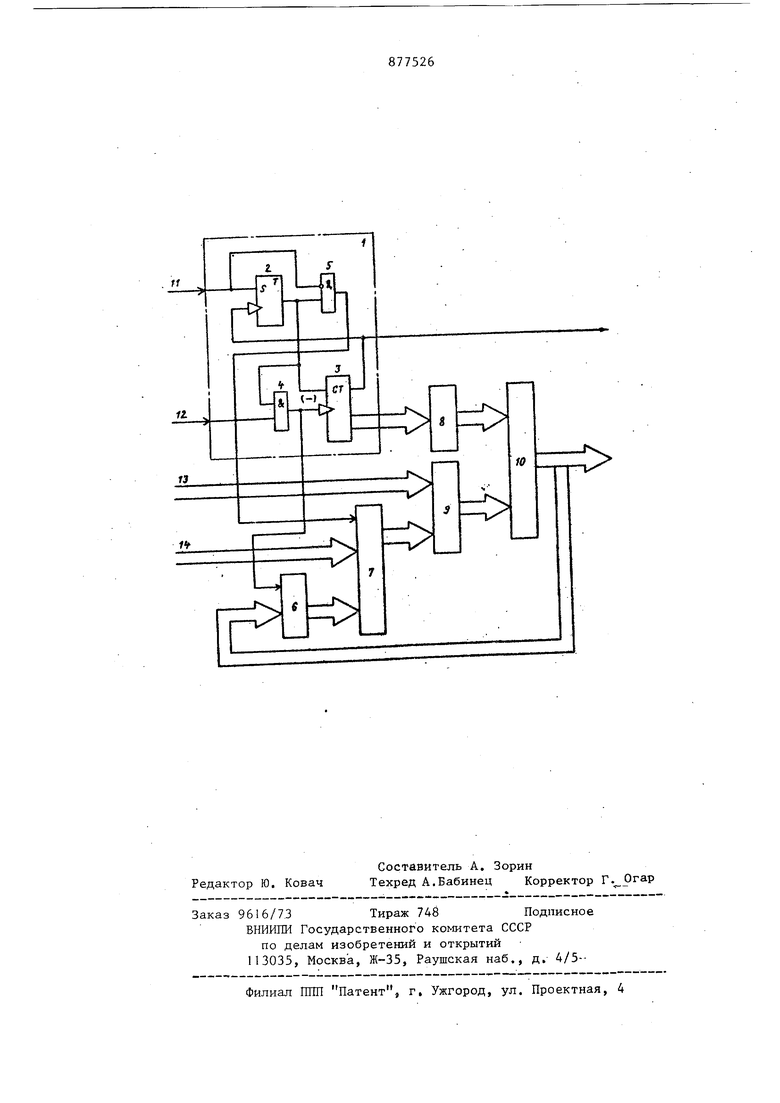

Изобретение относится к вычислительйой технике и предназначено для воспроизведения по коду аргумента х алгебраических полиномов вида im О Известно устройство с числоимпульсным представлением аргумента LlJ. Однако известное устройство имеет низкое быстродействие, определяемое в основном временем .представления аргумента числоимпульсным кодом, В связи с этим при цифровом представлении аргумента и коэффициентов ai практическое распространение полу чают устройства, в которых вычисление U) проводится по так называемой схеме Горнера :Jw,,-.( ч(,).-.). Наиболее близким к предлагаемому по технической сущности является уст (1) ройство, содержащее блок памяти, регистр, умножитель и сумматор . Недостатком этого преобразователя является низкое быстродействие, обусловленное тем, что операция перемножения в умножителе осуществляется с помощью обратных связей по сигналам переполнений счетчиков умножителя, а также тем, что слагаемые поступают на сумматор в разные моменты времени. Цель изобретения - повьппение быст-родействия. Поставленная цель достигается тем, что в устройство содержащее блок памяти, регистр, умножитель и сумматор дополнительно введены коммутатор и блок синхронизации, причем первый и второй входы блока синхронизации яв-. ляются соответственно входами запуска и тактовым входом преобразователя, выход блока, синхронизации через блок памяти соединен с первым входом сумматора, выход которого является выходом преобразователя и соединен со входом регистра, выход которого подключен к первой группе входов коммутатора, вторая группа входов которог является входом коэффициента преобра зователя, выходы коммутатора соединены с первой группой входов умнолсителя, вторая группа входов которого является входом аргумента преобразователя, выходы умножителя соединены Со вторым входом сумматора, первый и второй управляющие выходы блока синхронизации соединены с управляющи ми входами соответственно регистра и . коммутатора, третий управляющий выхо блока синхронизации является синхронизирующим выходом преобразователя. Блок синхронизации содержит триггер два элемента И и счетчик, причем nepBbrtJ вход блока синхронизации соединен с входом триггера и инверсным входом первого элемента И, прямо вход которого подключен к выходу три гера первому входу второго элемента И и вх:оду счетчика, тактовый вход ко торого соединен с выходом второго эл мента И и является первым управляющим выходом блока синхронизации, вто рой управляющий выход которого соеди нен с выходом первого элемента И, второй вход второго элемента И является тактовым входом, блока синхронизации, тактовый вход триггера соединен с выходом переполнения счетчика и является третьим управляющим вы ходом блока синхронизации, выходом к торого являются выходы счетчика. На чертеже представлена блок-схема устройства. Преобразователь содержит блок 1 синхронизации, состоящий из триггера 2, счетчика 3 и элементов И 4 и 5, регистр 6, коммутатор 7, блок 8 памяти, умножитель 9, сумматор 10, вхо 11 запуска, вход 12 тактовых импульсов, вход 13 кода аргумента и вход 14 кода коэффициента. Выполнен преобразователь на базе потенциальных цифровых элементов, триггеры которой переключаются в некоторые моменты времени после окончания импульсов на их синхронизирующ входах. Предлагаемый преобразователь реал зует алгоритм (2) и работает во времени циклически. Запуск каждого цикл I 1 П вычисления производится с входа импульсам запуска ИЗ 11, следующим с частотой fj,.j, а работа в цикле синхр низируется с.входа 12 по тактовым им пульсам ТИ12, следуюищм с частотой f-j-jf, При этом импульсы ИЗ II и импульсы ТИ12 синхронизированы между собой так, что каждый ИЗ 11 по длительности совпадает с одним из ТИ12, а Каждый цикл работы преобразователя состоит из m тактов, в течение каждого из которых выполняется операция умножения на параллельном комбинационном умножителе 9 и операция сложения на параллельном комбинационном сумматоре 10. В конце кадого такта вычисления (начале последующего такта) результат вычислений с выходов сумматора 10 заносится в регистр 6. Перед началом очередного цикла вычислений триггер 2 находится в О и выдает через элемент 5 .на выход блока 1 синхронизации логический сигнал , поступающий на управляющий, вход коммутатора 7. На другие входы коммутатора 7 приходит с входов 14 преобразователя код коэффициента а, а с выходов регистра 6 - код функ1у1и F6. Коммутатор 7 .по сигналу П2 и кодам ауу|И F6 формирует на выходах код функции F7 в соответствии с выражением Р а П2+РбП2 (4) С входов 13 преобразователя код аргумента X поступает на входы первого сомножителя умножителя 9, на входы второго сомножителя которого с коммутатора 7 приходит код F7. Умножитель 9 по кодам X и F7 вырабатывает на выходах код функции F9 в соответствии с выражением .(5) Кроме того. Так как перед началом цикла вычислений триггер 2 находится О, то сигналом О с прямого ча триггера 2 запрещена работа элемента 4, а в счетчик 3 производится фиксированная запись кода числа m-j при j l , где j - номер такта вычисления, принимающий в течение каждого цикла вычисления значения от 1 до m включительно, I . С группы выходов блока 1 синхронизации (т.-е. с выходов счетчика 3} код числа m-j поступает на адресные входы блока 8 памяти, в котором содержатся коды коэффициентов а, 1-й. 0 Блок 8 памяти по коду m-j вьфабатывает на выходах код коэффициента ау,л, поступающий на входы первого слагаемого сумматора 10, на входы другого слагаемого которого поступает код F9 с умножителя 9, Сумматор 10 по кодам и F9 вырабатывает на выходах код полинома у - степени j в соответствии с выражением (6) вычисления начинается с поступлением на преобразователь очередного ИЗ 11, по которому запрещается работа элемента 5 (т.е. в момент действия ИЗ 11 ), а триггер 2 уставав ливается в 1, снимает сигнал фиксированной записи с счетчика 3 и разрешает прохождение через элемент 4 импульсов ТИ12 на вычитающий вход счетчика 3 и вход записи регистра 6. На первом выходе блока 1 синхрониза, ции начинает вырабатываться по ТИ12 последовательность импульсов ПИ1, пер вый импульс которой совпадает-с импульсом И311. Следовательно, в момент после окончания первого такта вычисле ний (первого импульса ПИ1 счетчик 3 переходит в состояние m-j-1, в регистр :6 заносится код у- (при j l) а на управляющем входе коммутатора 7 устанавливается сигнал П2, которьй останется неизмененным в течение всег рассматриваемого цикла вычислений, К концу второго такта вычисления (к моменту окончания второго импульса на выходах сумматора 10 вырабатывается код полинома Таким образом, к концу j-ro такта вычисления (при ) на выходах, сумматора 10 формируется код полинома j в соответствии с выражением в момент действия т-го импульса последовательности ПИ1 на выходах сум матора 10 вырабатывается код полинома Yj, а на третьем выходе блока 1 синхронизации генерируется импульс переполнения ИЗ счетчика 3. По ИЗ с преобразователя можно снят результат вычисления - код Ууу, с выходов сумматора 10. С счетчика 3 ИЗ пос тупает также на счетный вход триггера 2, В момент действия ИЗ на выходе записи регистра 6 действует последний и пульс 1Ш1 . В связи с этим в момент после окон чания ИЗ триггер 2 устанавливается в а в регистре 6 производится запись кода с выкодов сумматора 10. На этом цикл вычислений заканчивается,а очередной цикл начинается с поступлением на преобразователь очередного ИЗ 1 1 . Поэтому в любой момен г промежутка времени между окончанием очередного ИЗ и окончанием последующего И311 с регистра 6 может быть снят результат предыдущего цикла вычислений - код у. Как следует из вышеописанного, длительность Т цикла вычисления преобразователя можно оценить выражением Т тТ. где период частоты следования тактовых импульсов ТИ12. Длительность периода Туу,определяется в основном быстродействием умножителя 9 и сумматора 10 и может быть выбрана из соотношения Ти . v.Au t VMH . -Cy/W где t --длительность переходных про/Мп . цессов умножителя 9} VvM A-™i JibHocTb переходных процессов сумматора 10. Сравнивая времени циклов известного и предлагаемого устройств при п., п .у ГО, получим Т /V с: О Ф (Т ПРОТ / ТИ ТИ I где длительность периода t- определяется быстродействием счетчиков известного устройства, а длительность периода Т - в основном быстродействием умножителя 9 и сумматора 10 предлагаемого преобразователя, .. Для современных элементных баз циф- ровых потенциальных элементов. ,ориентировочно можно принять 72 . Следовательно, оценка показывает, что при HV быстродействие предлагаемого преобразователя намного больше (примерно в 2 раз , чем быстродействие известного. Формула изобретения 1. Цифровой функциональный преобразователь, содержащий блок памяти, pef7 гистр, умножитель и сумматор, отличающийся тем, что, с целью повышения быстродействия, в него введены коммутатор и блок синхронизации, причем первый и второй входы блока синхронизации являются соответственно входами запуска и тактовым входом преобразователя, выход блока синхронизации через блок памяти соединен с первым входом сумматора, выход которого является выходом преобразователя И соединен с входом регистра, выход

которого подключен к первой группе входов коммутатора, вторая группа входов которого является.входом коэффициента преобразователе, выходы коммутатора соединены с первой группой входрв умножителя, вторая группа входов которого является входом аргумента преобразователя, выходы умножателя соединены с вторым входом сумматора, первый и второй управляющие выходы блока синхронизации соединены с управляющими входами соответственно ре« гистра и коммутатора, третий управляющий выход блока синхронизации является синхронизирующим-выходом преобразователя.

выходы счетчика.

Источники информации, принятые во внимание при экспертизе

tt

4J

(-}

It

13

1

О

10

i

Авторы

Даты

1981-10-30—Публикация

1979-11-26—Подача