4

/s

Изобретение относится к вычислительной технике, в частности к устройствам для реализации математических зависимостей и предназначено для вычисления по цифровым двоичным кодам аргумента х, коэффициента а и параметра N математических зависимостей вида

Л

k 0

i, и

-1

8kX

axk;

k 1

3kXk

d)

(2)

(3)

и может быть использовано в устройствах обработки данных при решении задач аппроксимации элементарных функций, вычисления произведения конечного числа сомножителей и вычисления суммы N парных произведений аппаратными методами. Цель изобретения - расширение функциональных возможностей за счет

дополнительного вычисления зависимо- м

ft

стей и axk и У akxk,

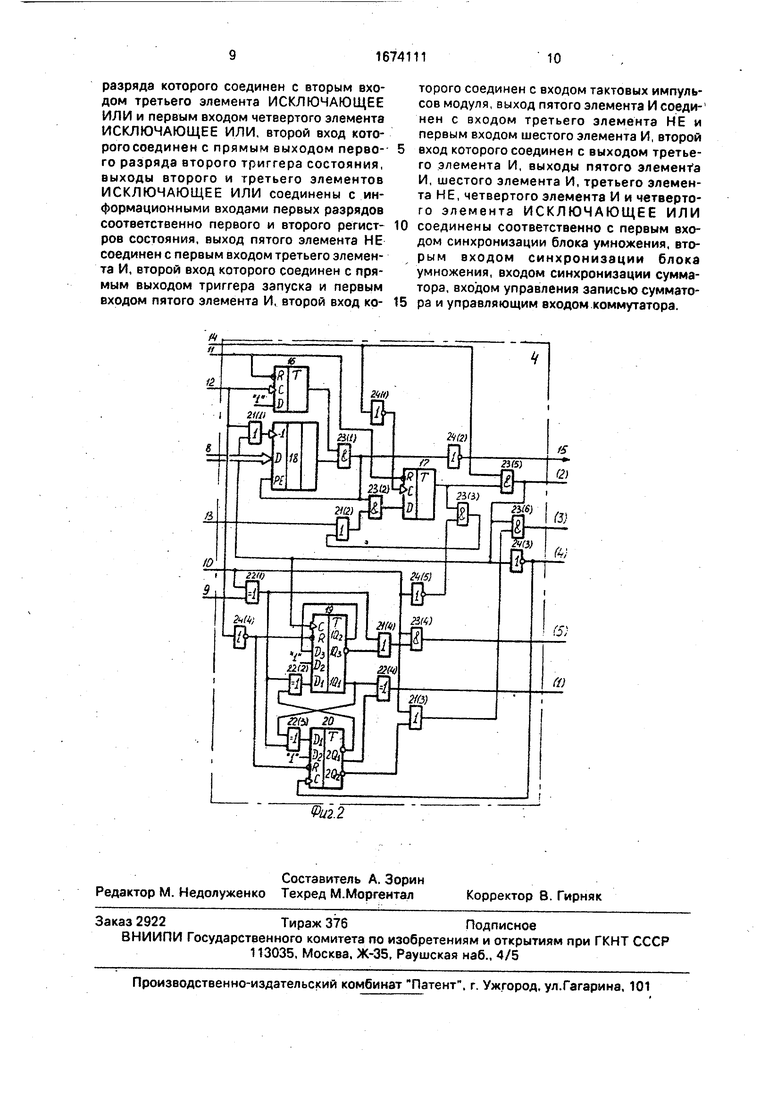

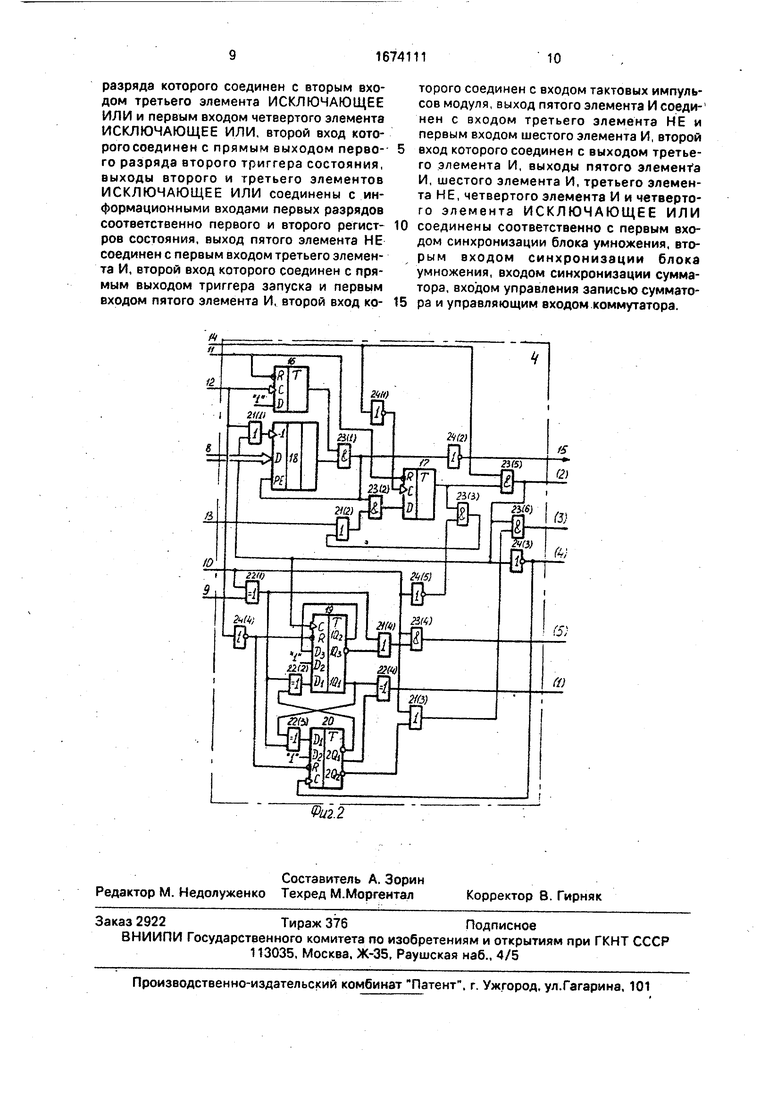

На фиг. 1 приведена блок-схема процессорного модуля; на фиг. 2 - функциональная схема блока управления процессорного модуля.

Процессорный модуль содержит блок 1 умножения, сумматор 2, коммутатор 3, блок 4 управления, вход 5 коэффициента, вход 6 аргумента, выход 7 результата, вход 8 количества слагаемых, первый и второй входы 9 и 10 кода режима, вход 11 начальной установки, вход 12 запуска, вход 13 разрешения запуска, вход 14 тактовых импульсов и выход готовности, результата 15.

Блок 4 управления содержит триггер 16 установки, триггер 17 запуска, счетчик 18, первый 19 и второй 20 регистры состояний, элементы ИЛИ 21 (1) - 21 (4), элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 22 (1), - 22 (4), элементы И 23 (1) и 23 (6) - элементы НЕ 24 (1) - 24 (5).

Здесь и в дальнейшем цифрами в скобах, стоящими после номера позиций, показаны порядковые номера совершенно одинаковых по своему функциональному назначению и техническому исполнению элементов, а цифрами в скобах, стоящими возле контура блоков, показаны порядковые номера их входов или выходов.

Процессорный модуль предназначен для работы в трех режимах, соответствующих вычислению математических зависимостей (1), (2) и (3). Настройка модуля на работу в определенном режиме осуществляется заданием соответствующего кода (F1F2) по

первому 9 и второму 10 входам кода режима модуля.

Математическая зависимость, вычисляемая при работе процессорного модуля в режиме, заданном кодом (F1F2) микроинструкции на входах 9 и 10 процессорного модуля определяется в соответствии с соотношением (4)

м

.k.

F2F1

01

10

I, ft

Z 2, akx

k 0

Z J1 axk. k 1

(4)

11

-S

, akXk

k 1

Процессорный модуль работает следующим образом.

По входам 9 и 10 модуля задается цифQ ровой двоичный код (F1F2), соответствующий вычисляемой математической зависимости.

По сигналу начальной установки с входа 11 модуля производится обнуление тригге5 ре 16 установки и триггера 17 запуска. Нулевой сигнал с выхода триггера установки 16 через первый элемент И 23 (1) подается на вход разрешения записи счетчика 18, определяя работу его в режиме загрузки

Q информации, подаваемой со входа 8 параметра N. Одновременно тот же нулевой сигнал с выхода первого элемента И 23 (1), через второй элемент И 23 (2) устанавливает низкий потенциал на информационном вхо5 де триггера 17 запуска.

Нулевой сигнал с прямого выхода триггера 17 запуска, подаваемого на второй вход пятого элемента И 23 (5) исключает возможность формирования синхросигна0 лов TL Тх и Т2 на (2), (3) и (4) выходах блока

4 управления, а через третий элемент И 23

(3) устанавливается низкий потенциал на

втором входе второго элемента ИЛИ 21 (2).

Исходная информация вычисляемой

5 математической зависимости - а, х и N, подается соответственно на вход 5 коэффициента, вход 6 аргумента и вход 8 количества слагаемых. О наличии аргумента по входу 6 модуля свидетельствует сигнал с входа 13

0 модуля.

По сигналу запуска со входа 12 модуля производится обнуление первого 19 и второго 20 регистров состояний, занесение в счетчик 18 информации совхоза 8 (число N

е соответствует заданной математической зависимости) и приведение триггера 16 установки в единичное состояние. Единичный сигнал с прямого выхода триггера 16 установки через первый элемент И 23/13 поступает на вход разрешения записи счетчика

18, обеспечивая перевод его в счетный режим, и на первый вход второго элемента И 23 (2), обеспечивая прохождение на информационный вход триггера 17 запуска сигнала с выхода второго элемента ИЛИ 1 (2), т.е. с входа 13 модуля.

При наличии операнда по входу 6 аргумента (единичное значение сигнала на входе 13 модуля) по отрицательному фронту тактового сигнала с входа 14 триггера запуска 17 устанавливается в единичное состояние, что открывает пятый элемент И 23 (5) для прохождения тактовых импульсов С входа 14 модуля, обеспечивая возможность формирования синхросигналов Ti, Tx и Т2 на выходах соответственно (2). (3) и (4) блока 4 управления. Единичный сигнал на выходе триггера 17 запуска открывает также третий элемент И 23 (3), определяя значение сигнала на втором входе второго элемента ИЛИ 21 (2) как обратное значение сигнала F с входа 10 модуля.

Каждый вычислительный такт работы процессорного модуля состоит из двух под- тактов, что определяется наличием операций умножения и сложения, выполняемых соответственно в первом и втором подтсЖ- тах каждого такта работы модуля.

Тактовые сигналы первого - Ti и вторе го - Т2 подтактов формируются на выходах соответственно (2) и (4) блока 4 управления Каждый из двух подтактов каждого такта начинается с приходом положительного фронта соответствующего тактового сигнала - Ti или Т2.

По положительному фронту тактового сигнала с входа 14 модуля на выходе пятого элемента И 23 (5), открытого единичным сигналом с выхода триггера 17 запуска, формируется положительный фронт сигнала Тч первого подтакта, под воздействием которого изменяется состояние выходов первого триггера 19 состояний, а содержимое счетчика 18 уменьшается на 1, отсчитывая один такт работы. Синхросигнал TI через выход (2) блока 4 управления подается на вход синхронизации блока 1 умножения, Одновременно с этим при наличии единичного сигнала на выходе третьего элемента ИЛИ 21 (3), определяемого единичным значением сигнала F2 1 с входа 10 модуля или единичным значением сигнала с инверсного второго выхода второго регистра состояния 20, на выходе шестого элемента И 23 (6) формируется положительный фронт синхросигнала Тх, который через выход (3) блока 4 управления подается на вход синхронизации блока 1 умножения.

По отрицательному фронту тактового сигнала TI первого подтакта на выходе

третьего элемента НЕ 24 (3) формируется положительным фронт сигнала Т2 второго подтакта, под воздействием которого изменяется состояние выходов второго регистра 20 состояния и который через выход (4) блока 4 управления подается на вход синхронизации сумматора 2, обеспечивая занесение информации с его входов.

Таким образом, цикл работы процес0 сорного модуля, содержащий k 1,N вычислительных тактов состоит из i 1,N первых подтактов и J 1,N вторых подтактов работы.

За время первого подтакта каждого так5 та работы модуля в блоке 1 умножения происходит перемножение операндов, заносимых с первого и второго его информационных входов по положительным Фронтам синхросигналов соответственно Ti

0 и Тх. поступающим на синхровходы блока 1 умножения (2) и (3) выходов блока 4 управления.

Информация, поступающая на вход (1) блока 1 умножения, определяется управля5 ющим сигналом, вырабатываемым на первом входе (1) блока 4 управления, под воздействием которого коммутатор 3 передается на блок 1 умножения либо результат предыдущего такта работы с выхода 7 ре0 зультата модуля, либо информацию с входа 5 коэффициента модуля.

Информация, поступающая на вход (2) блока 1 умножения определяется цифровым кодом с входа 6 аргумента модуля.

5За время второго подтакта каждого

такта работы модуля в сумматоре 2 производится суммирование операндов, занесенных с его входов по положительному фронту синхросигнала Тт, поступающего на синх0 ровход сумматора 2 с выхода (4) блока 4 управления.

Информация, поступающая на вход (1) сумматора 2, вначале каждого j-того второго подтакта работы соответствует информации

5 на выходе коммутатора 3 и определяется с поправкой на значение информации с входа 5 коэффициента на начало j-того второго подтакта, значение сигнала управления работой коммутатора 3 на начало j-того

0 второго подтакта и значение сигнала разрешающего работу первого входа многовходо- вого сумматора 2, формируемого на выходе (5) блока 4 управления.

Информация, поступающая на вход (2)

5 сумматора 2, представляет собой результат работы блока 1 умножения на i-том первом подтакте.

В последнем N-ном такте работы модуля под воздействием положительного фронта синхросигнала первого подтакта Ti

содержимое счетчика 18 обращается в нуль, о чем свидетельствует вырабатываемый на его выходе сигнал нулевого уровня, который через первый элемент И 23 (1), попадая на вход разрешения записи счетчика 18, устанавливает последний в режим загрузки информации, поступая на вход второго элемента И 23 (2), определяет нулевой уровень сигнала на входе триггера 17 запуска, что обеспечивает установку последнего в нулевое состояние по отрицательному фронту тактового сигнала с входа 14, с запрещением формирования синхросигналов Ti, T2 и Тх с выходов (2), (4) и (3) блока 4 управления. Нулевой сигнал с выхода первого элемента И 23 (1) поступает также на вход второго элемента НЕ 24 (2) и выхода которого на выходе 15 модуля формируется единичный сигнал Конец цикла,

В конце второго подтакта N-ного такта работы модуля искомый результат вычислений формируется на выходе 7 результата модуля. Работа закончена.

Повторные запуски процессорного модуля осуществляются по сигналу с входа 12 запуска модуля при наличии разрешающего сигнала с входа 13 модуля без предварительной подачи сигнала с входа 11 начальной установки модуля.

Формула изобретения

Процессорный модуль, содержащий блок умножения, сумматор, коммутатор и блок управления, отличающийся тем, что, с целью расширения функциональных возможностей за счет дополнительного выft

akXk,

числения зависимостей | axk и

k 1k

выход сумматора соединен с выходом модуля и первым информационным входом коммутатора, второй информационный вход которого соединен с входом коэффициента модуля, выход коммутатора соединен с входами первого сомножителя блока умножения и первого слагаемого сумматора, вход второго слагаемого сумматора соединен с выходом блока умножения, вход второго сомножителя которого соединен с входом аргумента модуля, причем блок управления содержит триггер установки, триггер запуска, первый и второй регистры состояний, счетчик, четыре элемента ИЛИ, четыре элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, шесть элементов И, пять элементов НЕ. вход начальной установки модуля соединен с входами установки в 0й триггера установки и триггера запуска, вход синхронизации которого через первый элемент НЕ подключен к входу тактовых импульсов модуля, прямой выход триггера установки соединен с первым входом первого элемента И, второй

вход которого соединен с выходом переполнения счетчика, выход первого элемента И соединен с входом разрешения записи счетчика, первым входом второго элемента И и входом второго элемента НЕ, выход которо0 го соединен с выходом готовности результата модуля, вход пуска которого соединен с первым входом первого элемента ИЛИ и входом синхронизации триггера установки, информационный вход которого соединен с

5 входом логической единицы модуля и информационными входами вторых разрядов первого и второго регистров состояния, вход количества слагаемых модуля соединен с информационным входом счетчика,

0 вычитающий вход которого соединен с выходом первого элемента ИЛИ. второй вход которого соединен с входом синхронизации первого регистра состояния и через третий элемент НЕ с входом синхронизации второ5 го регистра состояния, вход установки в О которого соединен с входом установки в О первого регистра состояния и выходом четвертого элемента НЕ, вход которого соединен с входом пуска модуля, вход раз0 решения пуска которого соединен с первым входом второго элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом третьего элемента И и вторым входом второго элемента И, выход которого

5 соединен с информационным входом триггера запуска, вход первого разряда режима модуля соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с входом второго

0 разряда кода режима модуля, входом пятого элемента НЕ и первыми входами четвертого элемента И и третьего элемента ИЛИ, вторые входы которых соединены соответственно с выходом четвертого элемента ИЛИ

5 и инверсным выходом второго разряда второго регистра состояния, инверсный выход первого разряда которого соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен

0 с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и первым входом четвертого элемента ИЛИ, выход и второй вход которого соединены соответственно с

5 вторым входом четвертого элемента И и инверсным выходом третьего разряда первого регистра состояния, прямой выход второго разряда которого соединен с информационным входом третьего разряда первого регистра состояния, прямой выход первого

разряда которого соединен с вторым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и первым входом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с прямым выходом первого разряда второго триггера состояния, выходы второго и третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с информационными входами первых разрядов соответственно первого и второго регистров состояния, выход пятого элемента НЕ соединен с первым входом третьего элемента И. второй вход которого соединен с прямым выходом триггера запуска и первым входом пятого элемента И, второй вход ко

торого соединен с входом тактовых импульсов модуля, выход пятого элемента И соединен с входом третьего элемента НЕ и первым входом шестого элемента И, второй вход которого соединен с выходом третьего элемента И, выходы пятого элемента И, шестого элемента И. третьего элемента НЕ, четвертого элемента И и четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с первым входом синхронизации блока умножения, вторым входом синхронизации блока умножения, входом синхронизации сумматора, входом управления записью сумматора и управляющим входом коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления полиномов | 1989 |

|

SU1674112A1 |

| Функциональный преобразователь | 1988 |

|

SU1619258A1 |

| Устройство для воспроизведения функций | 1984 |

|

SU1182539A1 |

| Устройство для вычисления полинома второй степени | 1983 |

|

SU1109743A1 |

| Цифровой функциональный преобразователь | 1989 |

|

SU1695321A1 |

| Устройство для интерполяции | 1984 |

|

SU1215118A1 |

| Устройство для вычисления дискретного преобразования Фурье | 1990 |

|

SU1725228A1 |

| Функциональный преобразователь | 1989 |

|

SU1709303A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1257638A1 |

| Устройство для вычисления модуля комплексного числа | 1989 |

|

SU1693599A1 |

Изобретение относится к вычислительной технике, в частности к устройствам для арифметической обработки данных, предназначено для реализации математических зависимостей вида Z = ΣNAKXK (1), Z = ПNAXK (2) и Z = ΣNAKXK (3). Цель изобретения - расширение функциональных возможностей за счет вычисления математических зависимостей вида (2), (3). Устройство содержит блок умножения, сумматор, коммутатор и блок управления. Сущность изобретения заключается в установлении новых связей и дополнительных элементов для циклического вычисления указанных математических зависимостей. Устройство может быть использовано при построении специализированных вычислительных систем для моделирования систем уравнений и аппроксимации элементарных функций. 2 ил.

Фиг 2

| Устройство для вычисления элементарных функций | 1984 |

|

SU1185329A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-08-30—Публикация

1989-02-03—Подача