/-J7 ., s

. I

Изобретение относится к устройствам для регулирования движения транспортных средств и может быть применено для автоматического контроля скорости движения и пройденного пути транспортным средством.

Цель изобретения - повышение информативности устройства путем запоминания максимальной скорости и пройденного транспортным средством пути в течение нескольких заданных интервалов времени перед остановкой транспортного средства.

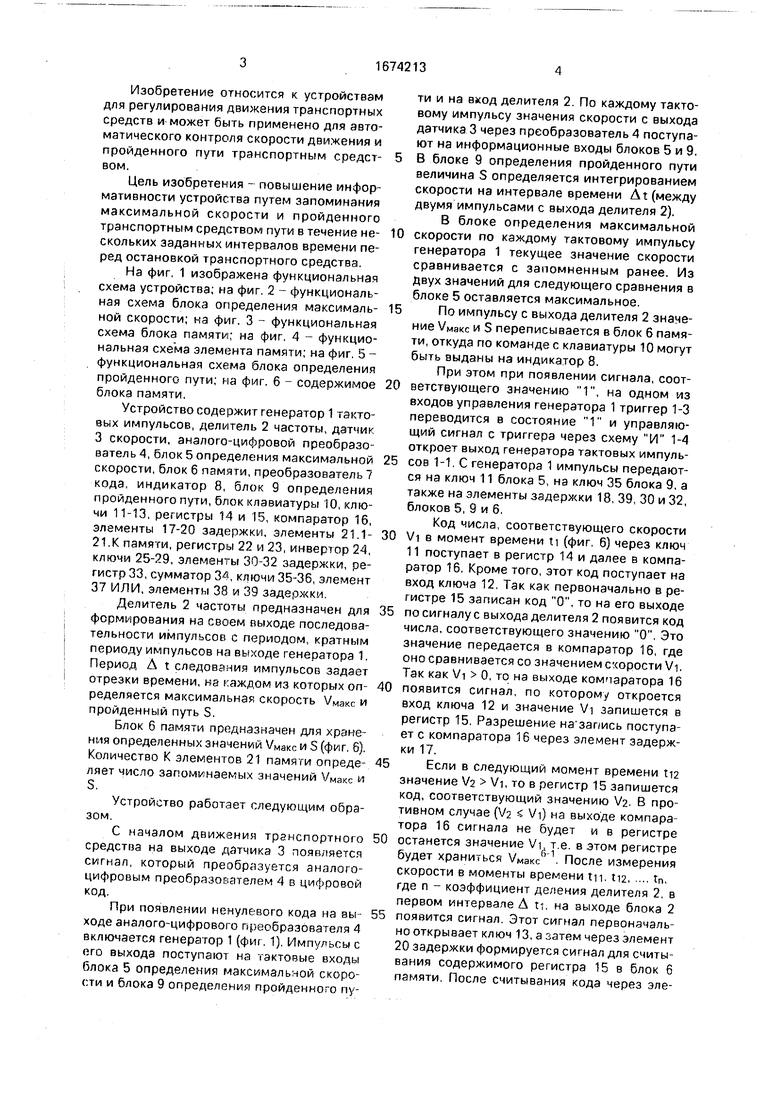

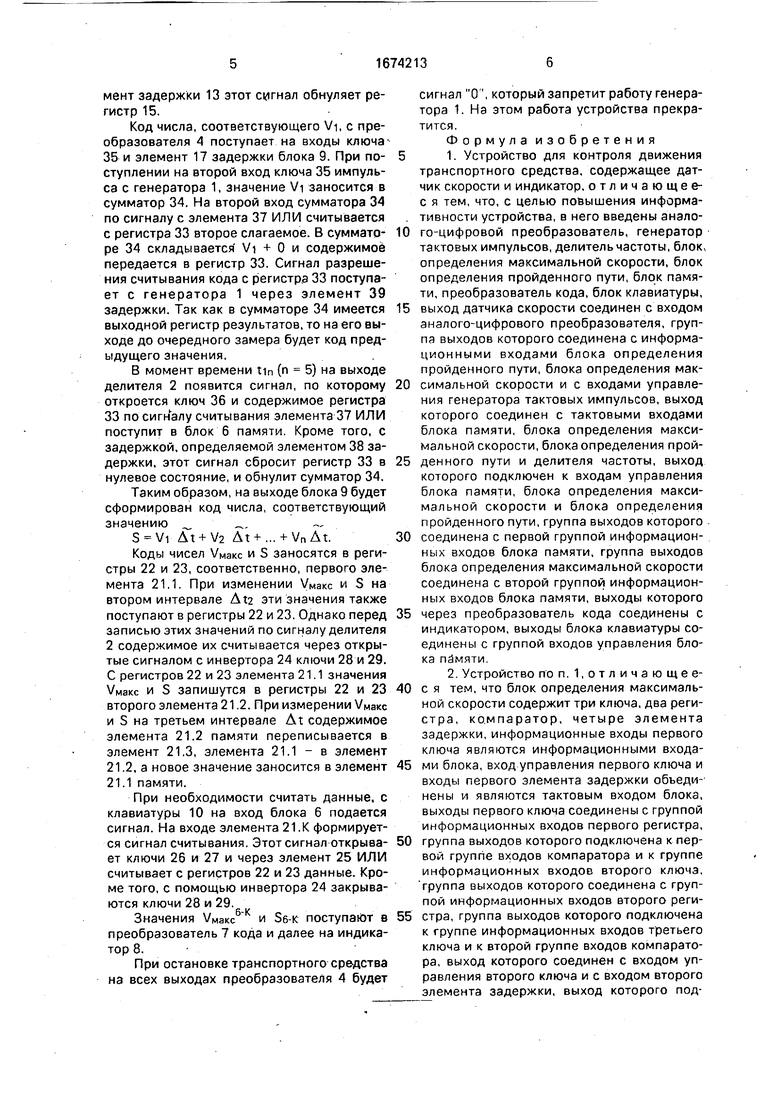

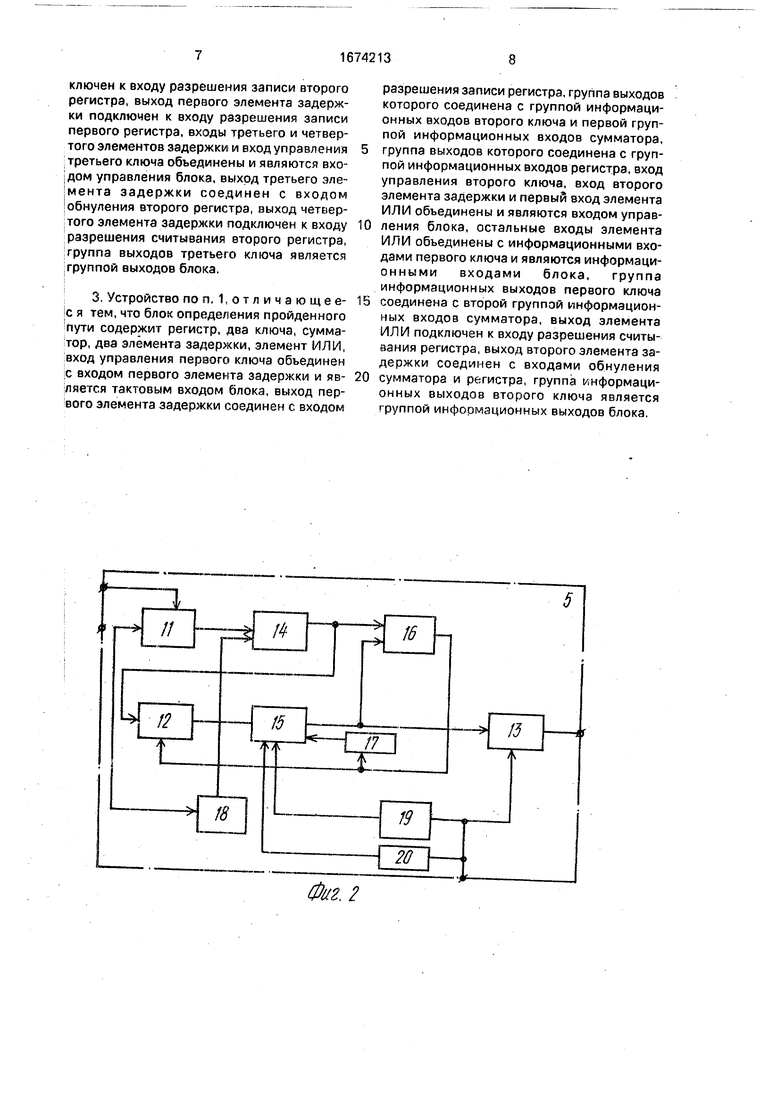

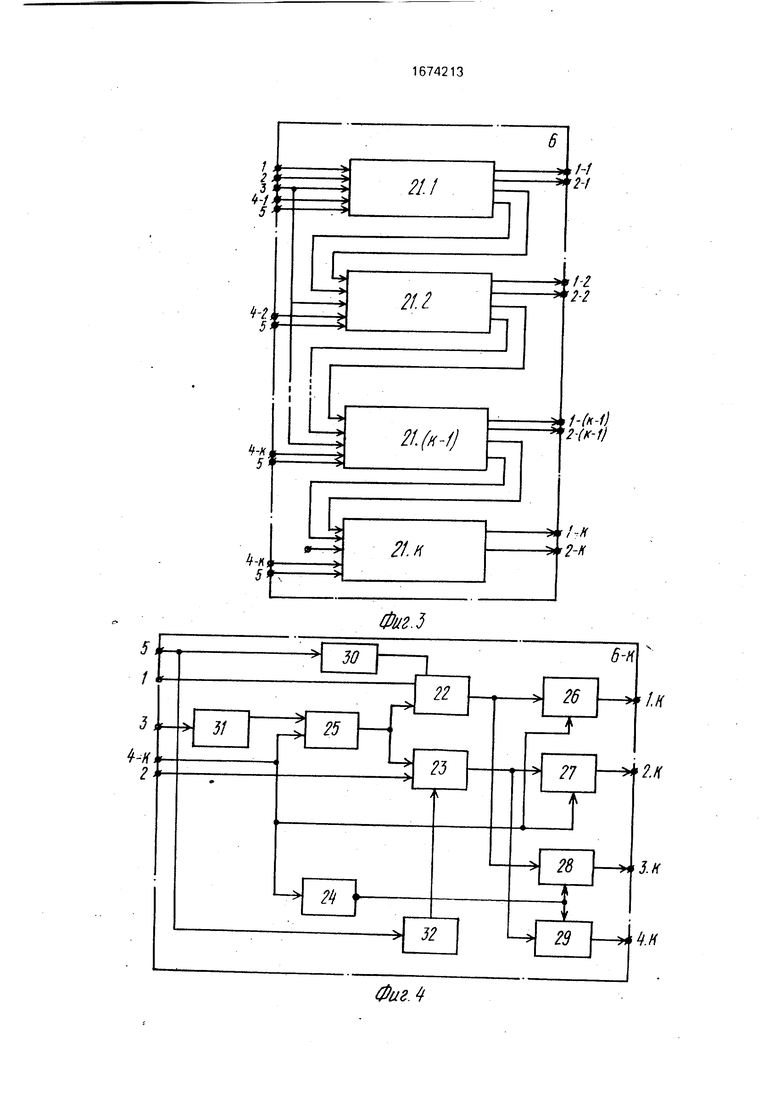

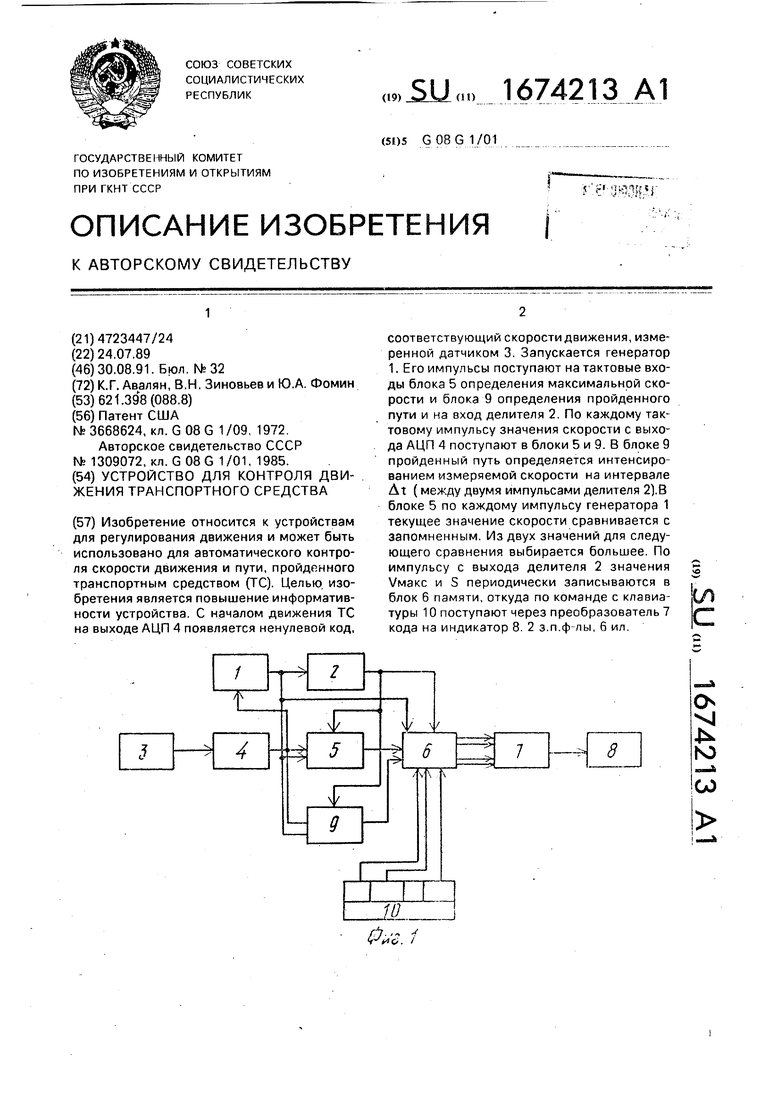

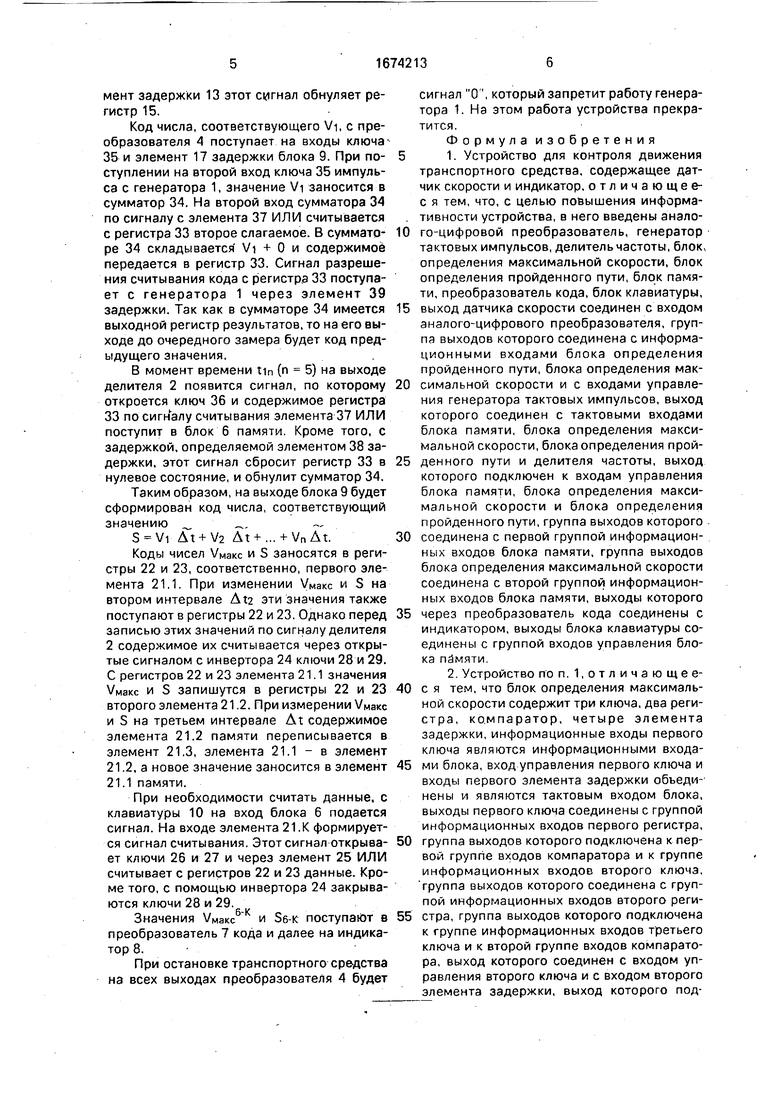

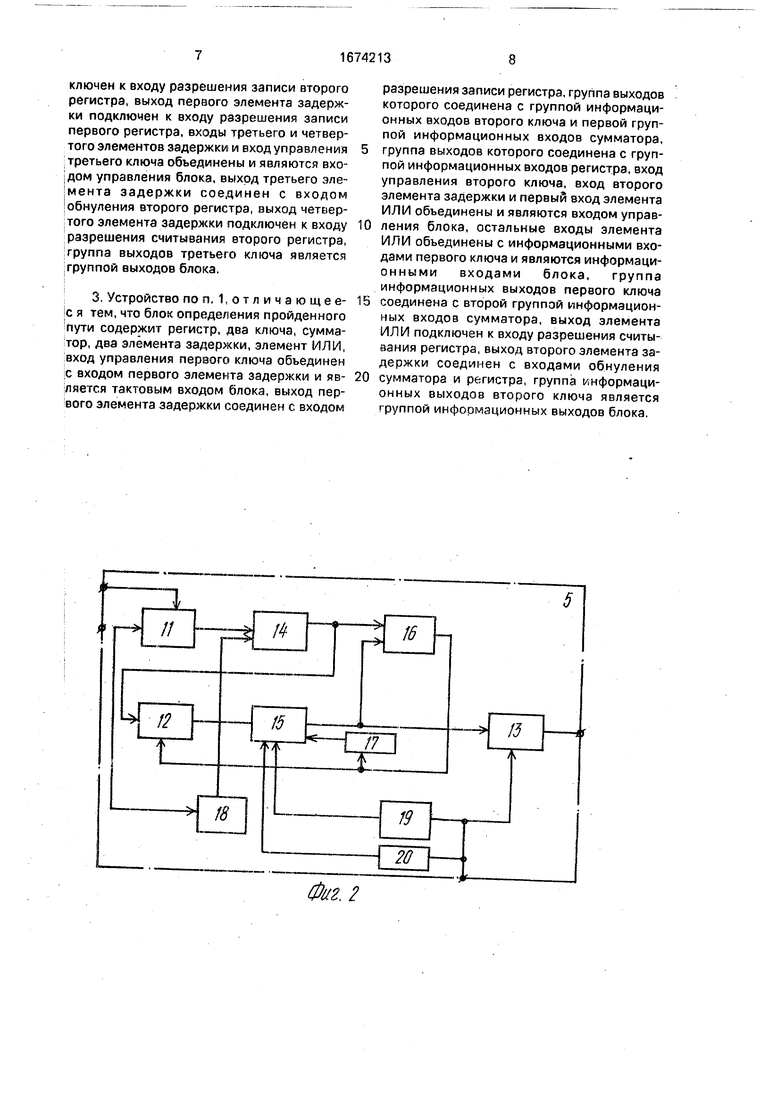

На фиг. 1 изображена функциональная схема устройства; на фиг. 2 - функциональная схема блока определения максимальной скорости; на фиг. 3 - функциональная схема блока памяти; на фиг. 4 - функциональная схема элемента памяти; на фиг 5 - функциональная схема блока определения пройденного пути; на фиг. 6 - содержимое блока памяти.

Устройство содержит генератор 1 тактовых импульсов, делитель 2 частоты, датчик 3 скорости, аналого-цифровой преобразователь 4, блок 5 определения максимальной скорости, блок 6 памяти, преобразователь 7 кода, индикатор 8, блок 9 определения пройденного пути, блок клавиатуры 10, ключи 11-13, регистры 14 и 15, компаратор 16, элементы 17-20 задержки, элементы 21 1- 21 К памяти, регистры 22 и 23, инвертор 24, ключи 25-29, элементы 30-32 задержки, регистр 33, сумматор 34, ключи 35-36 элемент 37 ИЛИ, элементы 38 и 39 задержки

Делитель 2 частоты предназначен для формирования на своем выходе последовательности импульсов с периодом, кратным периоду импульсов на выходе генератора 1. Период Д t следования импульсов задает отрезки времени, на каждом из которых определяется максимальная скорость и пройденный путь S.

Блок G памяти предназначен для хранения определенных значений VMSKC и S (фиг. 6) Количество К элементов 21 памяти определяет число запоминаемых значений Умакг и S

Устройство работает следующим образом

С началом движения транспортного средства на выходе датчика 3 появляется сигнал, который преобразуется аналого- цифровым преобразователем 4 в цифровой код

При появлении ненулевого кода на выходе аналого-цифрового преобразователя 4 включается генератор 1 (фиг. 1) Импульсы с его выхода поступают на тактовые входы блока 5 определения максимальной скорости и блока 9 определения пройденного пути и на вход делителя 2 По каждому тактовому импульсу значения скорости с выхода датчика 3 через преобразователь 4 поступают на информационные входы блоков 5 и 9.

В блоке 9 определения пройденного пути

величина S определяется интегрированием

скорости на интервале времени At (между

двумя импульсами с выхода делителя 2).

В блоке определения максимальной

скорости по каждому тактовому импульсу генератора 1 текущее значение скорости сравнивается с запомненным ранее. Из двух значений для следующего сравнения в блоке 5 оставляется максимальное

По импульсу с выхода делителя 2 значение /макс и S переписывается в блок 6 памяти, откуда по команде с клавиатуры 10 могут быть выданы на индикатор 8.

При этом при появлении сигнала, соответствующего значению 1. на одном из входов управления генератора 1 триггер 1-3 переводится в состояние 1 и управляющий сигнал с триггера через схему И 1-4 откроет выход генератора тактовых импульсов 1-1 С генератора 1 импульсы передаются на ключ 11 блока 5, на ключ 35 блока 9, а также на элементы задержки 18 39, 30 и 32, блоков 5, 9 и 6,

Код числа, соответствующего скорости

Vi в момент времени ti (фиг. 6) через ключ 11 поступает в регистр 14 и далее в компаратор 16. Кроме того, этот код поступает на вход ключа 12. Так как первоначально в регистре 15 записан код О, то на его выходе

по сигналу с выхода делителя 2 появится код числа, соответствующего значению О. Это значение передается в компаратор 16, где оно сравнивается со значением схорости VL Так как Vi 0, то на выходе компаратора 16

появится сигнал, по котором/ откроется вход ключа 12 и значение Vi запишется в регистр 15. Разрешение на запись поступает с компаратора 16 через элемент задержки 17

Если в следующий момент времени ti2 значение /2 Vi, то в регистр 15 запишется код, соответствующий значению /2. В противном случае (V2 $ Vi) на выходе компара тора 16 сигнала не будет и в регистре

останется значение Vi т е в этом регистре будет храниться VMBKC 1 После измерения скорости в моменты времени tn 112, tn где п - коэффициент деления делителя 2 в первом интервале Д ti на выходе блока 2

появится сигнал Этот сигнал первоначально открывает ключ 13, а атем через элемент 20 задержки формируется сигнал для считы вания содержимого регистра 15 в блок 6 памяти После считывания кода через эле

мент задержки 13 этот сигнал обнуляет регистр 15.

Код числа, соответствующего Vi, с преобразователя 4 поступает на входы ключа 35 и элемент 17 задержки блока 9. При поступлении на второй вход ключа 35 импульса с генератора 1, значение Vi заносится в сумматор 34. На второй вход сумматора 34 по сигналу с элемента 37 ИЛИ считывается с регистра 33 второе слагаемое. В сумматоре 34 складывается Vi + 0 и содержимое передается в регистр 33. Сигнал разрешения считывания кода с регистра 33 поступа ет с генератора 1 через элемент 39 задержки. Так как в сумматоре 34 имеется выходной регистр результатов, то на его выходе до очередного замера будет код предыдущего значения.

В момент времени tin (п 5) на выходе делителя 2 появится сигнал, по которому откроется ключ 36 и содержимое регистра 33 по сигналу считывания элемента 37 ИЛИ поступит в блок 6 памяти Кроме того, с задержкой, определяемой элементом 38 задержки, этот сигнал сбросит регистр 33 в нулевое состояние, и обнулит сумматор 34.

Таким образом, на выходе блока 9 будет сформирован код числа, соответствующий значению .

S Vi At + V2 At + ... - Vn At.

Коды чисел /Макс и S заносятся в регистры 22 и 23. соответственно, первого элемента 21.1. При изменении УМакс i. 5 на втором интеррале At2 эти значения также поступают в регистры 22 и 23. Однако перед записью этих значений по сигналу делителя 2 содержимое их считывается через открытые сигналом с инвертора 24 ключи 28 и 29. С регистров 22 и 23 элемента 21.1 значения VMBKC и S запишутся в регистры 22 и 23 второго элемента 212. При измерении Умакс и S на третьем интервале At содержимое элемента 21.2 памяти переписывается в элемент 21.3, элемента 21.1 - в элемент 21,2, а новое значение заносится в элемент 21.1 памяти.

При необходимости считать данные, с клавиатуры 10 на вход блока 6 подается сигнал. На входе элемента 21 .К формируется сигнал считывания. Этот сигнал открывает ключи 26 и 27 и через элемент 25 ИЛИ считывает с регистров 22 и 23 данные. Кроме того, с помощью инвертора 24 закрываются ключи 28 и 29.

Значения 7макс к и 5б-к поступают в преобразователь 7 кода и далее на индикатор 8.

При остановке транспортного средства на всех выходах преобразователя 4 будет

сигнал О , который запретит работу генератора 1. На этом работа устройства прекратится.

Формула изобретения

1. Устройство для контроля движения

транспортного средства, содержащее датчик скорости и индикатор, отличающее- с я тем. что, с целью повышения информативности устройства, в него введены анало0 го-цифровой преобразователь, генератор тактовых импульсов, делитель частоты, блок определения максимальной скорости, блок определения пройденного пути, блок памяти, преобразователь кода, блок клавиатуры,

5 выход датчика скорости соединен с входом аналого-цифрового преобразователя, группа выходов которого соединена с информационными входами блока определения пройденного пути, блока определения мак0 симальной скорости и с входами управления генератора тактовых импульсов, выход которого соединен с тактовыми входами блока памяти, блока определения максимальной скорости, блока определения прой5 денного пути и делителя частоты, выход которого подключен к входам управления блока памяти, блока определения максимальной скорости и блока определения пройденного пути, группа выходов которого

0 соединена с первой группой информационных входов блока памяти, группа выходов блока определения максимальной скорости соединена с второй группой информационных входов блока памяти, выходы которого

5 через преобразователь кода соединены с индикатором, выходы блока клавиатуры соединены с группой входов управления блока памяти.

2 Устройство поп. 1,отличающее0 с я тем, что блок определения максимальной скорости содержит три ключа, два регистра, компаратор, четыре элемента задержки, информационные входы первого ключа являются информационными входа5 ми блока, вход управления первого ключа и входы первого элемента задержки объединены и являются тактовым входом блока, выходы первого ключа соединены с группой информационных входов первого регистра.

0 группа выходов которого подключена к первой группе входов компаратора и к группе информационных входов второго ключа, группа выходов которого соединена с группой информационных входов второго реги5 стра, группа выходов которого подключена к группе информационных входов третьего ключа и к второй группе входов компаратора, выход которого соединен с входом управления второго ключа и с входом второго элемента задержки, выход которого подключей к входу разрешения записи второго регистра, выход первого элемента задержки подключен к входу разрешения записи первого регистра, входы третьего и четвертого элементов задержки и вход управления третьего ключа объединены и являются входом управления блока, выход третьего элемента задержки соединен с входом обнуления второго регистра, выход четвертого элемента задержки подключен к входу разрешения считывания второго регистра, группа выходов третьего ключа является группой выходов блока.

3. Устройство по п. 1,отличающее- с я тем, что блок определения пройденного пути содержит регистр, два ключа, сумматор, два элемента задержки, элемент ИЛИ, вход управления первого ключа объединен с входом первого элемента задержки и является тактовым входом блока, выход первого элемента задержки соединен с входом

разрешения записи регистра, группа выходов которого соединена с группой информационных входов второго ключа и первой группой информационных входов сумматора,

группа выходов которого соединена с группой информационных входов регистра, вход управления второго ключа, вход второго элемента задержки и первый вход элемента ИЛИ объединены и являются входом управления блока, остальные входы элемента ИЛИ объединены с информационными входами первого ключа и являются информаци- онными входами блока, группа информационных выходов первого ключа

соединена с второй группой информационных входов сумматора, выход элемента ИЛИ подключен к входу разрешения считывания регистра, выход второго элемента задержки соединен с входами обнуления

сумматора и регистра, группа информационных выходов второго ключа является группой информационных выходов блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования синусно-косинусного трансформаторного датчика угла | 1990 |

|

SU1778766A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ УГЛА ПОВОРОТА ВАЛА В КОД | 1993 |

|

RU2108663C1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ | 1998 |

|

RU2174699C2 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| Самонастраивающееся устройство управления | 1983 |

|

SU1130830A1 |

| Цифровой коррелятор | 1989 |

|

SU1711181A1 |

| Корреляционный измеритель времени запаздывания | 1983 |

|

SU1160433A1 |

| Устройство для контроля параметров | 1985 |

|

SU1291930A1 |

Изобретение относится к устройствам для регулирования движения и может быть использовано для автоматического контроля скорости движения и пути, пройденного транспортным средством /ТС/. Целью изобретения является повышение информативности устройства. С началом движения ТС на выходе АЦП 4 появляется ненулевой код, соответствующий скорости движения, измеренной датчиком 3. Запускается генератор 1. Его импульсы поступают на тактовые входы блока 5 определения максимальной скорости и блока 9 определения пройденного пути и на вход делителя 2. По каждому тактовому импульсу значения скорости с выхода АЦП 4 поступают в блоки 5 и 9. В блоке 9 пройденный путь определяется интенсированием измеряемой скорости на интервале ΔТ (между двумя импульсами делителя 2). В блоке 5 по каждому импульсу генератора 1 текущее значение скорости сравнивается с запомненным. Из двух значений для следующего сравнения выбирается большее. По импульсу с выхода делителя 2 значения Vмакс и S периодически записываются в блок 6 памяти, откуда по команде с клавиатуры 10 поступают через преобразователь 7 кода на индикатор 8. 2 з.п. ф-лы, 6 ил.

Фиг. 2

Фке.З

Фиг. 4

2

/

Фиг. 5

Фиг. 6

| Патент США № 3668624, кл | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

| Устройство для регистрации превышения транспортным средством разрешенной скорости движения | 1985 |

|

SU1309072A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

Авторы

Даты

1991-08-30—Публикация

1989-07-24—Подача