Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения различных устройств передачи и переработки дискретной информации.

Целью изобретения является повышение быстродействия.

На фиг. 1 представлена схема устройства для формирования вычета по произвольному модулю от числа; на фиг. 2 - схема первого вычитающего счетчика; на фиг. 3 - схема второго вычитающего счетчика.

Устройство для формирования вычета по произвольному модулю от числа (фиг, 1) содержит генератор 1 тактовых импульсов, блок 2 синхронизации, первый триггер 3, первый элемент И 4, вычитающий счетчик 5 по модулю, первый элемент ИЛИ 6, делитель 7, третий элемент И 8, второй триггер 9, четвертый элемент И 10, второй вычитающий счетчик 11, суммирующий счетчик 12 по модулю, второй элемент И 13, первый вычитающий счетчик 14, второй элемент ИЛИ 15, пятый элемент И 16, информационный вход 17, вход 18 запуска, вход 19 константы, вход 20 модуля, вход 21 начальной установки и выход 22.

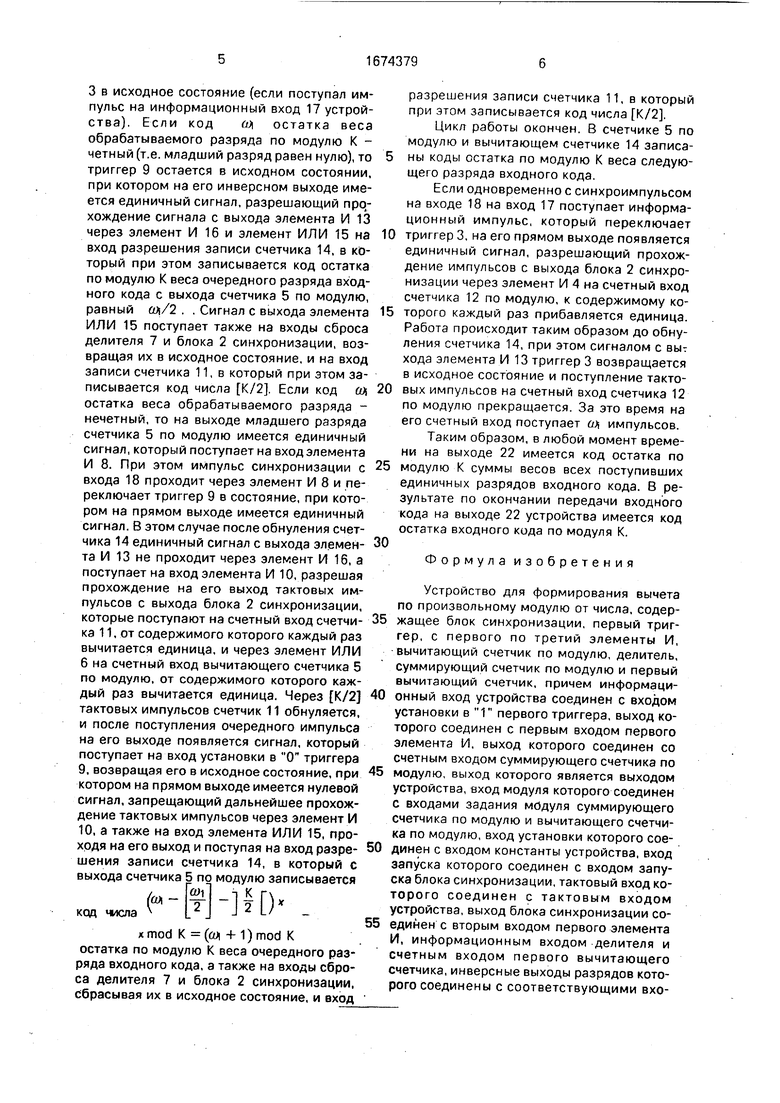

Первый вычитающий счетчик 14 (фиг. 2) содержит элемент И 23, элемент ИЛИ 24, узел 25 двоичного счета, группу элементов И 26, счетный вход 27, инверсные выходы 28 разрядов выхода счетчика 14, информационный вход 29 и вход 30 разрешения записи, причем входы разрядов входа 29 соединены с первыми входами соответствующих элементов И 26, выходы которых сое- динены с входами разрядов информационного входа узла 25 двоичного счета, прямые выходы разрядов выхода которого соединены с соответствующими входами элемента ИЛИ 24, выход которого и вход 27 соединены соответственно с входами элемента И 23, выход которого соединен с вычитающим входом узла 25 двоичного счета, инверсные выходы разрядов выхода которого являются выходами 28 счетчика 14, вход 30 которого соединен с вторыми входами элементов И 26 группы.

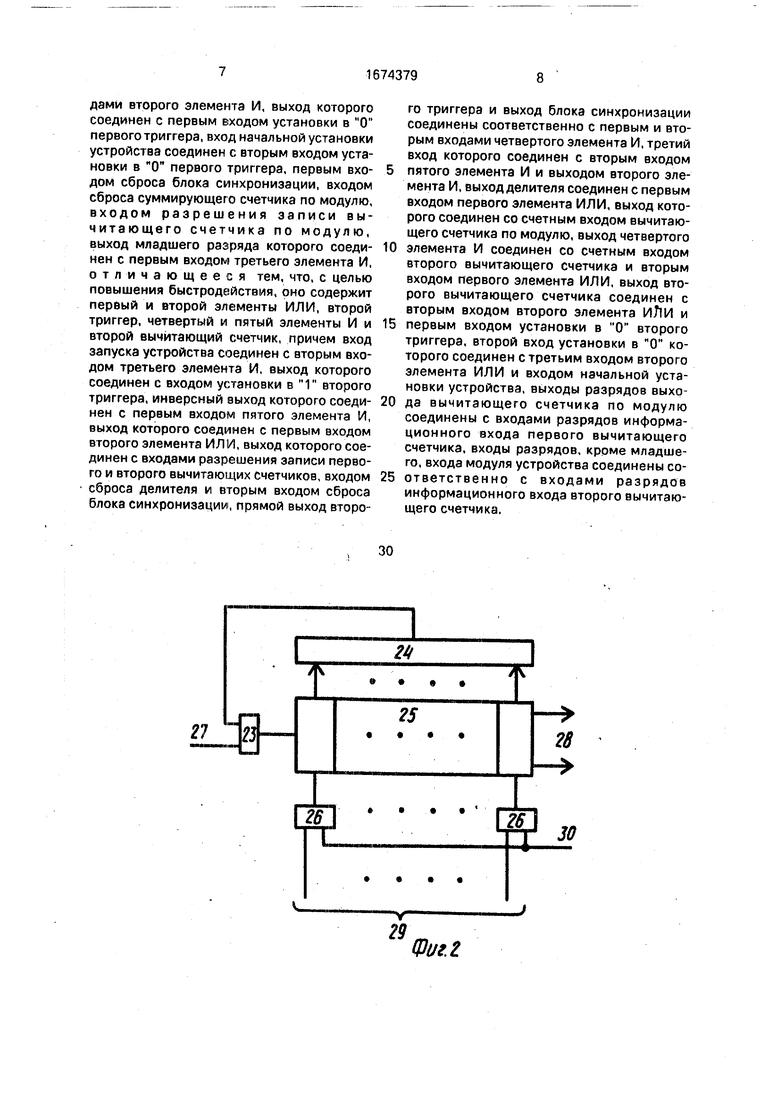

Второй вычитающий счетчик 11 (фиг. 3) содержит элемент И 31, группу элементов И 32, узел 33 двоичного счета, счетный вход 34, выход 35, информационный вход 36 и вход 37 разрешения записи, причем входы разрядов входа 36 соединены с первыми входами соответствующих элементов И 32 группы, выходы которых соединены с входами разрядов информационного входа узла 33 двоичного счета, инверсные выходы разрядов выхода которого и счетный вход 34 счетчика 11 соединены с входами элемента

И 31, выход которого является выходом счетчика 11, счетный вход 34 которого соединен с вычитающим входом узла 33 двоичного счета, вход 37 соединен с вторыми входами элементов И 32 группы.

Блок 2 синхронизации реализован и функционирует так, как прототип.

Счетчики 5 и 12 по модулю реализованы и функционируют так же, как и соответству- 0 ющие счетчики в прототипе.

Делитель 7 представляет собой счетный триггер, имеющий выход переноса,

Разрядность счетчиков 12, 14 и 5 выбирается равНОЙ t lOQ2 Кмакс ДВОИЧНЫХ

5 разрядов, а разрядность вычитающего счетчика 11 равна (t-1), где Кмакс максимальное значение модуля.

Устройство (фиг. 1) работает следующим образом.

0 На вход 19 устройства подается код остатка старшего разряда по модулю К, на вход 20 - код модуля К, а на вход 21 - сигнал сброса. При этом триггеры 3 и 9 сбрасываются в состояние, при котором на их прямых

5 выходах имеется нулевой сигнал. Блок 2 синхронизации устанавливается в состояние, при котором он не пропускает тактовых импульсов. Счетчик 12 по модулю и делитель 7 сбрасываются в нулевое состояние. В

0 счетчик 5 по модулю и в вычитающий счетчик 14 записывается код остатка старшего разряда входного кода по модулю К, а в вычитающий счетчик 11 - код числа К/2 (код модуля К без младшего разряда).

5 Далее на вход 18 подаются синхроимпульсы, а на вход 17 - разряды входного кода (последовательно синхронно с синхроимпульсами).

При поступлении синхроимпульса он

0 запускает блок 2 синхронизации, который начинает пропускать тактовые импульсы с выхода генератора 1 на свой выход (при этом, если тактовый импульс совпадает с синхроимпульсом, он на выход блока 2 син5 хронизации не проходит, что исключает возможность неправильного срабатывания устройства). Импульсы с выхода блока 2 синхронизации поступают на счетный вход вычитающего счетчика 14, от содержимого

0 которого каждый раз вычитается единица, и на информационный вход делителя 7 с коэффициентом деления, равным двум. Импульсы с выхода делителя 7 поступают через элемент ИЛИ 6 на счетный вход счетчика 5

5 по модулю, от содержимого которого каждый раз вычитается единица. Работа продолжается таким образом до обнуления счетчика 14, при этом на выходе элемента И 13 появляется (в паузе между тактовыми импульсами) сигнал, переключающий триггер

3 в исходное состояние (если поступал импульс на информационный вход 17 устройства). Если код (ft остатка веса обрабатываемого разряда по модулю К - четный (т.е. младший разряд равен нулю), то триггер 9 остается в исходном состоянии, при котором на его инверсном выходе имеется единичный сигнал, разрешающий прохождение сигнала с выхода элемента И 13 через элемент И 16 и элемент ИЛИ 15 на вход разрешения записи счетчика 14, в который при этом записывается код остатка по модулю К веса очередного разряда входного кода с выхода счетчика 5 по модулю, равный (ft/2 . . Сигнал с выхода элемента ИЛИ 15 поступает также на входы сброса делителя 7 и блока 2 синхронизации, возвращая их в исходное состояние, и на вход записи счетчика 11, в который при этом записывается код числа К/2. Если код (ft остатка веса обрабатываемого разряда - нечетный, то на выходе младшего разряда счетчика 5 по модулю имеется единичнми сигнал, который поступает на вход элемента И 8. При этом импульс синхронизации с входа 18 проходит через элемент И 8 и переключает триггер 9 в состояние, при кото ром на прямом выходе имеется единичный сигнал, В этом случае после обнуления счетчика 14 единичный сигнал с выхода элемента И 13 не проходит через элемент И 16, а поступает на вход элемента И 10, разрешая прохождение на его выход тактовых импульсов с выхода блока 2 синхронизации, которые поступают на счетный вход счетчика 11, от содержимого которого каждый раз вычитается единица, и через элемент ИЛИ 6 на счетный вход вычитающего счетчика 5 по модулю, от содержимого которого каждый раз вычитается единица. Через К/2 тактовых импульсов счетчик 11 обнуляется, и после поступления очередного импульса на его выходе появляется сигнал, который поступает на вход установки в О триггера

9,возвращая его в исходное состояние, при котором на прямом выходе имеется нулевой сигнал, запрещающий дальнейшее прохождение тактовых импульсов через элемент И

10,а также на вход элемента ИЛИ 15, проходя на его выход и поступая на вход разрешения записи счетчика 14, в который с выхода счетчика 5 по модулю записывается

)код числа

ж mod К ((ft + 1) mod К остатка по модулю К веса очередного разряда входного кода, а также на входы сброса делителя 7 и блока 2 синхронизации, сбрасывая их в исходное состояние, и вход

разрешения записи счетчика 11, в который при этом записывается код числа К/2.

Цикл работы окончен. В счетчике 5 по модулю и вычитающем счетчике 14 записа- 5 ны коды остатка по модулю К веса следующего разряда входного кода.

Если одновременно с синхроимпульсом на входе 18 на вход 17 поступает информационный импульс, который переключает

10 триггер 3, на его прямом выходе появляется единичный сигнал, разрешающий прохождение импульсов с выхода блока 2 синхронизации через элемент И 4 на счетный вход счетчика 12 по модулю, к содержимому ко5 торого каждый раз прибавляется единица. Работа происходит таким образом до обнуления счетчика 14, при этом сигналом с вы хода элемента И 13 триггер 3 возвращается в исходное состояние и поступление такто0 вых импульсов на счетный вход счетчика 12 по модулю прекращается. За это время на его счетный вход поступает (ft импульсов. Таким образом, в любой момент времени на выходе 22 имеется код остатка по

5 модулю К суммы весов всех поступивших единичных разрядов входного кода. В результате по окончании передачи входного кода на выходе 22 устройства имеется код остатка входного кода по модуля К.

0

Формула изобретения

Устройство для формирования вычета по произвольному модулю от числа, содер5 жащее блок синхронизации, первый триггер, с первого по третий элементы И, вычитающий счетчик по модулю, делитель, суммирующий счетчик по модулю и первый вычитающий счетчик, причем информаци0 онный вход устройства соединен с входом установки в 1 первого триггера, выход которого соединен с первым входом первого элемента И, выход которого соединен со счетным входом суммирующего счетчика по

5 модулю, выход которого является выходом устройства, вход модуля которого соединен с входами задания модуля суммирующего счетчика по модулю и вычитающего счетчика по модулю, вход установки которого сое0 динен с входом константы устройства, вход запуска которого соединен с входом запуска блока синхронизации, тактовый вход ко- торого соединен с тактовым входом устройства, выход блока синхронизации со5 единен с вторым входом первого элемента И, информационным входом делителя и счетным входом первого вычитающего счетчика, инверсные выходы разрядов которого соединены с соответствующими входами второго элемента И, выход которого соединен с первым входом установки в О первого триггера, вход начальной установки устройства соединен с вторым входом установки в О первого триггера, первым входом сброса блока синхронизации, входом сброса суммирующего счетчика по модулю, входом разрешения записи вычитающего счетчика по модулю, выход младшего разряда которого соединен с первым входом третьего элемента И, отличающееся тем, что, с целью повышения быстродействия, оно содержит первый и второй элементы ИЛИ, второй триггер, четвертый и пятый элементы И и второй вычитающий счетчик, причем вход запуска устройства соединен с вторым входом третьего элемента И, выход которого соединен с входом установки в 1 второго триггера, инверсный выход которого соединен с первым входом пятого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с входами разрешения записи первого и второго вычитающих счетчиков, входом сброса делителя и вторым входом сброса блока синхронизации, прямой выход второго триггера и выход блока синхронизации соединены соответственно с первым и вторым входами четвертого элемента И, третий вход которого соединен с вторым входом

пятого элемента И и выходом второго элемента И, выход делителя соединен с первым входом первого элемента ИЛИ, выход которого соединен со счетным входом вычитающего счетчика по модулю, выход четвертого

элемента И соединен со счетным входом второго вычитающего счетчика и вторым входом первого элемента ИЛИ, выход второго вычитающего счетчика соединен с вторым входом второго элемента ИЛИ и

первым входом установки в О второго триггера, второй вход установки в О которого соединен с третьим входом второго элемента ИЛИ и входом начальной установки устройства, выходы разрядов выхода вычитающего счетчика по модулю соединены с входами разрядов информационного входа первого вычитающего счетчика, входы разрядов, кроме младшего, входа модуля устройства соединены соответственно с входами разрядов информационного входа второго вычитающего счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для подсчета числа единиц двоичного кода по модулю К | 1986 |

|

SU1427574A1 |

| Устройство для формирования остатка по модулю от числа | 1988 |

|

SU1575186A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587642A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587641A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2202121C2 |

| Устройство для передачи информации | 1989 |

|

SU1700571A1 |

| Устройство для подсчета числа единиц двоичного кода по модулю К | 1986 |

|

SU1438006A1 |

| Устройство поэлементной синхронизации | 1987 |

|

SU1517142A1 |

| Устройство для измерения средней частоты импульсов нестационарного случайного потока | 1982 |

|

SU1049819A1 |

| Устройство для контроля устройства микропрограммного управления | 1988 |

|

SU1608674A1 |

Изобретение относится к области вычислительной техники и может быть использовано для построения различных устройств передачи и переработки дискретной информации. Цель изобретения - повышение быстродействия. Устройство для формирования вычета по произвольному модулю от числа содержит блок 2 синхронизации, триггеры 3 и 9, элементы И 10, 4, 8, 13 и 16, вычитающий счетчик 5 по модулю, суммирующий счетчик 12 по модулю, элементы ИЛИ 6 и 15, делитель 7, вычитающие счетчики 11 и 14 со связями. Введение второго вычитающего счетчика 11, триггера 9, элементов И 10 и 16 позволяет формировать остаток веса следующего разряда по модулю K в случае нечетного значения остатка веса поступившего разряда не путем его суммирования с модулем K и последующего пересчета с делением на два, а путем корректировки результата пересчета остатка веса разряда на K/2, что сокращает цикл работы устройства на K/2 тактов. 3 ил.

21 ПЯ

28

30

29

Фиг. Z

31

У J

М

JJ

пл

36

35

J7

| Авторское свидетельство СССР № 1488967, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для формирования вычета последовательного двоичного кода по модулю | 1988 |

|

SU1571771A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-08-30—Публикация

1989-08-22—Подача