4

ю ел

liu

Изобретение относится к вычислительной технике и может быть использовано в системах передачи и обработки дискретной информации.

Цель изобретения г Ф сширение функциональных возможностей за счет формирования остатка по модулю К от входного кода.

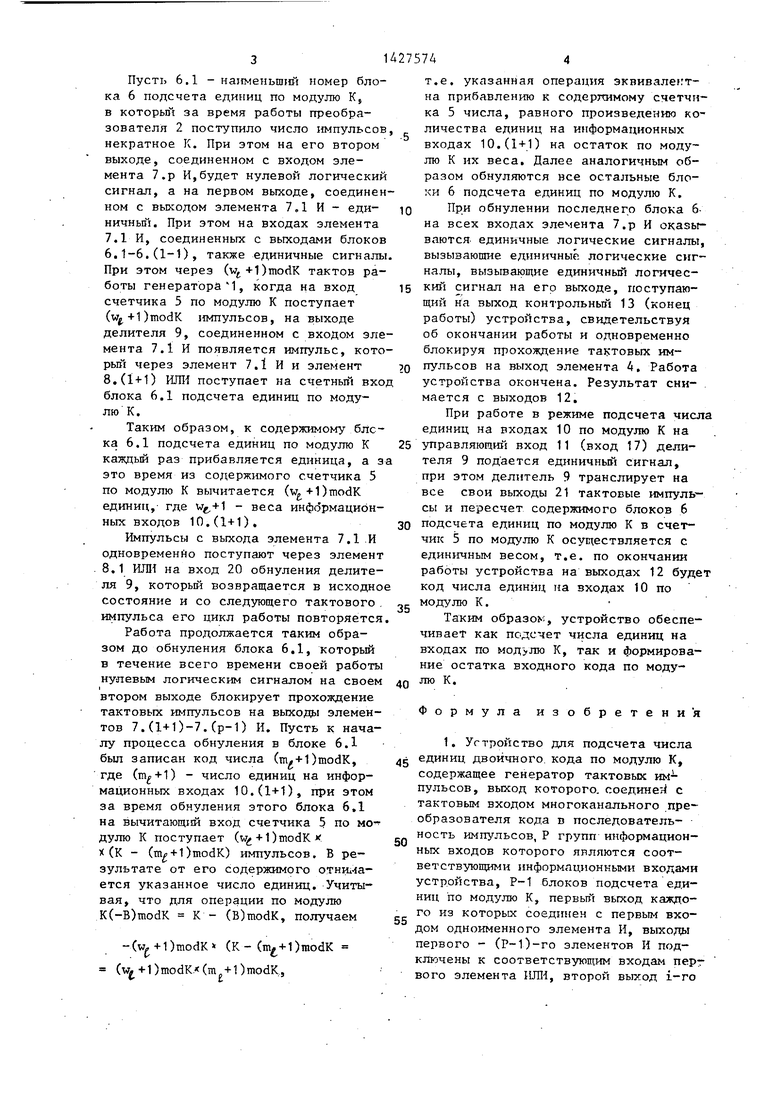

На фиг.1 изображена функциональная схема устройства; на фиг.2 - выполнение делителя частоты.

Устройство для подсчета числа единиц двоичного кода по модулю содержит генератор 1 тактовых импульсов, многоканальньй преобразователь 2 параллельного кода в последовательность импульсов, триггер 3, элемент 4 ЗАПРЕТ, счетчик 5 по модулю К, блоки 6 подсчета единиц по .модулю К, элементы 7 И, элементы 8 ИЛИ и делитель 9 частоты. На фиг.1 обозначен информационные и управляющий входы 1 и 11, информационные и контрольный выходы 12 и 13.

Многоканальный преобразователь 2 параллельного кода в последовательность импульсов может быть выполнен так же, как и в прототипе. Входы 10 преобразователя 2 сгруппированы таким образом, что веса всех разрядов одной группы входов, взятые по модулю К, одинаковы, а для первой группы входов равны 1.

Блок 6 подсчета единиц по модулю К включает в себя счетчик по модулю К, выходы которого соединены со входами элемента ИШ1, прямой и инверсный выходы которого являются первым и вторым выходами блока 6.

Делитель 9- частоты выполнен (фиг.2) на распределителе 14 импульсов, элементах 15 И, элементах 16 ИЛИ. На фиг.2 обозначены управляющий и тактовый входы 17 и 18, входы 19 и 20 синхронизации и обнуления и выход 21. При этом i-ый выход.делителя 9 (1 ) соединенный с входом i-ro элемента 7 И, соответствует коэффициенту деления, равному вёйу по модулю К (1+1)-ой группы информационных входов 10.

Устройство для подсчета числа единиц двоичного кода по модулю К работает следующим образом.

В исходном состоянии блоки 6 подсчета единиц по модулю К, счетчик 5 по модулю К, триггер 3, делитель 9 частоты и многоканальный пре0

5

0

5

0

5

0

5

0

5

образователь 2 параллельного кода в последовательный сброшены (цепи начального обнуления не показаны). На выходе триггера 3 - нулевой логический сигнал, блокирующий работу делителя 9 и прохождение импульсов на выход элемента 4 ЗАПРЕТ.

Контролируемый код подан на информационные входы 10 преобразователя 2.

При поступлении тактовых импульсов с выхода генератора 1 на тактовый вход многоканального преобразователя 2 последний преобразует параллельный код на входах 10 в последовательность импульсов информационном выходе (т 1,р).

Импульсы с (i+1)-ro информационного выхода поступают через элемент 8.(i+1) ИЛИ на счетный вход блока 6 подсчета единиц по модулю К, а с первого выхода преобразователя 2 - на суммирующий вход счетчика 5 по модулю К. Блоки 6 и счетчик 5 осуществляют подсчет поступающих на их входы импульсов по модулю К. По окончании преобразования входного кода многоканальный преобразователь 2 самоблокируется и далее импульсов на информационных выходах не формирует, при этом на его управляющем выходе (конца работы) появляется сигнал, переключающий триггер 3, на выходе которого при этом появляется единичный логический сигнал (в паузе между тактовыми импульсами).

К этому моменту времени в счетчике 5 по модулю К и блоках 6 подсчета единиц по модулю К оказывается записан код остатка по модулю К единичных сигналов на входах 10.

Далее происходит процесс последо- вательного обнуления блокоя 6 и пересчет их содержимого (с учетом остатков по модулю К весов соответствующих входов 10 при работе в режиме формирования остатка числа)в счетчик 5 по модулю К.

Пусть устройство работает в режиме формирования остатка числа по модулю К. При этом на управляющий вход 11 (вход 17 делителя 9) подается нулевой сигнал. При этом тактовые импульсы с выхода генератора. 1 тактовых импульсов поступают через элемент 4 на вход счетчика 5, а также на тактовый вход делителя 9.

числа соответствующих

Пусть 6.1 - наименьший номер блока 6 подсчета едиггиц по модулю К, в KOTopbDi за время работы преобразователя 2 поступило число импульсов, некратное К. При этом на его втором выходе, соединенном с входом элемента 7.р И,будет нулевой логический сигнал, а на первом выходе, соединенном с выходом элемента 7 Л И - еди- ничньш. При этом на входах элемента 7,1 И, соединенных с выходами блоков 6,1-6.(1-1), также единичные сигналы. При этом через (wj+1)modK тактов работы генераторам, когда на вход счетчика 5 по модулю К поступает (W(+1)modK импульсов, на выходе делителя 9, соединенном с входом элемента 7.1 И появляется импульс, кото- рьпг через элемент 7.1 И и элемент 8.(1+1) ИЛИ поступает на счетньш вход блока 6.1 подсчета единиц по модулю К .

Таким образом, к содержимому блока 6.1 подсчета единиц по модулю К каждый раз прибавляется единица, а за это время из содержимого счетчика 5 по модулю К вычитается ( 1) modK единиц, где .-i-1 - веса информационных входов 10, (1+1),

Импульсы с выхода элемента 7.1.И одновременно поступают через элемент 8,1 ИЛИ на вход 20 обнуления делителя 9, который возвращается в исходное состояние и со следующего тактового . импульса его цикл работы повторяется.

Работа продолжается таким образом до обнуления блока 6.1, который в течение всего времени своей работы нулевым логическим сигналом на своём втором выходе блокирует прохождение тактовых импульсов на выходы элементов 7, (1+1)-7.(р-1) И, Пусть к началу процесса обнуления в блоке 6.1 был записан код числа (m.+1)modK, где () - число единиц на информационных входах 10.(1+1), при этом за время обнуления этого блока 6.1 на вычитающий вход счетчика 5 по мо- дулю К поступает (w + 1)modKx X(к - (m/+1)modK) импульсов. В результате от его содержимого oTHit-ia- ется указанное число единиц. Учитывая, что для операции по модулю K(-B)tnodK К - (B)modK, получаем

-(wv+1)modK (К- ()modK (w, +1)modK.«(m+1) modK,

0

5

T,e. указанная операция эквивале гт- на прибавлению к содергсимому счетчика 5 числа, равного произведению количества единиц на информационных входах 10.(1+1) на остаток по модулю К их веса. Далее аналогичным образом обнуляются нее остальные блоки 6 подсчета единиц по модулю К,

При обнулении последнего блока 6- на всех входах элемента 7,р И оказываются единичные логические сигналы, вызывающие единичные логические ciri- налы, вызывающие единичньп логический сигнал на его выходе, поступающий на выход контрольньш 13 (конец работы) устройства, свидетельствуя об окончании работы и одновременно блокируя прохождение тактовых импульсов на выход элемента 4, Работа устройства окончена. Результат снимается с выходов 12,

При работе в режиме подсчета числа единиц на входах 10 по модулю К на 5 управляющий вход 11 (вход 17) делителя 9 подается единичный сигнал, при этом делитель 9 транслирует на все свои выходы 21 тактовые импульсы и пересчет содержимого блоков 6 подсчета единиц по модулю К в счетчик 5 по модулю К осуществляется с един гчным весом, т,е. по окончании работы устройства на выходах 12 будет код числа единиц на входах 10 по модулю к.

Таким образок:, устройство обеспечивает как подсчет числа единиц на входах по К, так и формирование остатка входного кода по модулю К,

0

5

0

Формула изобретения

1, Устройство для подсчета числа единиц двоичного, кода по модулю К, содержащее генератор тактовых импульсов, выход которого, соединет с тактовым входом многоканального преобразователя кода в последовательность импульсов, Р групп информационных входов которого являются соответствующими информационными входами устройства, Р-1 блоков подсчета единиц по модулю К, первьш выход каждого из которых соединен с первым входом одноименного элемента И, выходы первого - (р-1)-го элементов И подключены к соответствующим входам перг вого элемента ИЛИ, второй выход i-го

блока подсчета единиц по модулю К (i 1,Р-1) соединен с соответствую- .щим входом Р-го элемента И и (i+1)-M входом j-ro элемента И (), управляющий выход многоканального преобразователя параллельного кода в Последовательность импульсов подклю- |чен к входу триггера, выход которого соединен с Р-м входом Р-го элемента И, выход которого является контрольным выходом устройства, счетчик по модулю К, выходы которого являются информационными выходами устройс тва, отличающееся тем, что, с целью расширения функциональных возможностей за счет формирования остатка по модулю к от входного кода, в устройство введены делитель частоты, второй - Р-й элементы ИЛИ и ЗАПРЕТ, запрещающий вход которого подключен к выходу Р-го элемента И, ЬЬ1ход элемента ЗАПРЕТ соединен с вычитающим входом счетчика по модулю К, первый - Р-й информационные выходы многоканального преобразователя параллельного кода в последовательность импульсов соединены соответственно с суммирующим входом счетчика по модулю К и первыми входами второго - Р-го элементов ИЛИ, второй вход и выход (i+l)-ro элемента ИЛИ подключены соответственно к выходу i-ro элемента И и входу i-ro блока под1Д275746

обнуления делителя частоты, тактовый вход и вход синхронизации которого объединены соответственно с первым и вторым разрешающими входами элемента ЗАПРЕТ и подключены к выходам соответственно генератора тактовых импульсов и триггера, i-й выход делителя частоты подключен к (1+1)-му 10 входу i-ro элемента И, управляющий вход делителя частоты является управляющим входом устройства.

15

20

25

30

2, Устройство по п.1, о т л и - чающееся тем, что делитель частоты выполнен на элементах И, о элементах ИЛИ и распределителе импульсов, вход обнуления которого является входом обнуления делителя, первьш и второй входы первого и первый вход второго элементов И являются соответственно тактовым входом, входом синхронизации и управляющим входом делителя, выходы распределителя импульсов соединены с первыми входами соответственно первого - (Р-2)-го элементов 11ПИ, выход первого элемента И подключен к тактовому входу распределителя импульсов, второму входу второго элемента И и является первым выходом делителя, выход второго элемента И подключен к вторым входам первого - (Р-2)-го элементов ИЛИ, выходы которых яв-

счета единиц по модулю К, выход пер- ляются соответственно вторым - (Р-1)-м

вого элемента ИЛИ соединен с входом

выходами делителя.

5

0

5

0

2, Устройство по п.1, о т л и - чающееся тем, что делитель частоты выполнен на элементах И, о элементах ИЛИ и распределителе импульсов, вход обнуления которого является входом обнуления делителя, первьш и второй входы первого и первый вход второго элементов И являются соответственно тактовым входом, входом синхронизации и управляющим входом делителя, выходы распределителя импульсов соединены с первыми входами соответственно первого - (Р-2)-го элементов 11ПИ, выход первого элемента И подключен к тактовому входу распределителя импульсов, второму входу второго элемента И и является первым выходом делителя, выход второго элемента И подключен к вторым входам первого - (Р-2)-го элементов ИЛИ, выходы которых яв-

ляются соответстве

выходами делителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля количества единиц двоичного кода по модулю К | 1986 |

|

SU1401461A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587642A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587641A1 |

| Устройство для подсчета числа единиц двоичного кода по модулю К | 1986 |

|

SU1438006A1 |

| Устройство для контроля двоичного кода по модулю К | 1990 |

|

SU1737736A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАЛЛЕЛЬНОГО ДВОИЧНОГО КОДА ПО МОДУЛЮ K | 1991 |

|

RU2020760C1 |

| Устройство для преобразования двоичного кода в код по модулю К | 1987 |

|

SU1492479A1 |

| Устройство для подсчета числа единиц двоичного кода | 1987 |

|

SU1569995A1 |

| Устройство для контроля равновесного кода | 1987 |

|

SU1580563A1 |

| Устройство для контроля количества единиц двоичного кода по модулю К | 1986 |

|

SU1401464A2 |

Изобретение относится к вычислительной технике. Его использование в системах обработки и передачи дискретной информации позволяет расширить функциональные возможности устройства па счет формирования остатка по модулю К от входного кода. Устройство содержит генератор 1 тактовых импульсов, многоканальньп преобразователь 2 параллельного кода в последовательность импульсов, триггер 3, счетчик 5 по модулю К, Р-1 блоков 6 подсчета единиц по модулю К, Р элементов И 7 и элемент ИЛИ 8.1. Благодаря введению элемента 4 ЗАПРЕТ, элементов HJBi 8.2-8.Р и делителя 9 частоты в устройстве формируется остаток по модулю К от вход,- ного кода и определяется число единиц кода по тому же модулю. 1 з.п. ф-лы, 2 ил. ( W

л

ПО

JtL

18

19

20

7

. 2

| Устройство для контроля параллельного двоичного кода на четность | 1974 |

|

SU530332A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь двоичного кода в последовательность импульсов | 1983 |

|

SU1277115A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-30—Публикация

1986-12-02—Подача