Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах ЭВМ.

Целью изобретения является уменьшение площади, занимаемой на кристалле, и повышение быстродействия блока формирования переноса.

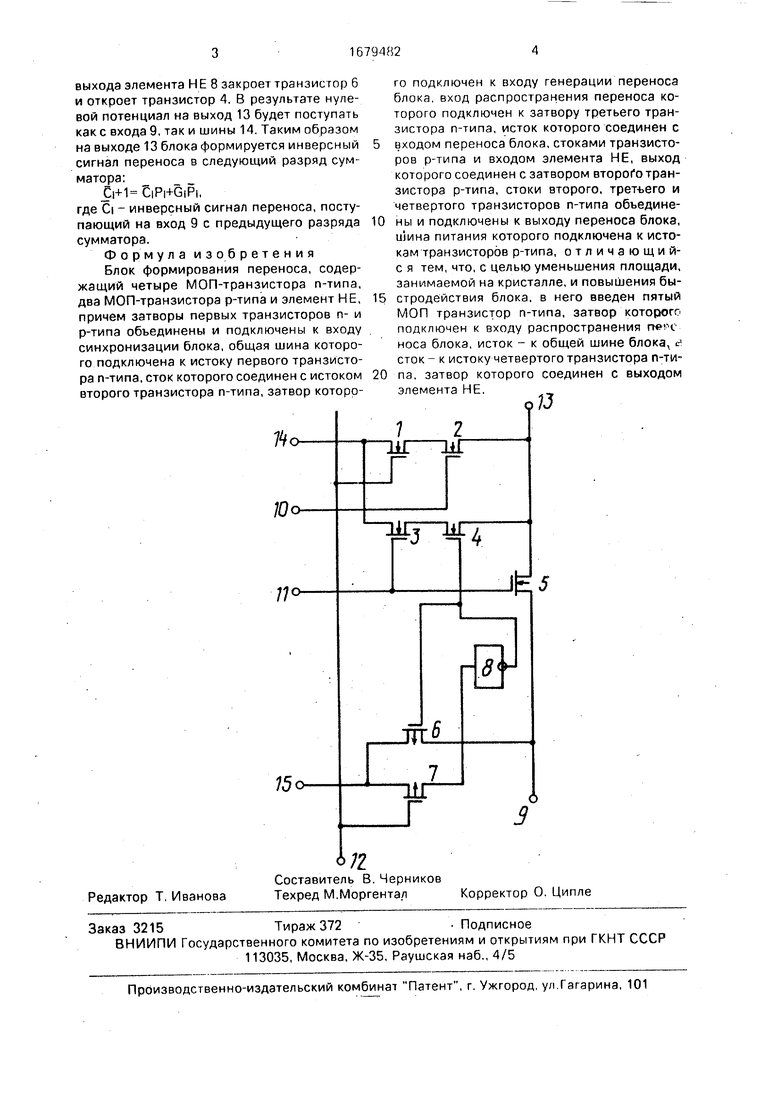

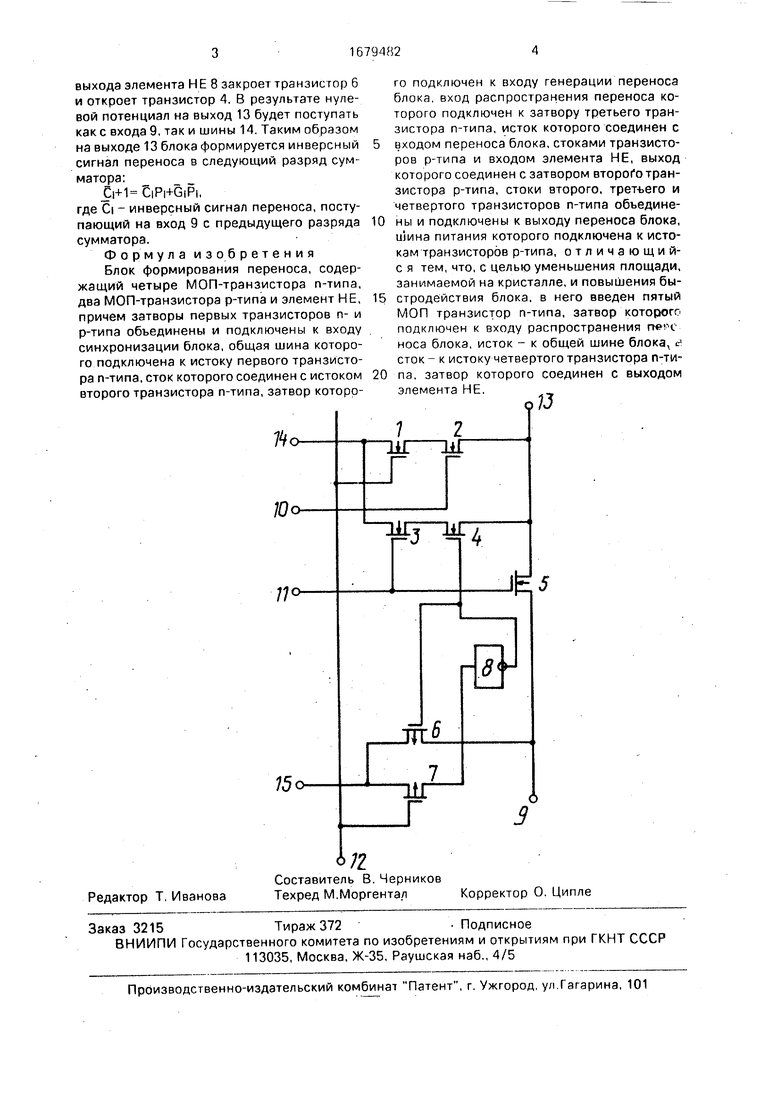

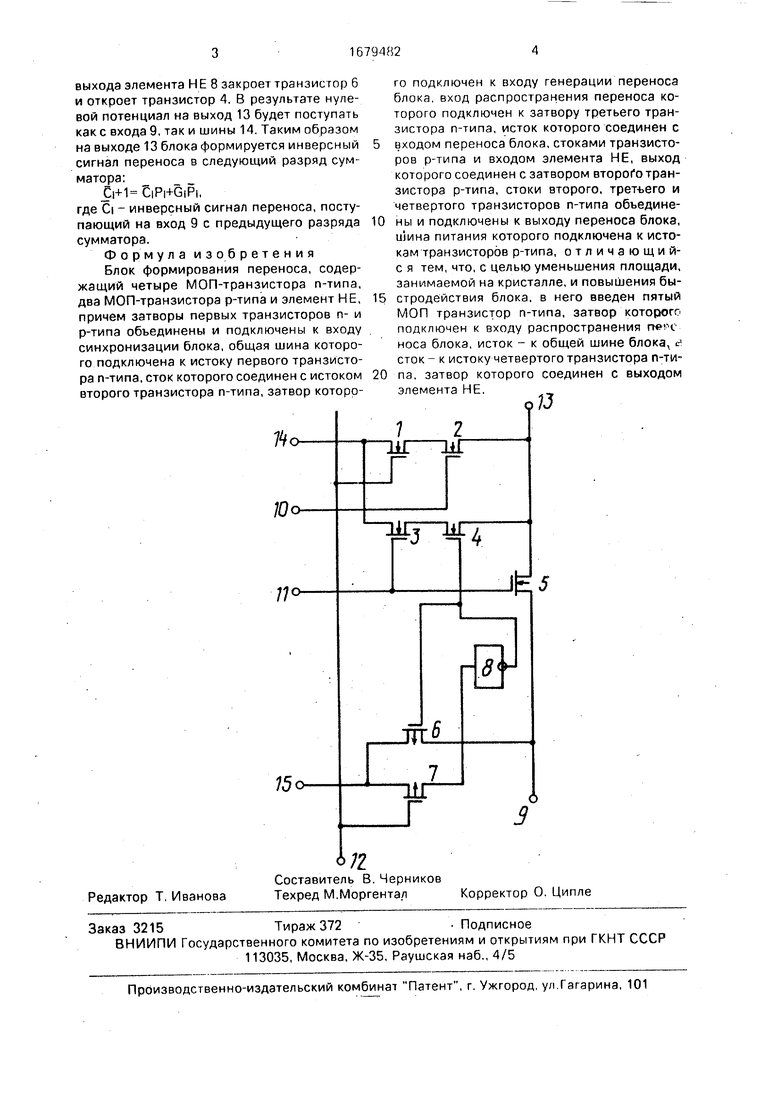

На чертеже приведена схема блока формирования переноса.

Блок формирования переноса содержит МОП-транзисторы п-типа 1-5 и р-типа 6, 7, элемент НЕ 8, имеет входы переноса 9, генерации переноса 10, распространения переноса 11 и синхронизации 12, выход переноса 13, подключен к общей шине 14 и шине питания 15.

Блок работает следующим образом.

В исходном состоянии на вход синхронизации 12 подается нулевой сигнал. При этом закрывается транзистор 1 и открывается транзистор 7. Единичный потенциал с шины 15 поступает на вход элемента НЕ 8 и вход 9 данного блока. Нулевой сигнал с выхода элемента НЕ 8 закрывает транзистор 4 и открывает транзистор 6. В результате на выходе переноса 13 блока переноса предыдущего разряда арифметического устройства, который подключен к входу переноса 9 данного блока, устанавливается единичный потенциал.

В рабочем состоянии на вход 12 подается единичный сигнал, который открывает транзистор 1 и закрывает транзистор 7, а на входы 10 и 11 - сигналы генерации и распространения Pi Xi+Yi переноса, где Х| и YI - i-e разряды входных слагаемых. Если и , то транзисторы 2, 3 и 5 будут закрыты и на выходе переноса 13 останется единичный потенциал, так как открыт транзистор 6 блока переноса предыдущего разряда. Если и , то транзисторы 3 и 5 будут закрыты, но откроется транзистор 2, и нулевой потенциал с шины 14 поступит на выход 13. Если и , то транзистор 2 будет закрыт, но откроются транзисторы 3 и 5, и сигнал с входа 9 поступит на выход 13, Сопротивление открытого транзистора 6 значительно меньше сопротивления открытых транзисторов п-типа 1-5. Поэтому при подаче на вход 9 нулевого сигнала на входе элемента НЕ 8 установится потенциал, близкий к нулевому, и единичный сигнал с

СП

С

о ч чэ

со ю

выхода элемента НЕ 8 закроет транзистор 6 и откроет транзистор 4. В результате нулевой потенциал на выход 13 будет поступать как с входа 9, так и шины 14. Таким образом на выходе 13 блока формируется инверсный сигнал переноса в следующий разряд сумматора:

Ci+1 CiP|-K3iPi,

где Ci - инверсный сигнал переноса, поступающий на вход 9 с предыдущего разряда сумматора.

Формула изобретения Блок формирования переноса, содержащий четыре МОП-транзистора п-типа, два МОП-транзистора р-типа и элемент НЕ, причем затворы первых транзисторов п- и р-типа объединены и подключены к входу синхронизации блока, общая шина которого подключена к истоку первого транзистора n-типа, сток которого соединен с истоком второго транзистора n-типа, затвор которо#0го подключен к входу генерации переноса блока, вход распространения переноса которого подключен к затвору третьего транзистора n-типа, исток которого соединен с

входом переноса блока, стоками транзисторов р-типа и входом элемента НЕ, выход которого соединен с затвором второго транзистора р-типа, стоки второго, третьего и четвертого транзисторов n-типа обьединены и подключены к выходу переноса блока, шина питания которого подключена к истокам транзисторов р-типа, отличающий- с я тем, что, с целью уменьшения площади, занимаемой на кристалле, и повышения быстродействия блока, в него введен пятый МОП транзистор n-типа, затвор которого подключен к входу распространения носа блока, исток - к общей шине блока, с1 сток - к истоку четвертого транзистора п-типа, затвор которого соединен с выходом элемента НЕ.

97J

1 2

ЯЖ

| название | год | авторы | номер документа |

|---|---|---|---|

| Схема формирования переносов сумматора | 1988 |

|

SU1624443A1 |

| Блок формирования сквозного переноса в сумматоре | 1979 |

|

SU1042012A1 |

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2021 |

|

RU2762061C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ВОССТАНОВЛЕНИЯ МОДИФИЦИРОВАННОГО КОДА ХЕММИНГА ДЛЯ 16-РАЗРЯДНЫХ ДВОИЧНЫХ ЧИСЕЛ | 2024 |

|

RU2824472C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ВОССТАНОВЛЕНИЯ МОДИФИЦИРОВАННОГО КОДА ХЕММИНГА ДЛЯ 32-РАЗРЯДНЫХ ДВОИЧНЫХ ЧИСЕЛ | 2023 |

|

RU2800768C1 |

| Формирователь переноса | 1990 |

|

SU1702361A1 |

| Блок формирования переноса сумматора | 1989 |

|

SU1718214A1 |

| Динамическая программируемая логическая матрица | 1989 |

|

SU1635217A1 |

| СУММАТОР | 1994 |

|

RU2049346C1 |

| Комбинационный сумматор | 1988 |

|

SU1596321A1 |

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах ЭВМ. Цель изобретения - уменьшение площади, занимаемой на кристалле, и повышение быстродействия. Блок формирования переноса содержит шину 15 питания, общую шину 14, вход 11 распространения переноса, вход 10 генерации переноса, входы 9 переноса, выход 13 переноса, вход 12 синхронизации, пять МОП-транзисторов 1-5 n-типа, два МОП- транзистора 6, 7 р-типа и элемент НЕ 8. 1 ил.

Ms

JTtl

| Патент США № 4016546, кл.С06Р7/50, 1977 | |||

| Патент США №4471455, кл.СОб F7/50, 1984 |

Авторы

Даты

1991-09-23—Публикация

1989-01-03—Подача