Изобретение относится к вычислительной технике и может быть использовано при построении арифметических цифровых устройств на КМДП-транзисторах, в частности многоразрядных параллельных суммато- ров-вычитателей и схем сравнения.

Известен узел формирования переноса в сумматоре, два разряда которого содержат три МДП-транзистора р-типа, три МДП- транзистора n-типа, четыре элемента НЕ, два элемента И-НЕ, два элемента ИЛИ-НЕ.

Недостатком такого устройства является невысокое быстродействие в режиме передачи сквозного переноса, вызванное последовательным прохождением сигнала переноса через каждый разряд узла.

Наиболее близким по технической сущности к предлагаемому является формирователь переноса, содержащий в каждом разряде по три МДП-транзистора р- и п-ти- па, элемент И-НЕ. элемент ИЛИ-НЕ.

Недостатком такого устройства также является невысокое быстродействие в режиме передачи сквозного переноса, вызванное последовательным прохождением сигнала переноса через каждый разряд формирователя.

Цель изобретения - повышение быстродействия.

Поставленная цель достигается тем. что в формирователь переноса, каждый разряд которого содержит элемент И-НЕ, элемент

X

С N ОС О

ИЛИ-НЕ, три МДП-трэнзистора n-типа и три МДП-транзистора р-типа, причем выход элемента И--НЕ соединен с затворами первых МДП-транэисторов п- и р-типа, выход элемента соединен с затворами вторых МДП-транзисторов n-и р-типа, истоки первого МДП-транзистора р-типа и второго МДП-транзистора n-типа соединены соответственно с шинами питания и нулевого потенциала формирователя, стоки первого МДП-транзистора р-типа и второго МДП-транзистора n-типа образуют выход переноса данного разряда формирователя, ,затворы третьих МДП-транзисторов п- и р- типа соединены с входом переноса данного разряда формирователя, первые и вторые входы элементов ИЛН-НЕ, И-НЕ данного разряда формирователя соединены с входами соответствующих разрядов первого и второго операндов формирователя, введены дополнительно в каждый разряд первый и второй входы управления и четвертые и пятые МДП-транзисторы п- и р-типа, а каждый нечетный разряд формирователя, считая с младшего нулевого, дополнен первым и вторым инверторами, причем в каждом разряде формирователя истоки четвертого и пятого МДП-транзисторов р- типа соединены с шиной питания формирователя, истоки четвертого и пятого МДП-транзисторов n-типа соединены с шиной нулевого потенциала формирователя, затворы четвертых МДП-транзисторов п- и р-типа соединены с первым входом управления данного разряда формирователя, затворы пятых МДП-трзнзисторов п- и р-типа соединены с вторым входом управления данного разряда формирователя, стоки третьего и четвертого МДП-транзисторов р-типз соединены с истоком второго МДП-транзистора р-типа, стоки третьего и пятого МДП-транзисторов n-типа соединены с истоком первого МДП-транзистора n-типа, стоки первого МДП-трэнзистора n-типа м второго МДП- транзистора р-типа соединены с выходом переноса данного разряда формирователя, сток пятого МДП-транзистора р-типа соединен с истоком третьего МДП-транзистора р-типа, сток четвертого МДП-транзистора n-типа соединен с истоком третьего МДП-транзистора n-типа, выходы элементов И-НЕ, ИЛИ-НЕ образуют соответственно первый и второй выходы управления данного разряда формирователя, которые у каждого четного разряда формирователя, считая с младшего нулевого, соединены соответственно с первым и вторым входами управления соседнего более старшего разряда формирователя, а

у каждого нечетного разряда формирователя соединены с входами соответствующих первого и второго инверторов, выходы которых соединены соответственно с вторым и

первым входами управления соседнего более старшего разряда формирователя, выход переноса каждого четного разряда формирователя соединен с входом переноса следующего более старшего четного разряда формирователя, выход переноса каждого нечетного разряда формирователя соединен с входом переноса следующего более старшего нечетного разряда формирователя, у самой младшей пары разрядов

формирователя входы переноса соединены с входом начального переноса формирователя, а первый и второй входы управления самого младшего разряда формирователя соединены соответственно с шинами логической 1 и логического О.

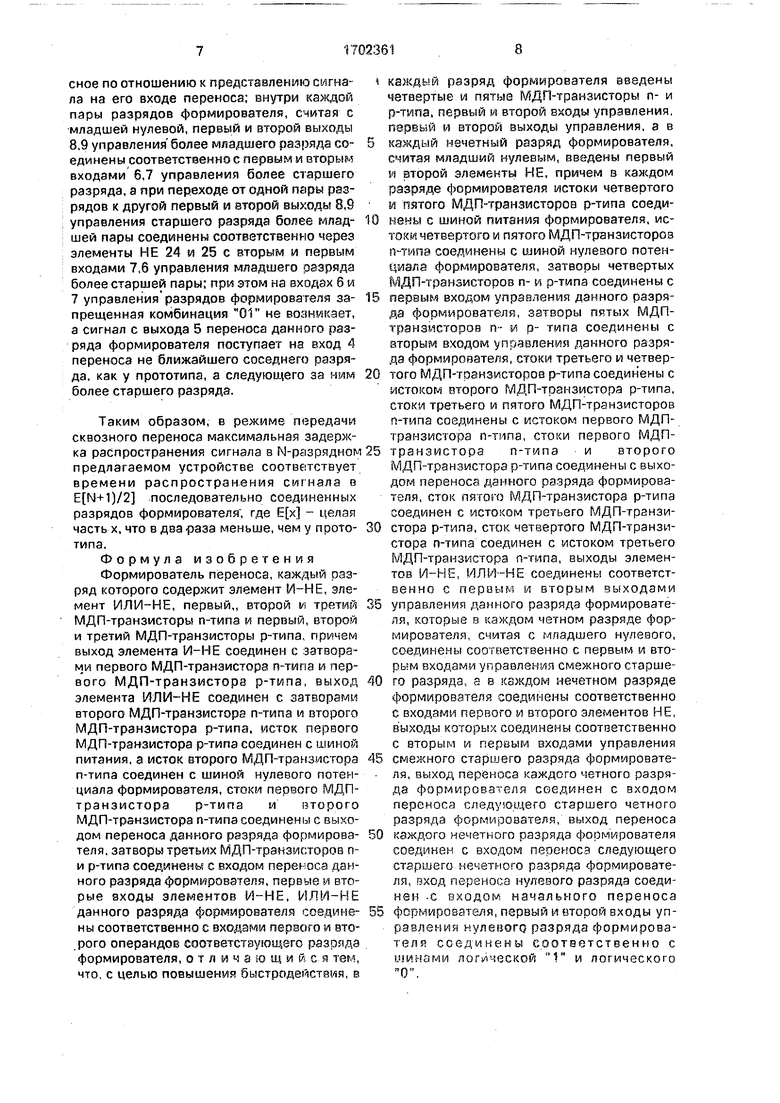

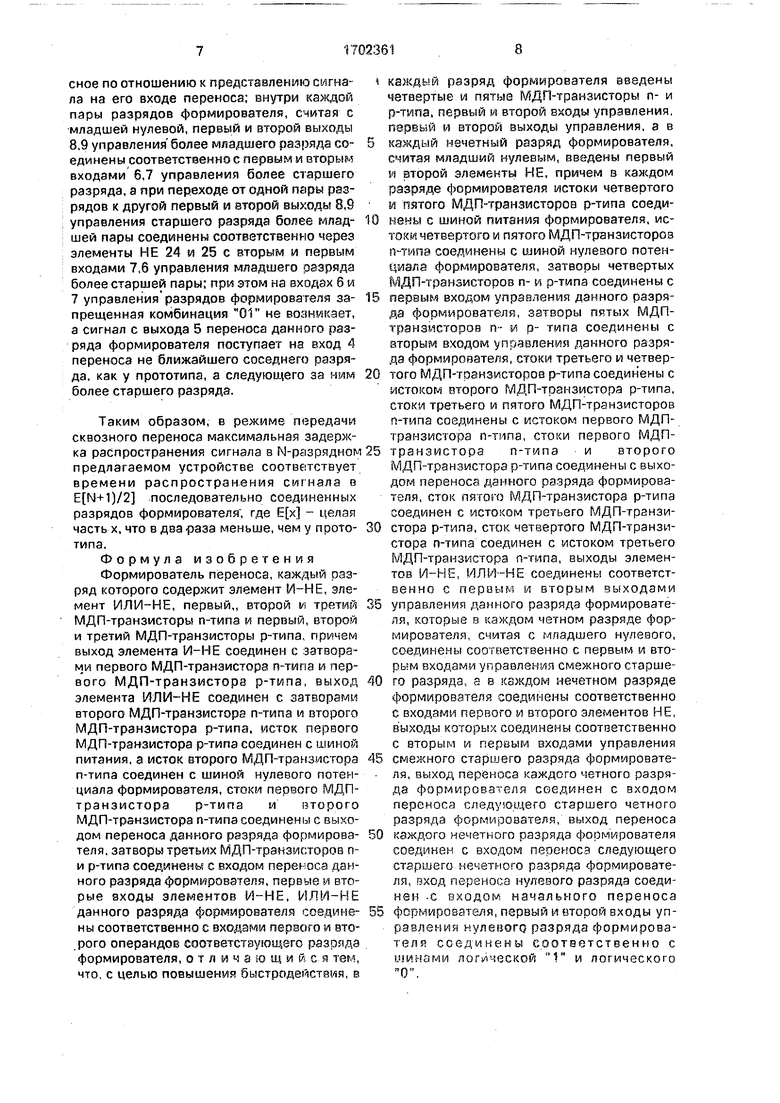

На чертеже представлена электрическая функциональная схема предлагаемого устройства.

На схеме условно показаны младшие

разряды устройства, где каждый разряд 1 содержит входы 2 и 3 первого и второго операндов соответственно, вход 4 переноса и выход 5 переноса, первый и второй входы 6,7 управления, первый и второй выходы 8.9 управления, элементы И-НЕ 10, ИЛИ-НЕ 11, первый - пятый МДП-транзисторы р-типа 12-16 соответственно, первый - пятый МДП-транзисторы п-типа 17 - 21 соответственно, шины 22, 23 питания и

нулевого потенциала устройства, а каждый нечетный разряд устройства, считая с младшего нулевого, содержит первый и второй элементы НЕ 24,25, причем входы переноса младшей пары разрядов устройства соедикены с входом 26 его начального переноса, а выход переноса его старшего разряда образует выход 27 переноса устройства.

Обозначим прямые значения j-ro разря- да первого и второго входных операндов устройства как AJ и Bj соответственно, где j |0,1N-lЈ, N - разрядность входных операндов; прямое значение сигнала переноса, формируемого соответствующим разрядом устройства, как CJ-H, прямое значение начального переноса устройства - как СВх и прямое значение его выходного переноса - как Свых.

Формирователь переноса работает сле- дующим образом.

Будем считать, что уровень логический Г (1) соответствует напряжению шины 22 питания формирователя, а уровень логического О (О) - напряжению шины 23 нулевого потенциала формирователя.

Для удобства выделим два следующих режима работы каждого разряда формирователя: режим генерации собственного переноса; режим передачи сквозного переноса.

Разряд формирователя переноса работает в режиме генерации собственного переноса при совпадении сигналов на его входах 2 и 3 разрядов операндов: при этом на его выходах 8,9 управления формируются сигналы 00 или 11 и в случае комбинации 00 открыты первый и второй МДП-транзисторы р-типа 12,13, закрыты первый и второй МДП-транзисторы п-типа 17,18 и на выходе 5 переноса данного разряда формирователя устанавливается уровень логической в случае комбинации 11, открыты его первый и второй МДП- транзисторы п-типа 17,18, закрыты первый и второй МДП-транзисторы р-типа 12,13 и на выходе 5 переноса данного разряда формирователя устанавливается уровень логического О.

Разряд формирователя работает в режиме передачи сквозного переноса при несовпадении сигналов на его входах 2 и 3 разрядов операндов; при этом на его первом и втором выходах 8,9 управления формируются соответственно уровни логических 1 и О, первый МДП-транзи- стор р-типа 12 и второй МДП-транзистор п-типа 18 закрыты, первый МДП-транзистор п-типа 17 и второй МДП-транзистор р-типа 13 открыты, и состояние сигнала на выходе 5 переноса данного разряда формирователя определяется уровнями сигналов на его первом и втором входах 6,7 управления, а также уровнем сигнала на его входе 4 переноса.

Так, если на входах 6 и 7 управления данного разряда формирователя установлена комбинация 00, соответствующая режиму генерации собственного переноса соседнего более младшего разряда формирователя, у рассматриваемого разряда формирователя открыты четвертый и пятый МДП-транзисторы р-типа 15,16, закрыты четвертый и пятый МДП-транзисторы п-типа 20,21 и на его выходе 5 переноса устанавливается уровень логической 1. Если на входах 6 и 7 управления данного разряда формирователя установлена комбинация 11, также соответствующая режиму генерации собственного переноса соседнего более младшего разряда формирователя, у рассматриваемого разряда формирователя открыты четвертый и пятый МДП-транзисторы п-типа 20,21, закрыты четвертый и пятый МДП-транзисторы р-типа 15,16 и на его выходе 5 переноса устанавливается уровень логического О. Если же на первом и втором входах 6,7 управления данного разряда формирователя установлены состояния 1 и О, соответствующие режиму

передачи сквозного переноса соседнего более младшего разряда формирователя, у рассматриваемого разряда формирователя четвертый МДП-транзистор р-типа 15 и пятый МДП-транзистор п-типа 21 закрыты, пя0 тый МДП-транзистор р-типа 16 и четвертый МДП-транзистор п-типа 20 открыты, и на выход 5 переноса через третьи МДП-транзисторы р-типа 14 и п-типа 19 передается дво- ичноинверсное значение сигнала с его

5 входа 4 переноса; сочетание состояний О и 1 на первом и втором входах 6,7 управления разрядов формирователя запрещено. Для обеспечения правильности функционирования формирователя у самого млад0 шего его разряда первый и второй входы 6,7 управления соединены соответственно с 1 и О, а входы 4 переноса у самой младшей пары его разрядов - с входом 26 начального переноса,

5 Пусть на вход 26 начального переноса формирователя подается прямое значение сигнала входного переноса. Тогда в режиме передачи сквозного переноса на выходы 5 переноса младшей пары разрядов форми0 рователя передается его двоичноинверсное значение, в режиме генерации собственного переноса О на их выходах 5 соответствует комбинации 11 прямых значений сигналов на их входах 2 и 3 операндов, а 1

5 - комбинации 00 этих сигналов.

У следующей пары разрядов формирователя в режиме передачи сквозного переноса на их выходы 5 передается прямое значение сигнала (26) начального переноса;

0 в режиме генерации собственного переноса О на их выходах 5 соответствует комбинации 00 прямых значений сигналов на их входах 2 и 3 операндов, а 1 - комбинации 11 этих сигналов, и так далее.

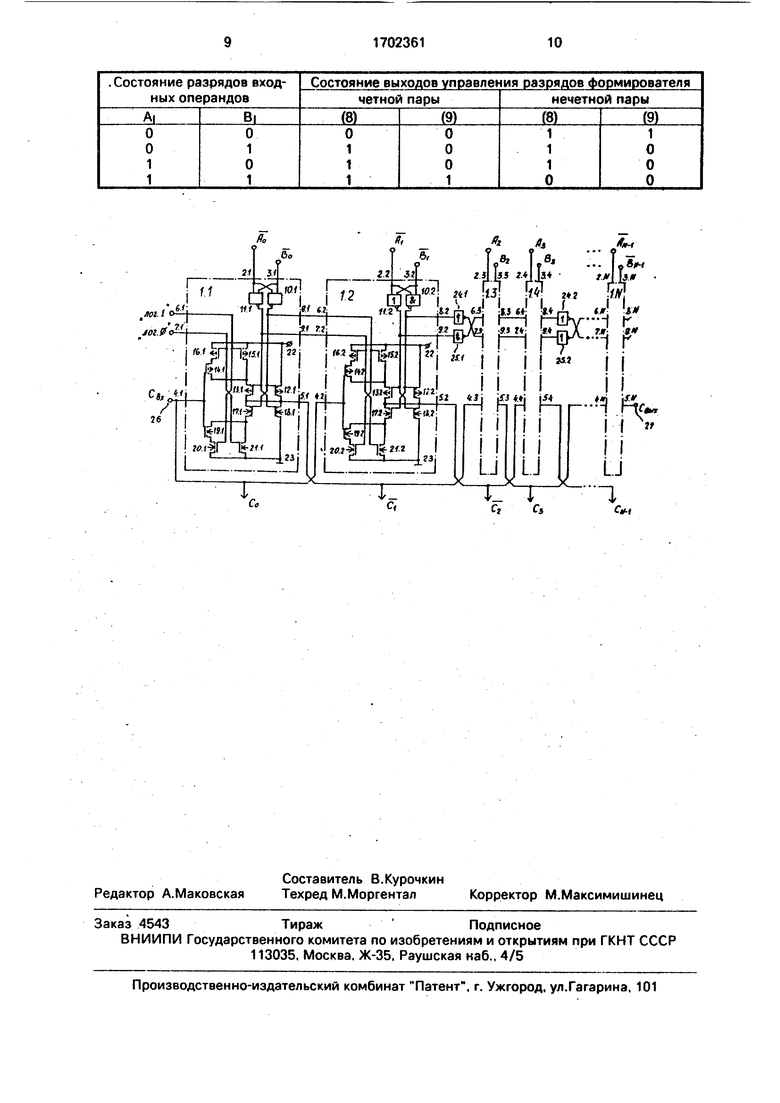

5 В таблице отражены возможные состояния на выходах 8 и 9 управления для четных и нечетных пар разрядов формирователя, считая с младшей нулевой. Из таблицы следует, что для четной па0 ры разрядов формирователя состояния выходов 8 и 9 управления могут быть описаны

как.

F{8)AjVEj , F(9) AjVBj; для нечетной пары - как я

5F (8) AjVBj , F(9) AJ VBj;

причем „ F (8) F(9) и F (9) F(e). Из изложенного выше видно, что для каждого разряда формирователя представление входных операндов - двоичноинверсное по отношению к представлению сигна- ла на его входе переноса; внутри каждой пары разрядов формирователи, считая с младшей нулевой, первый и второй выходы 8.9 управления более младшего разряда со- единены соответственное первым и вторым входами 6,7 управления более старшего разряда, а при переходе от одной пары разрядов к другой первый и второй выходы 8,9 управления старшего разряда более млад- шей пары соединены соответственно через элементы НЕ 24 и 25 с вторым и первым входами 7,6 управления младшего разряда более старшей пары; при этом на входах б и 7 управления разрядов формирователя за- прещенная комбинация 01 не возникает, а сигнал с выхода 5 переноса данного разряда формирователя поступает на вход 4 переноса не ближайшего соседнего разряда, как у прототипа, а следующего за ним более старшего разряда.

Таким образом, в режиме передачи сквозного переноса максимальная задержка распространения сигнала в М-разрядном предлагаемом устройстве соответствует времени распространения сигнала в )/2 последовательно соединенных разрядов формирователя; где - целая часть х, что в два раза меньше, чем у прото- типа.

Формула изобретения Формирователь переноса, каждый разряд которого содержит элемент И-НЕ, элемент ИЛИ-НЕ, первый,, второй м третий МДП-транзисторы n-типа и первым, второй и третий МДП-транзисторы р-типа, причем выход элемента И-НЕ соединен с затворами первого МДП-транзистора n-типа и первого МДП-транзмстора р-типа, выход элемента ИЛИ-НЕ соединен с затворами второго МДП-транзистора n-типа и второго МДП-транзистора р-типа, исток первого МДП-транзистора р-типа соединен с шиной питания, а исток второго МДП-транзистора n-типа соединен с шиной нулевого потенциала формирователя, стоки первого МДП- транзистора р-типа м второго МДП-транзистора n-типа соединены с выходом перекоса данного разряда формирова- теля, затворы третьих МДП-транзисторов п- и р-типз соединены с входом переноса данного разряда формирователя, первые и вторые входы элементов И-НЕ, ИЛИ-НЕ данного разряда формирователя соедине- ны соответственно с входами первого и второго операндов соответствующего разряда формирователя, отличающийся тем, что, с целью повышения быстродействия, в

каждый разряд формирователя введены четвертые и пятые МДП-транзисторы п- и р-типа, первый MI второй входы управления, первый и второй выходы управления, а в каждый нечетный разряд формирователя, считая младший нулевым, введены первый и второй элементы НЕ, причем в каждом разряде формирователя истоки четвертого и пятого МДП-транзисторов р-типа соединены с шиной питания формирователя, истоки четвертого и пятого МДП-транзистороз n-типа соединены с шиной нулевого потенциала формирователя, затворы четвертых МДП-транзисторов п- и р-типа соединены с первым входом управления данного разряда формирователя, затворы пятых МДП- транзмсторов п- и р- типа соединены с вторым входом управления данного разряда формирователя, стоки третьего и четвертого МДП-тоанзисторов р-типа соединены с истоком второго МДП-транзистора р-типа, стоки третьего и пятого МДП-транзисторов n-типа соединены с истоком первого МДП- транзистора n-типа, стоки первого МДП- транзистора n-типа и второго МДП-транзистора р-типа соединены с выходом переноса данного разряда формирователя, сток пятого МДП-транзистора р-типа соединен с истоком третьего МДП-транзистора р-типа, сток четвертого МДП-транзистора п-типа соединен с истоком третьего МДП-транзистора п-типа, выходы элементов И-НЕ, ИЛИ--НЕ соединены соответственно с первым и вторым выходами управления данного разряда формирователя, которые в каждом четном разряде формирователя, считая с младшего нулевого, соединены соответственно с первым и вторым входами управления смежного старшего разряда, а в каждом нечетном разряде формирователя соединены соответственно с входами первого и второго элементов НЕ, выходы которых соединены соответственно с вторым и первым входами управления смежного старшего разряда формирователя, выход переноса каждого четного разряда формирователя соединен с входом переноса следующего старшего четного разряда формирователя, выход переноса каждого нечетного разряда формирователя соединен с входом переноса следующего старшего нечетного разряда формирователя, вход переноса нулевого разряда соединен -с входом начального переноса формирователя, первый и второй входы управления нулевого разряда формирователя соединены соответственно с шинами логической и логического О.

flc 96

21 3/j

11

«HP U

/2

«i

TPI r-r

j i Jrffi

.M.4I

г г

Ii

1

«i

I

f

TT I fe ... 1л«

г 1зз г.1

jtji Г| iLiik i aljTi 5 I- -ub/- 1 f

Л jugX..

f

n

I I I I M i i i i i

гЗ ftM P4r-«I Й

i i f

LJ

ТГ

c«

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь переноса | 1991 |

|

SU1798778A1 |

| СУММАТОР | 1994 |

|

RU2049346C1 |

| Узел формирования переноса | 1986 |

|

SU1363189A1 |

| Узел формирования переноса в сумматоре | 1985 |

|

SU1312567A1 |

| УСТРОЙСТВО СЛОЖЕНИЯ С УСКОРЕННЫМ ПЕРЕНОСОМ | 2000 |

|

RU2198421C2 |

| Устройство для формирования группового переноса | 1985 |

|

SU1335981A1 |

| Узел формирования переноса в сумматоре | 1985 |

|

SU1291969A1 |

| Узел формирования переноса в сумматоре | 1985 |

|

SU1287147A1 |

| СДВИГОВЫЙ РЕГИСТР (ВАРИАНТЫ) | 2013 |

|

RU2530271C1 |

| Формирователь переноса | 1984 |

|

SU1223223A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических цифровых устройств на КМДП-транзисторах, в частности многоразрядных параллельных суммато- ров-вычитателей и схем сравнения. Цель изобретения - повышение быстродействия. Формирователь переноса содержит в каждом разряде входы первого и второго операндов, вход переноса, выход переноса, первый и второй входы управления, первый и второй выходы управления, элемент И-НЕ, элемент ИЛИ-НЕ, пять МДП-транзисторов р-типа, пять МДП-транзисторов n-типа, шины питания и нулевого потенциала, соединенные между собой функционально. Кроме того, каждый нечетный разряд (считая младший нулевым) содержит два элемента НЕ, соединенных функционально, причем входы переноса младшей пары разрядов соеди- нены с входом начального переноса формирователя, а выход переноса старшего разряда образует выход переноса формирователя. 1 ил., 1 табл. С/ С

| Узел формирования переноса в сумматоре | 1985 |

|

SU1312567A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Узел формирования переноса | 1986 |

|

SU1363189A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

Авторы

Даты

1991-12-30—Публикация

1990-04-18—Подача