18131011U

/3 Ггз

о оо оо го

ОЭ

со

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления десятичных чисел | 1990 |

|

SU1774328A1 |

| Устройство для деления десятичных чисел | 1984 |

|

SU1241235A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

| Устройство для деления чисел | 1980 |

|

SU857977A1 |

| Устройство для деления | 1979 |

|

SU773618A1 |

| Устройство для деления | 1990 |

|

SU1783521A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

| Устройство для деления десятичных чисел | 1982 |

|

SU1048473A1 |

| Устройство для деления чисел | 1981 |

|

SU1119006A1 |

| Устройство для деления | 1990 |

|

SU1709352A1 |

Изобретение относится к вычислительной технике и может быть использовано для быстрого деления десятичных чисел. Цель изобретения сокращение аппаратурных затрат на реализацию устройства. Устройство содержит регистры 1-3 делимого, делителя и частного, блок k формирования кратных делителя, сумматор 5, пять вычитателей 6-10, первый коммутатор 11, блок 13 формирования цифры частного и нововведенный второй коммутатор 12. 2 ил., 1 табл. 5 (Л

Фиг /

#

Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных машинах, выполняющих операцию деся- тичной арифметики.

Цель изобретения - сокращение аппаратурных затрат устройства.

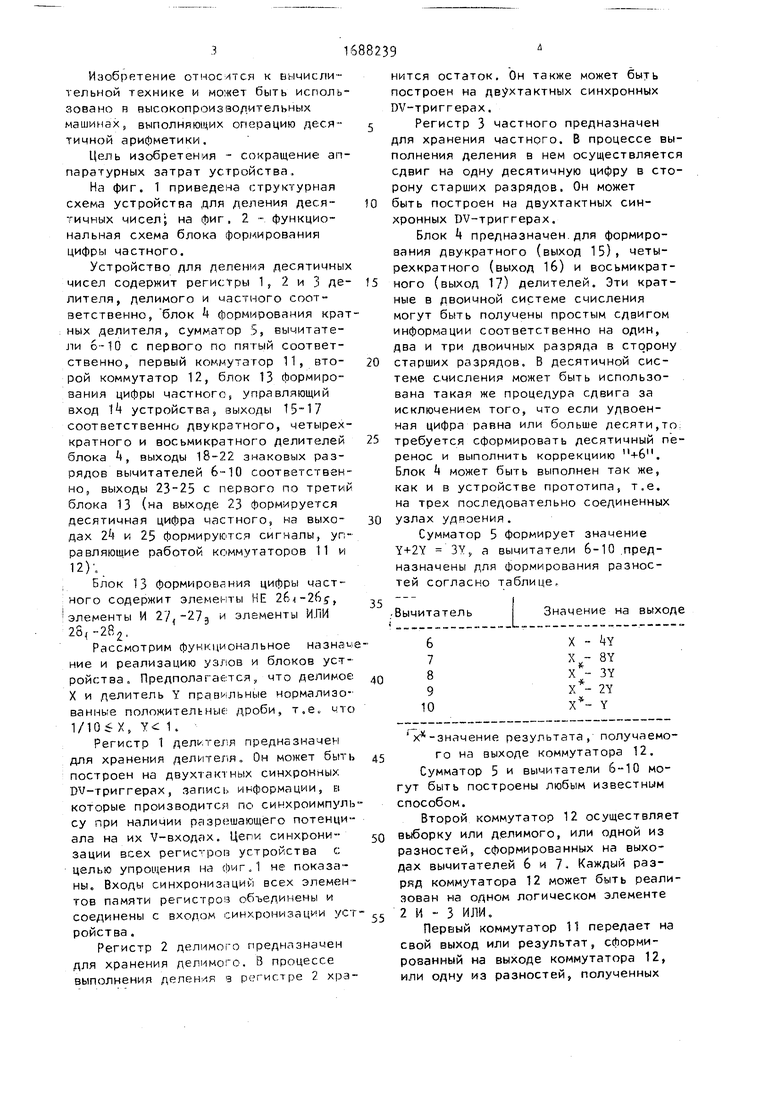

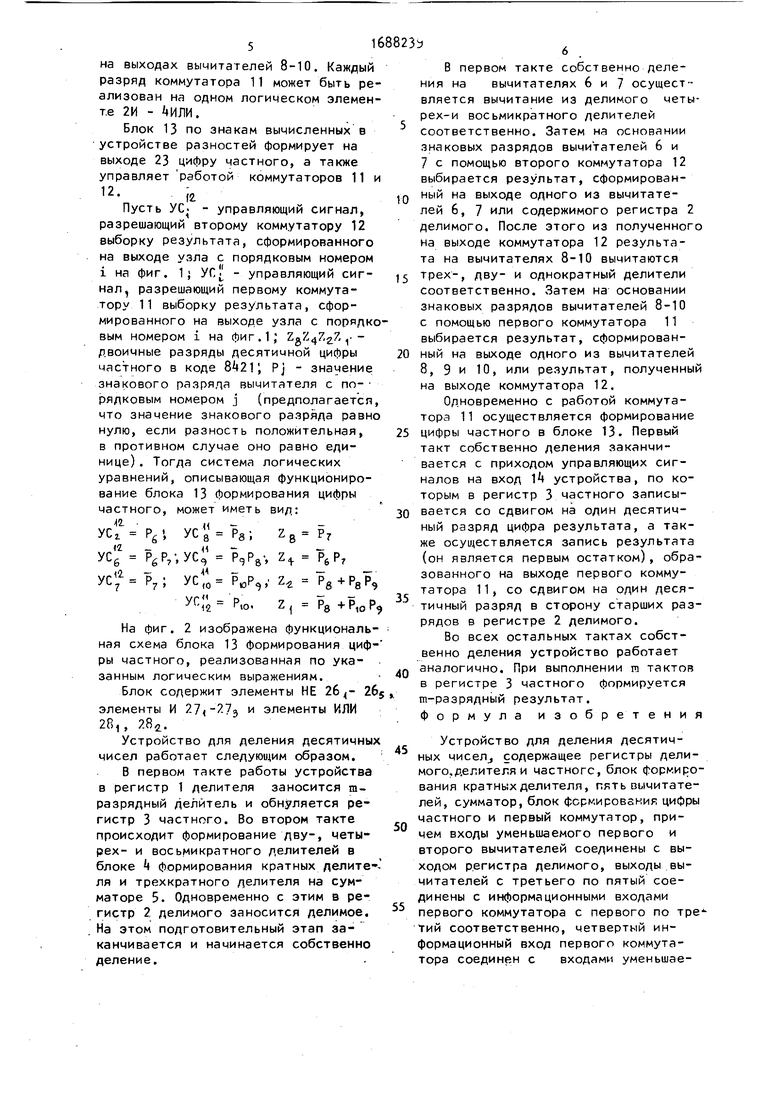

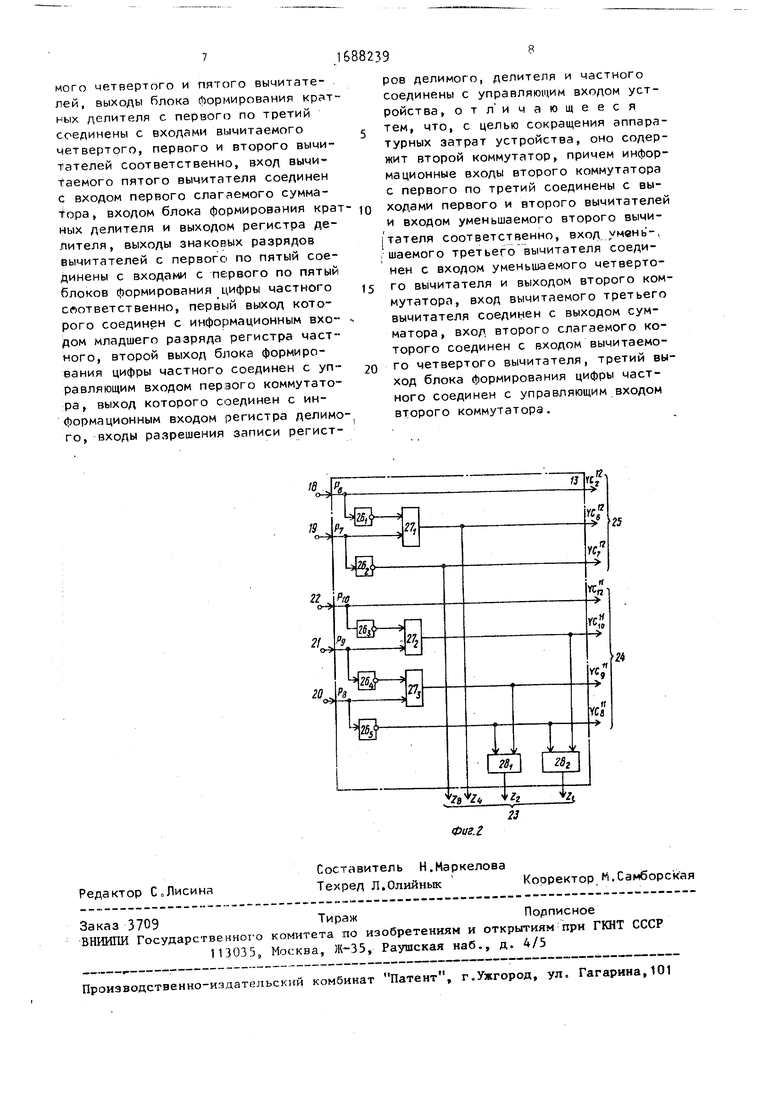

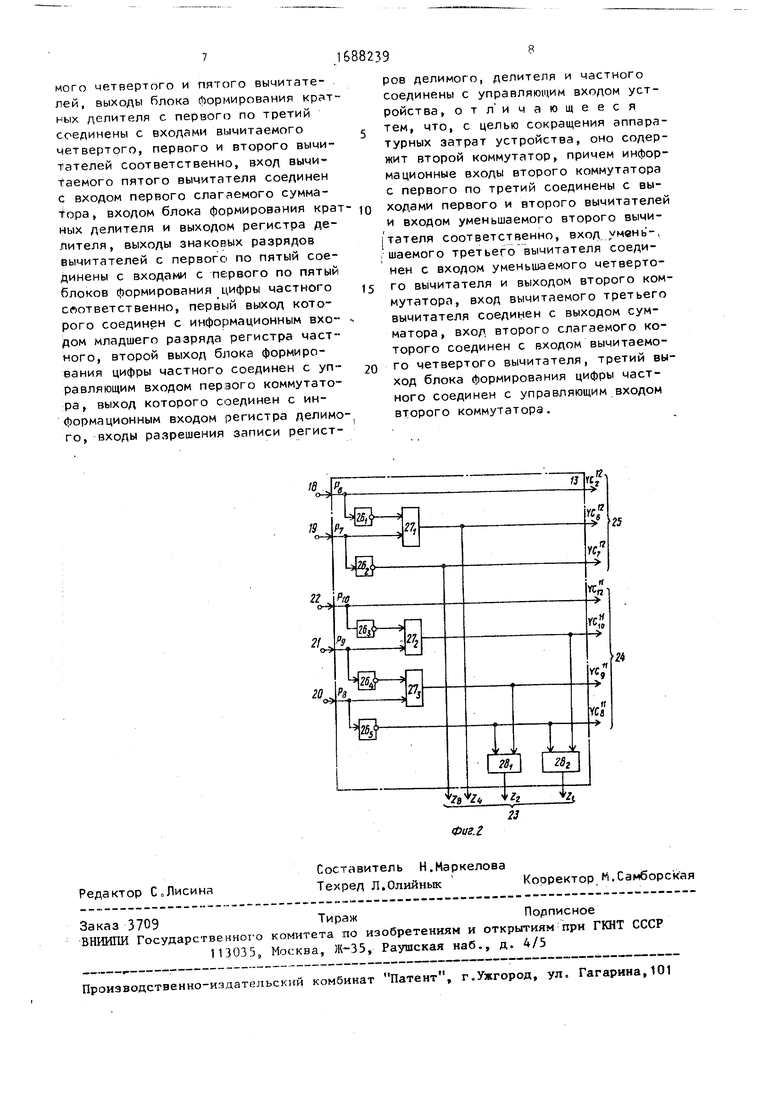

На фиг. 1 приведена структурная схема устройства для деления деся- тичных чисел; на фиг. 2 - функциональная схема блока формирования цифры частного.

Устройство для деления десятичных чисел содержит регистры 1, 2 и 3 де- лителя, делимого и частного соответственно, блок Формирования кратных делителя, сумматор 5, вычитате- ли 6-10 с первого по пятый соответственно, первый коммутатор 11, вто- рой коммутатор 12, блок 13 формирования цифры частного, управляющий вход устройства, выходы 15-17 соответственно двукратного, четырехкратного и восьмикратного делителей блока 1+, выходы 18-22 знаковых разрядов вычитателей 6-10 соответственно, выходы 23-25 с первого по третий блока 13 (на выходе 23 формируется десятичная цифра частного, на выхо- дах и 25 формируются сигналы, уп- равляюшие работой коммутаторов 11 и 12).

Блок 13 формирования цифры частного содержит элементы НЕ 261-265, элементы И 2/,-27} и элементы ИЛИ .

Рассмотрим функциональное назначние и реализацию узлов и блоков устройства. Предполагается, что делимое X и делитель Y правильные нормализованные положительные дроби, т.е. что 1 / 10 X , Y с 1 .

Регистр 1 делителя предназначен для хранения делителя. Он может быть построен на двухтактных синхронных DV-триггерах, запись информации, в которые производится по синхроимпульсу при наличии разрешающего потенциала на их V-входах. Цепи синхрони- зации всех регистров устройства с целью упрощения на фиг.1 не показаны. Входы синхронизации всех элементов памяти регистров объединены и соединены с входом синхронизации уст ройства.

Регистр 2 делимого предназначен для хранения делимого. В процессе выполнения деления в регистре 2 хра

нится остаток. Он также может быть построен на двухтактных синхронных DV-триггерах.

Регистр 3 частного предназначен для хранения частного, В процессе выполнения деления в нем осуществляетс сдвиг на одну десятичную цифру в сторону старших разрядов. Он может быть построен на двухтактных синхронных DV-триггерах.

Блок k предназначен для формирования двукратного (выход 15), четырехкратного (выход 16) и восьмикратного (выход 17) делителей. Эти кратные в двоичной системе счисления могут быть получены простым сдвигом информации соответственно на один, два и три двоичных разряда в сторону старших разрядов. В десятичной системе счисления может быть использована такая же процедура сдвига за исключением того, что если удвоенная цифра равна или больше десяти,то требуется сформировать десятичный перенос и выполнить коррекциию +6. Блок k может быть выполнен так же, как и в устройстве прототипа, т.е. на трех последовательно соединенных узлах удооения.

Сумматор 5 формирует значение Y+2Y 3V, а вычитатели 6-10 предназначены для формирования разностей согласно таблице.

35

Вычитатель

Значение на выходе

х -значение результата, получаемого на выходе коммутатора 12.

Сумматор 5 и вычитатели 6-10 могут быть построены любым известным способом.

Второй коммутатор 12 осуществляет выборку или делимого, или одной из разностей, сформированных на выходах вычитателей 6 и 7- Каждый разряд коммутатора 12 может быть реализован на одном логическом элементе 2 И - 3 ИЛИ.

Первый коммутатор 11 передает на свой выход или результат, сформированный на выходе коммутатора 12, или одну из разностей, полученных

на выходах вычитагелей 8-10. Каждый разряд коммутатора 11 может быть реализован на одном логическом элементе 2И - 4ИЛИ.

Блок 13 по знакам вычисленных в устройстве разностей формирует на выходе 23 цифру частного, а также управляет работой коммутаторов 11 и 12. k

Пусть УС - управляющий сигнал, разрешающий второму коммутатору 12 выборку результата, сформированного на выходе узла с порядковым номером i на фиг. 1; УГ, - управляющий сигнал, разрешающий первому коммутатору 11 выборку результата, сформированного на выходе узла с порядковым номером i на фиг.1; .7 .- двоичные разряды десятичной цифры частного в коде PJ - значение знакового разряда вымитателя с порядковым номером j (предполагаете, что значение знакового разряда равно нулю, если разность положительная, в противном случае оно равно единице) . Тогда система логических уравнений, описывающая функционирование блока 13 Формирования цифры частного, может иметь вил:

На фиг. 2 изображена функциональная схема блока 13 формирования цифры частного, реализованная по указанным логическим выражениям.

Блок содержит элементы НЕ 2б элементы И и элементы ИЛИ 28,, 284.

Устройство для деления десятичных чисел работает следующим образом.

В первом такте работы устройства в регистр 1 делителя заносится га- разрядный делитель и обнуляется регистр 3 частного. Во втором такте происходит формирование дву-, четырех- и восьмикратного делителей в блоке Ц формирования кратных делителя и трехкратного делителя на сумматоре 5. Одновременно с этим в регистр 2 делимого заносится делимое. На этом подготовительный этап заканчивается и начинается собственно деление.

5

0

5

0

В первом такте собственно деления на вычитателях 6 и 7 осуществляется вычитание из делимого четы- рех-и восьмикратного делителей соответственно. Затем на основании знаковых разрядов вычи тателей 6 и 7 с помощью второго коммутатора 12 выбирается результат, сформированный на выходе одного из вычитате- лей 6, 7 или содержимого регистра 2 делимого. После этого из полученного на выходе коммутатора 12 результата на вычитателях 8-Ю вычитаются трех-, дву- и однократный делители соответственно. Затем на основании знаковых разрядов вычитателей 8-10 с помощью первого коммутатора 11 выбирается результат, сформированный на выходе одного из вычитателей 8, 9 и 10, или результат, полученный на выходе коммутатора 12.

Одновременно с работой коммутатора 11 осуществляется формирование 5 цифры частного в блоке 13. Первый такт собственно деления заканчивается с приходом управляющих сигналов на вход устройства, по которым в регистр 3 мастного записывается со сдвигом на один десятичный разряд цифра результата, а также осуществляется запись результата (он является первым остатком), образованного на выходе первого коммутатора 11, со сдвигом на один десятичный разряд в сторону старших разрядов в регистре 2 делимого.

Во всех остальных тактах собственно деления устройство работает аналогично. При выполнении п тактоя в регистре 3 частного Формируется m-разрядный результат. Формула изобретения

0

5

0

Устройство для деления десятичных чиceлJ содержащее регистры делимого, делителя и частного, блок формирования кратных делителя, пятьвычитателей, сумматор, блок формирования цифры частного и первый коммутатор, причем входы уменьшаемого первого и второго вычитателей соединены с выходом регистра делимого, выходы вычитателей с третьего по пятый соединены с информационными входами первого коммутатора с первого по третий соответственно, четвертый информационный вход первого коммутатора соединен с входами уменьшавмого четвертого и пятого вычитателей, выходы блока формирования кратных делителя с первого по третий соединены с входами вычитаемого четвертого, первого и второго вычи- тателей соответственно, вход вычитаемого пятого вычитателя соединен с входом первого слагаемого сумматора, входом блока формирования краных делителя и выходом регистра делителя, выходы знаковых разрядов вычитателей с первого по пятый соединены с входами с первого по пятый блоков формирования цифры частного соответственно, первый выход которого соединен с информационным вхо- дом младшего разряда регистра частного, второй выход блока формирования цифры частного соединен с управляющим входом первого коммутатора, выход которого соединен с информационным входом регистра делимого, входы разрешения записи регист19

ров делимого, делителя и мастного соединены с управляющим входом устройства, отличающееся

тем, что, с целью сокращения аппаратурных затрат устройства, оно содержит второй коммутатор, причем информационные входы второго коммутатора с первого по третий соединены с выходами первого и второго вычитателей и входом уменьшаемого второго вычи- .тэтеля соответственно, вход умень-, шаемого третьего вычитателя соединен с входом уменьшаемого четвертого вычитателя и выходом второго коммутатора, вход вычитаемого третьего вычитателя соединен с выходом сумматора, вход второго слагаемого которого соединен с входом вычитаемого четвертого вычитателя, третий выход блока формирования цифры частного соединен с управляющим входом второго коммутатора.

| Ричарде Р.К | |||

| Арифметические операции на цифровых вычислительных машинах | |||

| М.: Иностранная литература, 1957, с.292, рис.9-3 | |||

| Авторское свидетельство СССР V , кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-10-30—Публикация

1989-12-29—Подача