Х|

2

СА) ГО 00

Изобретение относится к вычислительной технике и может быть использовано при разработке быстродействующих устройств деления десятичных чисел.

Известно устройство для деления десятичных чисел, содержащее регистры делимого, делителя и частного блок формирования кратных, восемь вычитате- лей, сумматор и блок формирования цифры частного.

Недостатком известного устройства является большое количество аппаратуры

Наиболее близко к предлагаемому - устройство для деления десятичных чисел, содержащее регистры делимого, делителя и частного, два коммутатора, пять вычитате- лей, сумматор, блок формирования кратных и блок формирования цифры частного, причем входы уменьшаемых первого и второго вычитателей соединены с выходом регистра делимого и первым информационным входом первого коммутатора, выход которого соединен с входами уменьшаемых третьего, четвертого и пятого вычитателей и первым информационным входом второго коммутатора, второй, третий и четвертый информа- ционные входы которого соединены соответственно с выходами третьего, четвертого и пятого вычитателей, вход вычитаемого третьего вычитателя соединен с первым выходом блока формирования кратных и первым информационным входом сумматора, вход вычитаемого четвертого вычитателя соединен с выходом регистра делителя, входом блока формирования кратных и вторым информационным входом сумматора, выход которого соединен с входом вычитаемого пятого вычитателя, второй и третий выходы блока формирования кратных соединены с входами вычитаемых соответственно первого и второго вычитателей. выходы которых соединены с вторым и третьим информационными входами соответственно первого коммутатора выход второго коммутатора соединен с информационным входом регистра делимого, управляющий вход устройства соединен с входами разрешения записи регистров делимого, делителя и частного, выходы знаковых разрядов вычитателей соединены с входами блока формирования цифры частного, первый выход которого соединен с информационным входом младшего разряда регистра частного, а второй и третий выходы - с управляющими входами первого и второго коммутаторов соответственно

Недостаток известного устройства - большие аппаратурные затраты

Цель изобретения - сокращение аппаратурных затрат.

Поставленная цель достигается тем, что в устройство для деления десятичных чисел, содержащее регистры делимого, делителя и частного два коммутатора, четыре

вычитателя, блок формирования кратных, причем входы уменьшаемых первого и второго вычитателей соединены с выходом регистра делимого и первым информационным входом первого коммута0 тора, выход которого соединен с входом уменьшаемого третьего вычитателя и первым информационным входом второго коммутатора, второй информационный вход которого соединен с выходом третьего вы5 читателя, вход которого соединен с первым выходом блока формирования кратных, второй и третий выходы которого соединены с входами вычитаемых первого и второго вычитателей, выходы которых соединены с

0 вторым и третьим информационными входами соответственно первого коммутатора, выход регистра делителя соединен с входом блока формирования кратных и входом вычитаемого четвертого вычитателя, управля5 ющмй вход устройства соединен с входами разрешения записи регистров делимого, делителя и частного, введен третий коммутатор, выход которого соединен с информационным входом регистра делимо0 го,выход второго коммутатора соединен с входом уменьшаемого четвертого вычитателя и первым информационным входом третьего коммутатора, второй информационный вход которого соединен с выходом

5 четвертого вычитателя, выходы знаковых разрядов первого и второго вычитателей соединены соответственно с первым и вторым управляющими входами первого коммутатора и входами двух старших бит младшего

0 разряда регистра частного, входы двух младших бит младшего разряда которого соединены с управляющими входами второго и третьего коммутаторов и выходами знаковых разрядов третьего и четвертого

5 вычитателей соответственно.

На чертеже приведена структурная схема устройства для деления десятичных чисел.

Устройство содержит регистры 1-3 де0 лителя, делимого и частного соответствен- ,но, блок 4 формирования кратных, вычитатели 5-8 с первого по четвертый соответственно, первый 10, второй 11 и третий 9 коммутаторы, управляющий вход 12 уст5 ройства, выходы 13-15 соответственно двукратного,четырехкратногои восьмикратного делителей блока 4, выходы 16-19 знаковых разрядов вычитателей 6, 5, 7 и 8 соответственно.

Рассмотрим функциональное назначение и реализацию узлов и блоков устройства. Предполагается, что делимое X и делитель Y - правильные нормализованные положительные дроби, т. е. 1 /10 X, Y 1.

Регистр 1 делителя предназначен для хранения делителя. Он может быть построен на двухтактных синхронных D V-тригге- рах, запись информации в которые производится по синхроимпульсу при нали- чии разрешающего потенциала на их V-BXO- дах, Цепи синхронизации всех регистров устройства с целью упрощения на чертеже не показаны. Отметим -одтоко, что входы синхронизации всех элементов памяти ре- гистров объединены и соединены с входом синхронизации устройства.

Регистр 2 делимого предназначен для хранения делимого. В процессе выполнения деления в регистр 2 записываются зна- чения остатков. Он также может быть построен на двухтактных синхронных D V- триггерах.

„Регистр 3 частного предназначен для хранения частного. В прюцессе выполнения деления в.нем осуществляется однотакто- вый сдвиг на одну десятичную цифру в сто- ррну старших раз р-ядо в. Он может быть построен на двухтактных синхронных D V- тригге рах,

Блок 4 предназначен для формирования двукратного (выход 13), четырехкратного (выход 14) и восьмикратного (выход 15} делителей. Эти кратные в двоичной системе счисления могут быть получены простым сдвигом информации соответственно на один, два и три двоичных разряда в сторону старших разрядов. В десятичной системе счисления может быть использована такая же процедура сдвига,за исключением того, что если удвоенная цифра равна или больше десяти, требуется сформировать десятичный перенос и выполнить коррекцию +6. Блок 4 может быть выполнен как в устройстве-прототипе, т. е. на трех последова- тельно соединенных узлах удвоения, Вычитатели 5-8 предназначены для формирования разностей согласно табл. 1. Они могут быть построены любым известным способом,

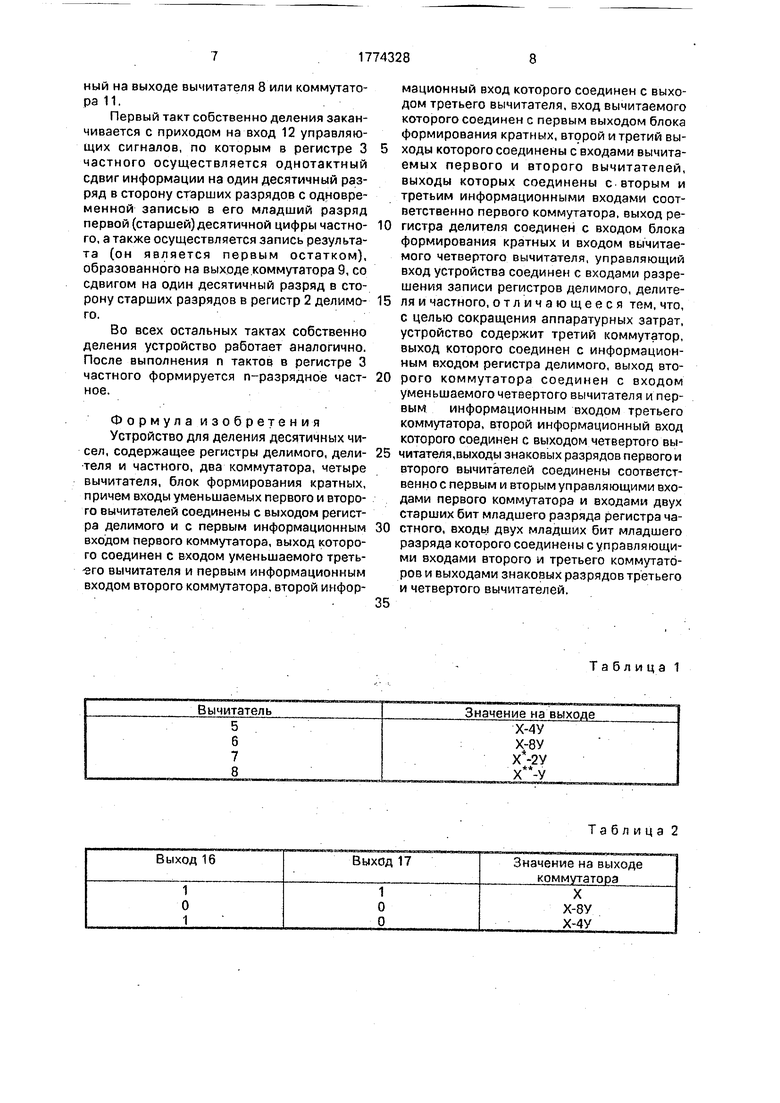

В табл, 1 приняты следующие обозначения: X - значение результата, получаемого на выходе коммутатора 10; X - значение результата, получаемого на выходе коммутатора 11.

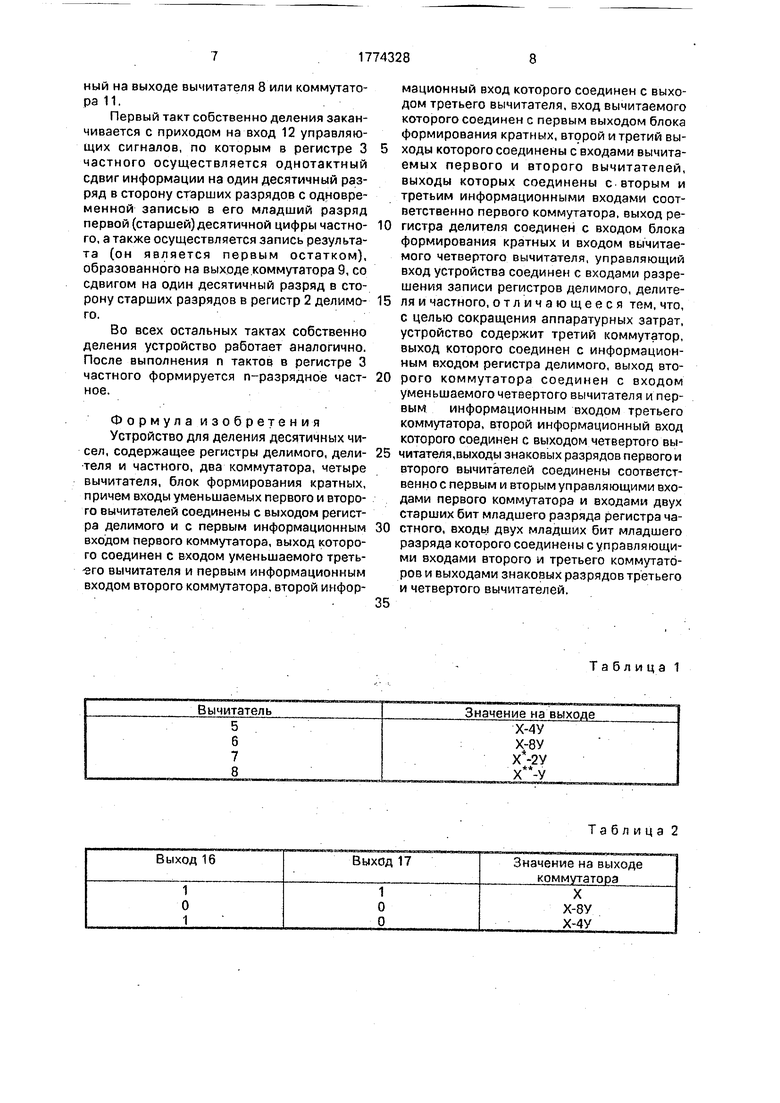

Первый коммутатор 10 осуществляет выборку в соответствии с табл. 2 или остатка (делимого), хранимого в регистре 2. или одной из разностей, сформированных на выходах вычитателей 5 и б, в зависимости от

знаковых разрядов данных вычитэтелей. Каждый разряд коммутатора 10 может быть реализован на одном мультиплексоре 3-1, работающем в соответствии с табл. 2.

Второй коммутатор 11 передает на свой выход или результат, сформированный на выходе коммутатора 10, или разность, сформированную на выходе вычитателя 7. Так, если значение сигнала на выходе 18 знакового разряда вычитателя 7 равно нул ю, коммутируется разность, сформированная на выходе вычитателя 7. В противном случае коммутируется информация с выхода коммутатора 10. Каждый разряд коммутатора 11 может быть реализован на одном логическом элементе 2И-2ИЛИ.

Третий коммутатор 9 передает на свой выход или результат, сформированный на выходе коммутатора 11, или разность, сформированную на выходе вычитателя 8. Так, если значение сигнала на выходе 19 знакового разряда вычитателя 8 равно нулю, передается разность с выхода вычитателя 8. В противном случае передается результат с выхода коммутатора 11. Каждый разряд коммутатора 9 может быть реализован на одном логическом элементе 2М-2ИЛИ.

Устройство для деления десятичных чисел работает следующим образом.

В первом такте работы устройства в регистр 1 делителя загружается п-разрядный делитель и обнуляется регистр 3 частного. Во втором такте происходит формирование двух-( четырех- и восьмикратного делителей в блоке 4 формирования кратных и одновременно в регистр 2 делимого заносится делимое. На этом подготовительный этап заканчивается и начинается собственно деление.

В первом такте собственно деления на вычитателях 5 и б осуществляется вычитание из делимого четырех- и восьмикратного делителей соответственно. Затем на основании значений знаковых разрядов вычитателей 5 и 6 с помощью коммутатора 10 выбирается или результат, сформированный на выходе одного из вычитателей 5 и 6, или содержимое регистра 2 делимого. После этого из полученного на выходе коммутатора 10 результата на вычитателе 7 вычитается двукратный делитель. Далее, на основании знакового разряда вычитателя 7 с помощью коммутатора 11 выбирается результат, сформированный на выходе вычитателя 7 или коммутатора 10. После этого из полученного на выходе коммутатора 11 результата в вычитателе 8 вычитается делитель. Затем на основании знакового разряда вычитателя 8 с помощью коммутаный на выходе вычитателя 8 или коммутатора 11.

Первый такт собственно деления заканчивается с приходом на вход 12 управляющих сигналов, по которым в регистре 3 частного осуществляется однотактный сдвиг информации на один десятичный разряд в сторону старших разрядов с одновременной записью в его младший разряд первой (старшей) десятичной цифры частного, а также осуществляется запись результата (он является первым остатком), образованного на выходе коммутатора 9, со сдвигом на один десятичный разряд в сторону старших разрядов в регистр 2 делимого.

Во всех остальных тактах собственно деления устройство работает аналогично. После выполнения п тактов в регистре 3 частного формируется n-разрядное частное.

Формула изобретения Устройство для деления десятичных чисел, содержащее регистры делимого, делителя и частного, два коммутатора, четыре вычитателя, блок формирования кратных, причем входы уменьшаемых первого и второго вычитателей соединены с выходом регистра делимого и с первым информационным входом первого коммутатора, выход которого соединен с входом уменьшаемого треть- -эго вычитателя и первым информационным входом второго коммутатора, второй информационный вход которого соединен с выходом третьего вычитателя, вход вычитаемого которого соединен с первым выходом блока формирования кратных, второй и третий выходы которого соединены с входами вычитаемых первого и второго вычитателей, выходы которых соединены с вторым и третьим информационными входами соответственно первого коммутатора, выход регистра делителя соединен с входом блока формирования кратных и входом вычитаемого четвертого вычитателя, управляющий вход устройства соединен с входами разрешения записи регистров делимого, делителя и частного, отличающееся тем, что, с целью сокращения аппаратурных затрат, устройство содержит третий коммутатор, выход которого соединен с информационным входом регистра делимого, выход второго коммутатора соединен с входом уменьшаемого четвертого вычитателя и первым информационным входом третьего коммутатора, второй информационный вход которого соединен с выходом четвертого вычитателя,выходы знаковых разрядов первого и второго вычитателей соединены соответственно с первым и вторым управляющими входами первого коммутатора и входами двух старших бит младшего разряда регистра частного, входы двух младших бит младшего разряда которого соединены с управляющими входами второго и третьего коммутаторов и выходами знаковых разрядов третьего и четвертого вычитателей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления десятичных чисел | 1984 |

|

SU1241235A1 |

| Устройство для деления десятичных чисел | 1989 |

|

SU1688239A1 |

| Устройство для деления | 1979 |

|

SU773618A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

| Устройство для деления чисел | 1980 |

|

SU857977A1 |

| Устройство для деления | 1990 |

|

SU1709352A1 |

| Устройство для деления чисел | 1981 |

|

SU1119006A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

| Устройство для деления | 1985 |

|

SU1317431A1 |

| Устройство для деления | 1990 |

|

SU1783521A1 |

Изобретение относится к вычислительной технике и может быть использовано для быстрого деления десятичных чисел. Целью изобретения является сокращение аппаратурных затрат на реализацию устройства. Устройство содержит регистры 1-3 делимого, делителя и частного, блок 4 формирования кратных делителя, четыре вычитателя 5-8, первый и второй коммутаторы 10-11 и нововведенный коммутатор 9. t ил. 2 табл.

Таблица 1

| Устройство для деления десятичных чисел | 1984 |

|

SU1241235A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления десятичных чисел | 1989 |

|

SU1688239A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Механизм для сообщения поршню рабочего цилиндра возвратно-поступательного движения | 1918 |

|

SU1989A1 |

Авторы

Даты

1992-11-07—Публикация

1990-04-09—Подача