Изобретение относится к импульсной и вычислительной технике и может быть использовано в контрольно-измерительном оборудовании для полупроводниковых приборов, в частности в системах автоматического контроля динамического функционирования цифровых узлов электронной аппаратуры.

Целью изобретения является повышение производительности при использовании устройства для автоматизированного выравнивания временного положения фронта и среза выходного сигнала.

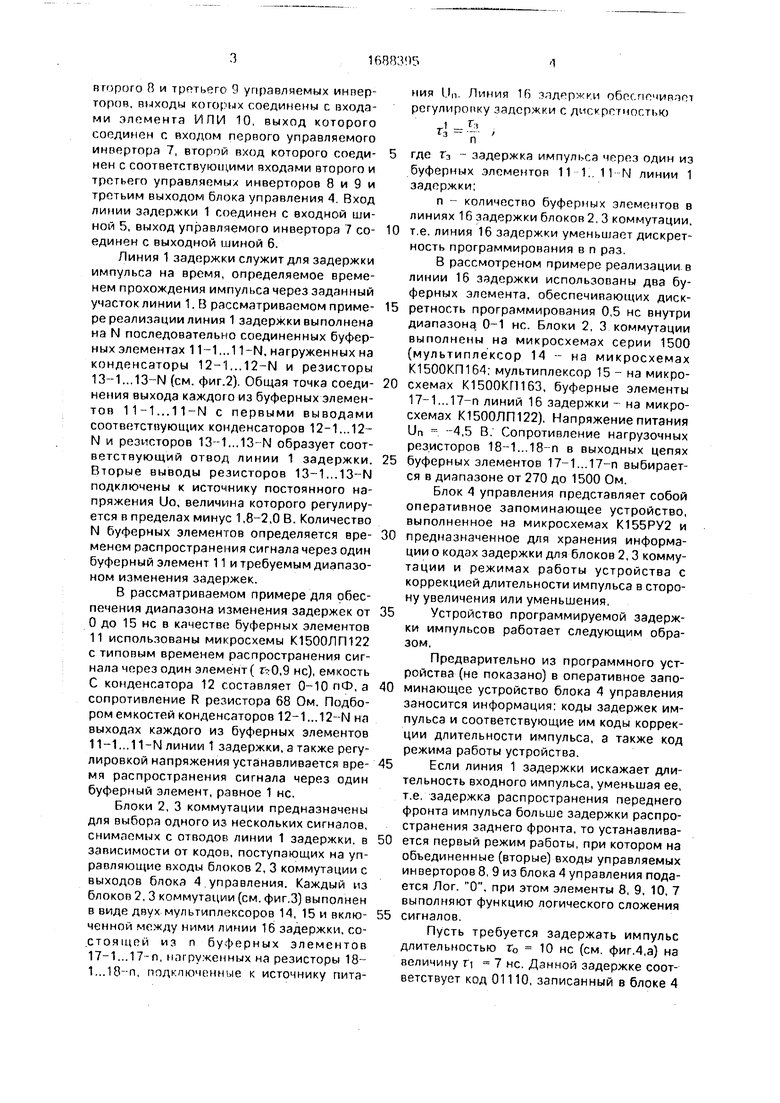

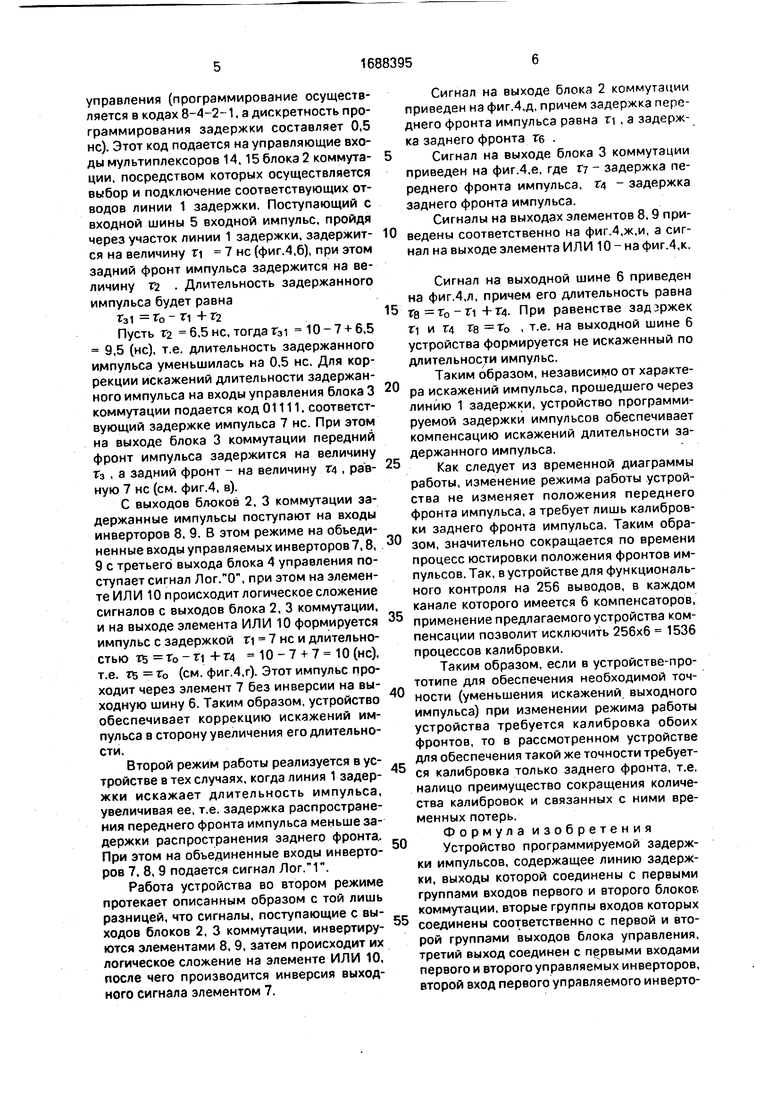

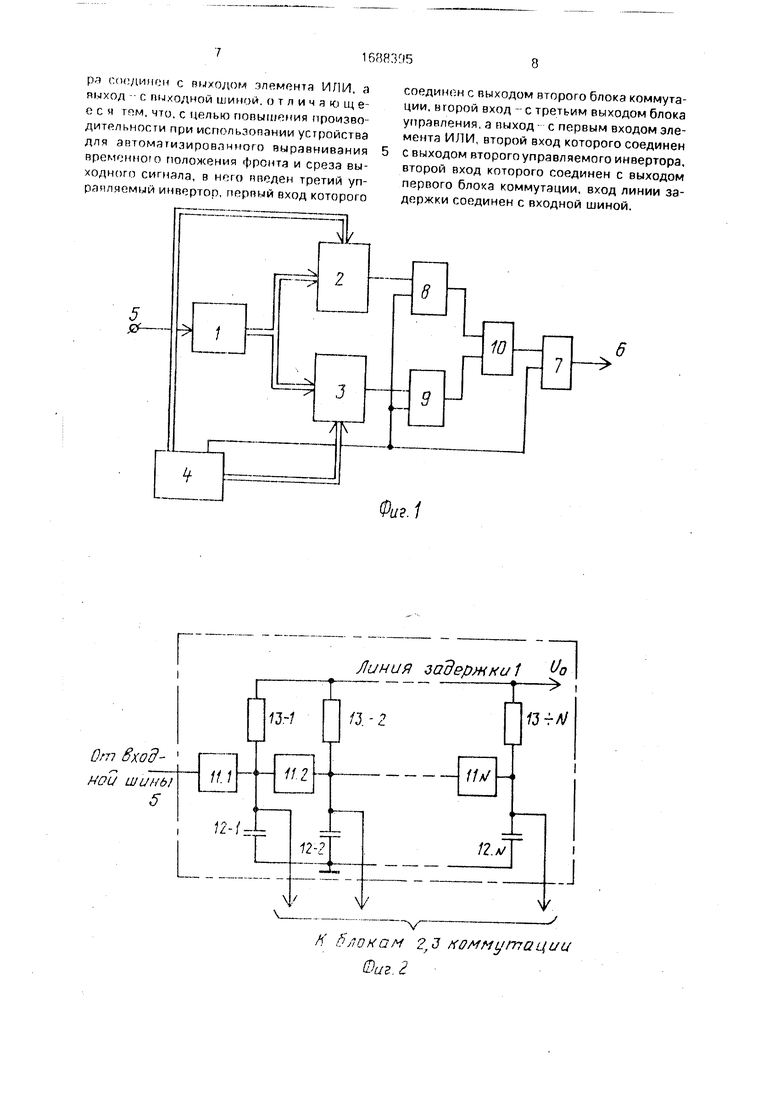

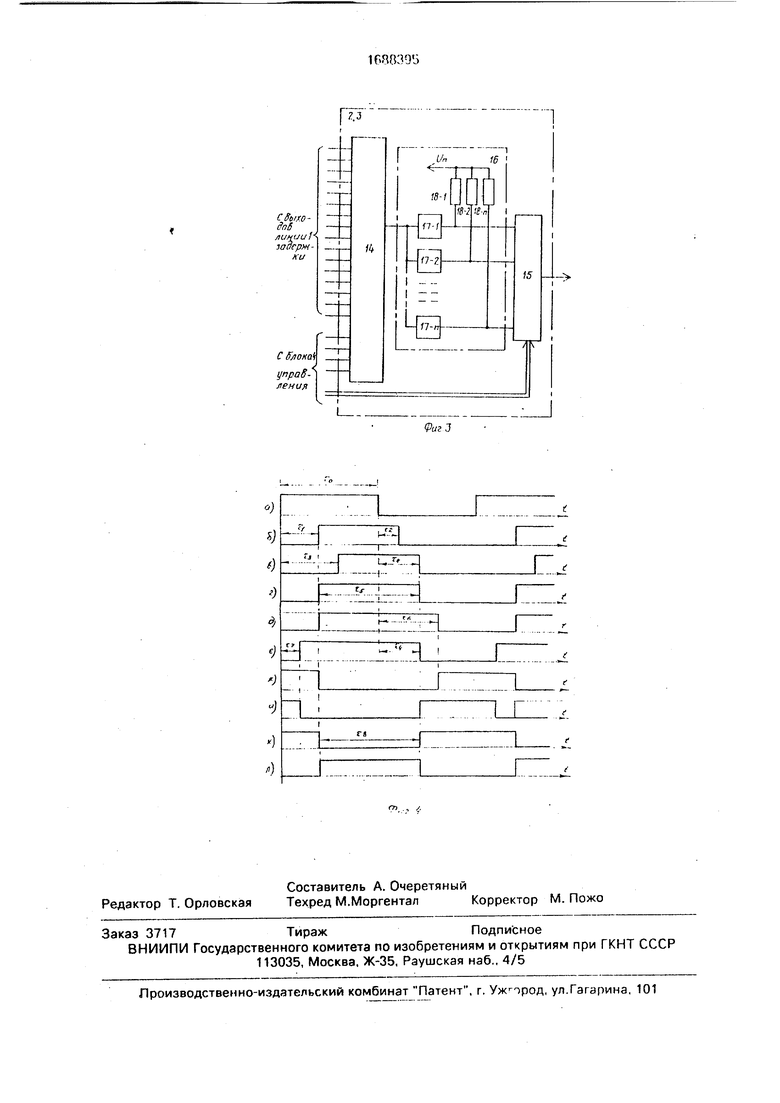

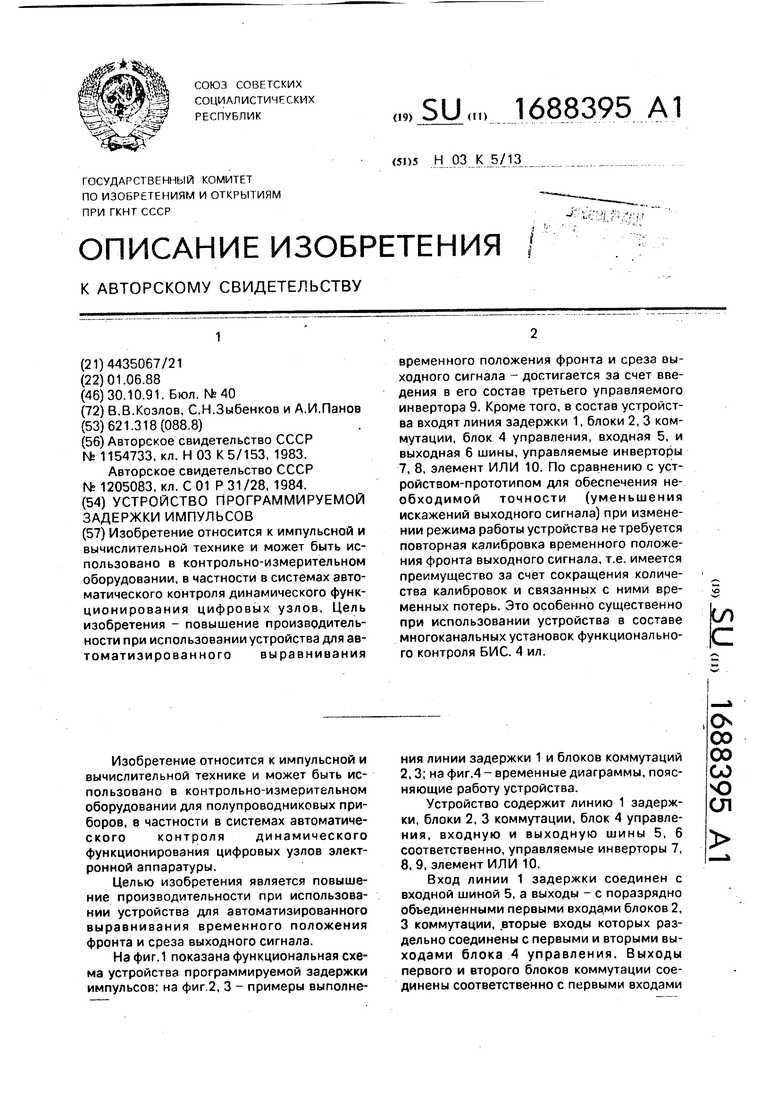

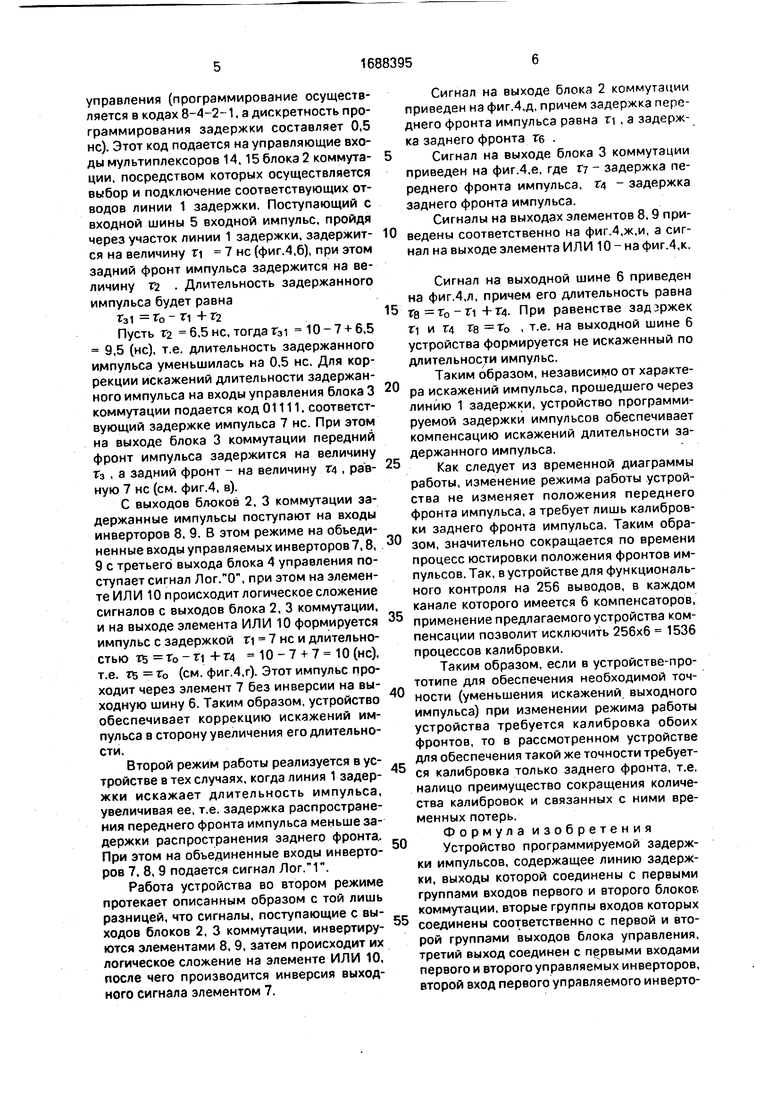

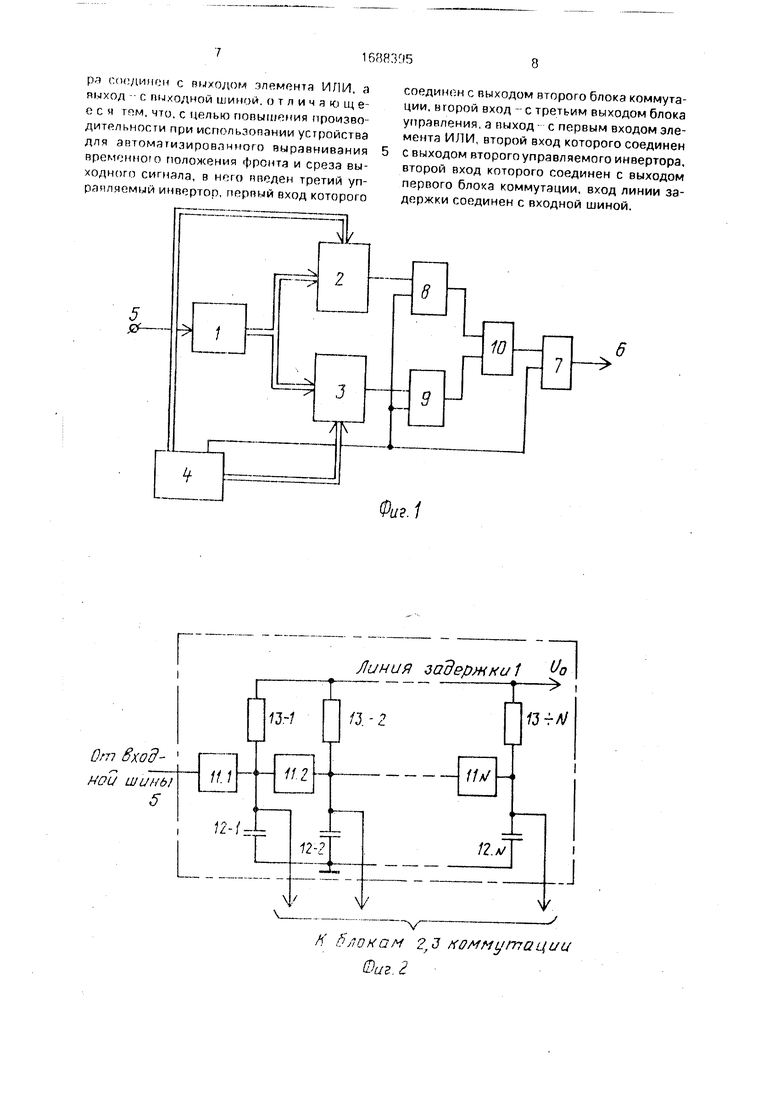

На фиг.1 показана функциональная схема устройства программируемой задержки импульсов; на фиг 2,3- примеры выполнения линии задержки 1 и блоков коммутаций 2, 3; на фиг.4 - временные диаграммы, поясняющие работу устройства.

Устройство содержит линию 1 задержки, блоки 2, 3 коммутации, блок 4 управления, входную и выходную шины 5. 6 соответственно, управляемые инверторы 7, 8, 9, элемент ИЛИ 10.

Вход линии 1 задержки соединен с входной шиной 5, а выходы - с поразрядно объединенными первыми входами блоков 2, 3 коммутации, вторые входы которых раздельно соединены с первыми и вторыми выходами блока 4 управления. Выходы первого и второго блоков коммутации соединены соответственно с первыми входами

о

00 00

со ю ел

второго П и третьего 0 управляемых инпер- торогч. выходы которых соединены с входами элемента ИПИ 10, выход которого соединен п входом первого управляемого инвертора 7, второй вход которого соединен с соответствующими входами второго и третьего управляемых инверторов 8 и 9 и третьим выходом блока управления 4. Вход линии задержки 1 соединен с входной шиной 5, выход управляемого инвертора 7 соединен с выходной шиной 6.

Линия 1 задержки служит для задержки импульса на время, определяемое временем прохождения импульса через заданный участок линии 1. В рассматриваемом примере реализации линия 1 задержки выполнена на N последовательно соединенных буферных элементах 11-1...11-N, нагруженных на конденсаторы 12-1...12-N и резисторы 13-1...13-N (см. фиг.2). Общая точка соединения выхода каждого из буферных элементов 11--1...11-N с первыми выводами соответствующих конденсаторов 12-1...12- N и резисторов 13--1...13-N образует соответствующий отвод линии 1 задержки. Вторые выводы резисторов 13-1...13-N подключены к источнику постоянного напряжения Do, величина которого регулируется в пределах минус 1,8-2,0 В. Количество N буферных элементов определяется временем распространения сигнала через один буферный элемент 11 и требуемым диапазоном изменения задержек.

В рассматриваемом примере для обеспечения диапазона изменения задержек от О до 15 не в качестве буферных элементов 11 использованы микросхемы К1500ЛП122 с типовым временем распространения сигнала через один элемент ( ,9 не), емкость С конденсатора 12 составляет 0-10 пФ, а сопротивление R резистора 68 Ом. Подбором емкостей конденсаторов 12-1...12-N на выходах каждого из буферных элементов 11-1...11-N линии 1 задержки, а также регулировкой напряжения устанавливается время распространения сигнала через один буферный элемент, равное 1 не.

Блоки 2. 3 коммутации предназначены для выбора одного из нескольких сигналов, снимаемых с отводов линии 1 задержки, в зависимости от кодов, поступающих на управляющие входы блоков 2, 3 коммутации с выходов блока 4 управления. Каждый из блоков 2. 3 коммутации (см. фиг.З) выполнен в виде двух мультиплексоров 14. 15 и включенной между ними линии 16 задержки, состоящей из п буферных элементов 17-1.,.17-п. погруженных на резисторы 18- 1...18-П, подключенные к источнику питания lln Линия 1В члдрржки обгм.печиплгм регулировку задержки с дискретностью

г

где тч - задержка импульса через один из буферных элементов 11 1. 11 N линии 1 задержки;

п количество буферных элементов в линиях 16 задержки блоков 2.3 коммутации,

т.е. линия 16 задержки уменьшает дискретность программирования в п раз.

В рассмотреном примере реализации в линии 16 задержки использованы два буферных элемента, обеспечивающих дискретность программирования 0,5 не внутри диапазона. 0-1 не. Блоки 2, 3 коммутации выполнены на микросхемах серии 1500 (мультиплексор 14 - на микросхемах К1500КП164: мультиплексор 15 - на микросхемах К1500КП163, буферные элементы 17- 1.,.17-п линий 16 задержки - на микросхемах К1500ЛП122). Напряжение питания Un 4,5 В. Сопротивление нагрузочных резисторов 18-1...18-п в выходных цепях

буферных элементов 17-1...17-П выбирается в диапазоне от 270 до 1500 Ом.

Блок 4 управления представляет собой оперативное запоминающее устройство, выполненное на микросхемах К155РУ2 и

предназначенное для хранения информации о кодах задержки для блоков 2,3 коммутации и режимах работы устройства с коррекцией длительности импульса в сторону увеличения или уменьшения.

Устройство программируемой задержки импульсов работает следующим образом.

Предварительно из программного устройства (не показано) в оперативное запоминающее устройство блока 4 управления заносится информация: коды задержек импульса и соответствующие им коды коррекции длительности импульса, а также код режима работы устройства.

Если линия 1 задержки искажает длительность входного импульса, уменьшая ее, т.е. задержка распространения переднего фронта импульса больше задержки распространения заднего фронта, то устанавливается первый режим работы, при котором на объединенные (вторые) входы управляемых инверторов 8, 9 из блока 4 управления подается Лог. О, при этом элементы 8, 9, 10, 7 выполняют функцию логического сложения

5 сигналов.

Пусть требуется задержать импульс длительностью Г0 10 не (см. фиг.4,а) на величину ri 7 не. Данной задержке соответствует код 01110, записанный в блоке 4

управления (программирование осуществляется в кодах 8-4- 2-1, а дискретность программирования задержки составляет 0,5 не). Этот код подается на управляющие входы мультиплексоров 14, 15 блока 2 коммутации, посредством которых осуществляется выбор и подключение соответствующих отводов линии 1 задержки. Поступающий с входной шины 5 входной импульс, пройдя через участок линии 1 задержки, задержится на величину ri 7 не (фиг.4,6), при этом задний фронт импульса задержится на величину Г2 . Длительность задержанного импульса будет равна

Г31 Г0 - Г1 Ч- Г2

Пусть Г2 6.5 не, тогда Г31 10-7 + 6,5 9,5 (не), т.е. длительность задержанного импульса уменьшилась на 0.5 не. Для коррекции искажений длительности задержанного импульса на входы управления блока 3 коммутации подается код 01111, соответствующий задержке импульса 7 не. При этом на выходе блока 3 коммутации передний фронт импульса задержится на величину гэ , а задний фронт - на величину Г4 , равную 7 не (см. фиг.4, в).

С выходов блоков 2, 3 коммутации задержанные импульсы поступают на входы инверторов 8, 9. В этом режиме на объединенные входы управляемых инверторов 7,8, 9 с третьего выхода блока 4 управления поступает сигнал Лог.0, при этом на элементе ИЛИ 10 происходит логическое сложение сигналов с выходов блока 2, 3 коммутации, и на выходе элемента ИЛИ 10 формируется импульс с задержкой ri 7 не и длительностью ТВ Г0 - П + Г4 10-7 + 7 10 (не), т.е. тв тг0 (см. фиг.4,г). Этот импульс проходит через элемент 7 без инверсии на выходную шину 6. Таким образом, устройство обеспечивает коррекцию искажений импульса в сторону увеличения его длительности.

Второй режим работы реализуется в устройстве в тех случаях, когда линия 1 задержки искажает длительность импульса, увеличивая ее, т.е. задержка распространения переднего фронта импульса меньше задержки распространения заднего фронта, При этом на объединенные входы инверторов 7, 8, 9 подается сигнал Лог.Г.

Работа устройства во втором режиме протекает описанным образом с той лишь разницей, что сигналы, поступающие с выходов блоков 2, 3 коммутации, инвертируются элементами 8, 9, затем происходит их логическое сложение на элементе ИЛИ 10, после чего производится инверсия выходного сигнала элементом 7.

Сигнал на выходе блока 2 коммутации приведен на фиг.4,д, причем задержка переднего фронта импульса равна ri , а задержка заднего фронта ге .

Сигнал на выходе блока 3 коммутации приведен на фиг.4,е, где г - задержка переднего фронта импульса, Г4 - задержка заднего фронта импульса.

Сигналы на выходах элементов 8, 9 приведены соответственно на фиг.4,ж,и, а сигнал на выходе элемента ИЛИ 10 - на фиг.4,к.

Сигнал на выходной шине 6 приведен на фиг.4,л. причем его длительность равна Га г0-Г1 + Г4. При равенстве задержек ri и г Гв Г0 , т.е. на выходной шине 6 устройства формируется не искаженный по длительности импульс.

Таким образом, независимо от характера искажений импульса, прошедшего через линию 1 задержки, устройство программируемой задержки импульсов обеспечивает компенсацию искажений длительности задержанного импульса.

Как следует из временной диаграммы работы, изменение режима работы устройства не изменяет положения переднего фронта импульса, а требует лишь калибровки заднего фронта импульса. Таким образом, значительно сокращается по времени процесс юстировки положения фронтов импульсов. Так, в устройстве для функционального контроля на 256 выводов, в каждом канале которого имеется 6 компенсаторов, применение предлагаемого устройства компенсации позволит исключить 256x6 1536 процессов калибровки.

Таким образом, если в устройстве-прототипе для обеспечения необходимой точности (уменьшения искажений выходного импульса) при изменении режима работы устройства требуется калибровка обоих фронтов, то в рассмотренном устройстве для обеспечения такой же точности требуется калибровка только заднего фронта, т.е. налицо преимущество сокращения количества калибровок и связанных с ними временных потерь.

Формула изобретения

Устройство программируемой задержки импульсов, содержащее линию задержки, выходы которой соединены с первыми группами входов первого и второго блокое коммутации, вторые группы входов которых соединены соответственно с первой и второй группами выходов блока управления, третий выход соединен с первыми входами первого и второго управляемых инверторов, второй вход первого управляемого инверто5 Гя

0

5

0

5

0

5

0

5

рл соединен с выходом члемента ИЛИ, а выход с nu/одной шиной, отличают е- с с ч тем, что. с целью повышения производительности при использовании устройства для апгомя1изиров,чнного выравнивания временною положения фронта и среза выходного сигнала, в него введен третий уп- раиляемый инвертор, первый вход которого

соединен с выходом второго блока коммутации, второй вход - с третьим выходом блока управления, я выход с первым входом элемента ИЛИ, второй вход которого соединен с выходом второго управляемого инвертора, второй вход которого соединен с выходом первого блоха коммутации, вход линии задержки соединен с входной шиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Устройство подавления шума в канале воспроизведения видеомагнитофона | 1983 |

|

SU1124451A1 |

| СПОСОБ КОГЕРЕНТНОГО НАКОПЛЕНИЯ РАДИОИМПУЛЬСОВ | 2003 |

|

RU2293347C2 |

| Устройство для функционального контроля больших интегральных схем | 1983 |

|

SU1109687A1 |

| Устройство для функционального контроля больших интегральных схем | 1990 |

|

SU1798743A1 |

| УСТРОЙСТВО ФАЗИРОВАНИЯ ШКАЛЫ ВРЕМЕНИ ЭЛЕКТРОННЫХ ЧАСОВ | 1994 |

|

RU2084944C1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| Селектор импульсов по длительности | 1990 |

|

SU1758866A2 |

| УСТРОЙСТВО ЗАДЕРЖКИ ИМПУЛЬСОВ | 2004 |

|

RU2269866C2 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

Изобретение относится к импульсной и вычислительной технике и может быть использовано в контрольно-измерительном оборудовании, в частности в системах автоматического контроля динамического функционирования цифровых узлов. Цель изобретения - повышение производительности при использовании устройства для автоматизированного выравнивания временного положения фронта и среза выходного сигнала - достигается за счет введения в его состав третьего управляемого инвертора 9. Кроме того, в состав устройства входят линия задержки 1, блоки 2, 3 коммутации, блок 4 управления, входная 5, и выходная 6 шины, управляемые инверторы 7, 8, элемент ИЛИ 10. По сравнению с устройством-прототипом для обеспечения необходимой точности (уменьшения искажений выходного сигнала) при изменении режима работы устройства не требуется повторная калибровка временного положения фронта выходного сигнала, т.е. имеется преимущество за счет сокращения количества калибровок и связанных с ними временных потерь. Это особенно существенно при использовании устройства в составе многоканальных установок функционального контроля БИС. 4 ил. СО С

От входной шины 5

А блокам 2,3 коммутации

Оиг I

Фиг.1

Линия задержки 1 р

Г

tfr/V

/2. л/

J

V

С

ijnpaS/IfHUf

| Авторское свидетельство СССР № 1154733 | |||

| кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для автоматического контроля больших интегральных схем | 1984 |

|

SU1205083A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-10-30—Публикация

1988-06-01—Подача