с о

vj

чэ

00

Изобретение относится к контрольно- измерительной технике и может быть использовано для автоматизированного контроля цифровых блоков, включающих в себя большие интегральные схемы.

Цель изобретения - повышение быстро- действия устройства за счет возможности одновременной подачи входных воздействий на объект контроля при помощи двух видов контактирующих приспособлений в различных точках объекта контроля и достоверности контроля за счет возможности Ъд- нозначного определения номера отказавшей микросхемы объекта контроля.

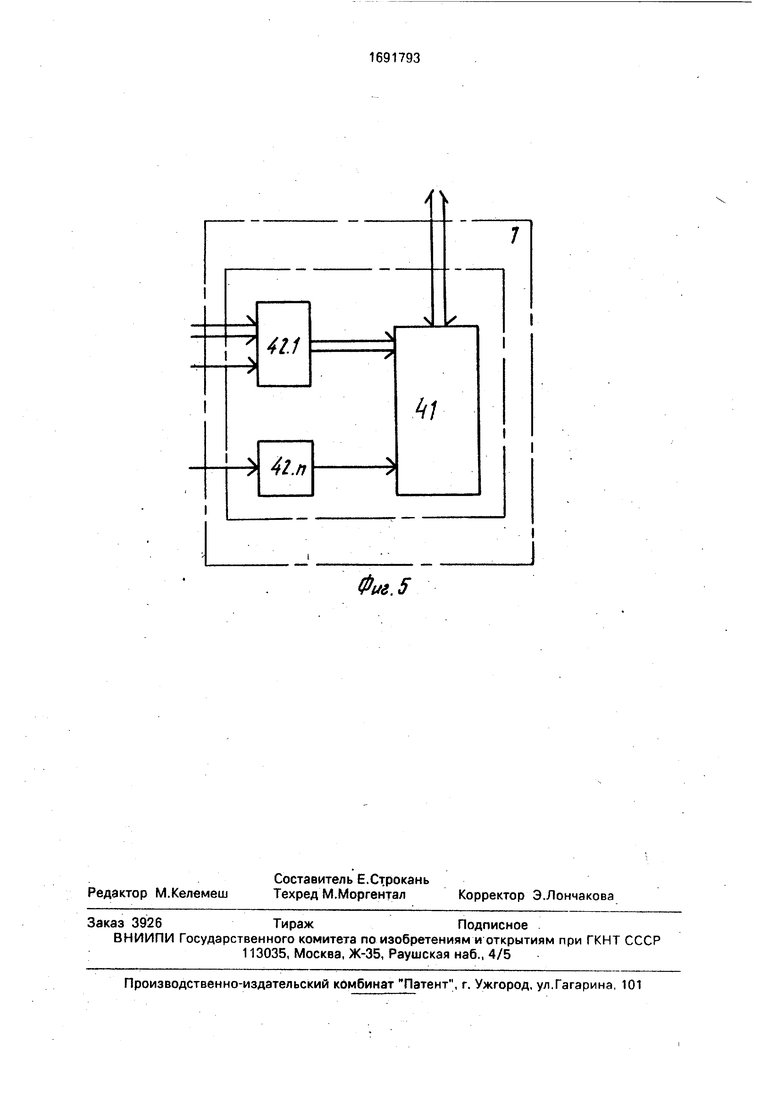

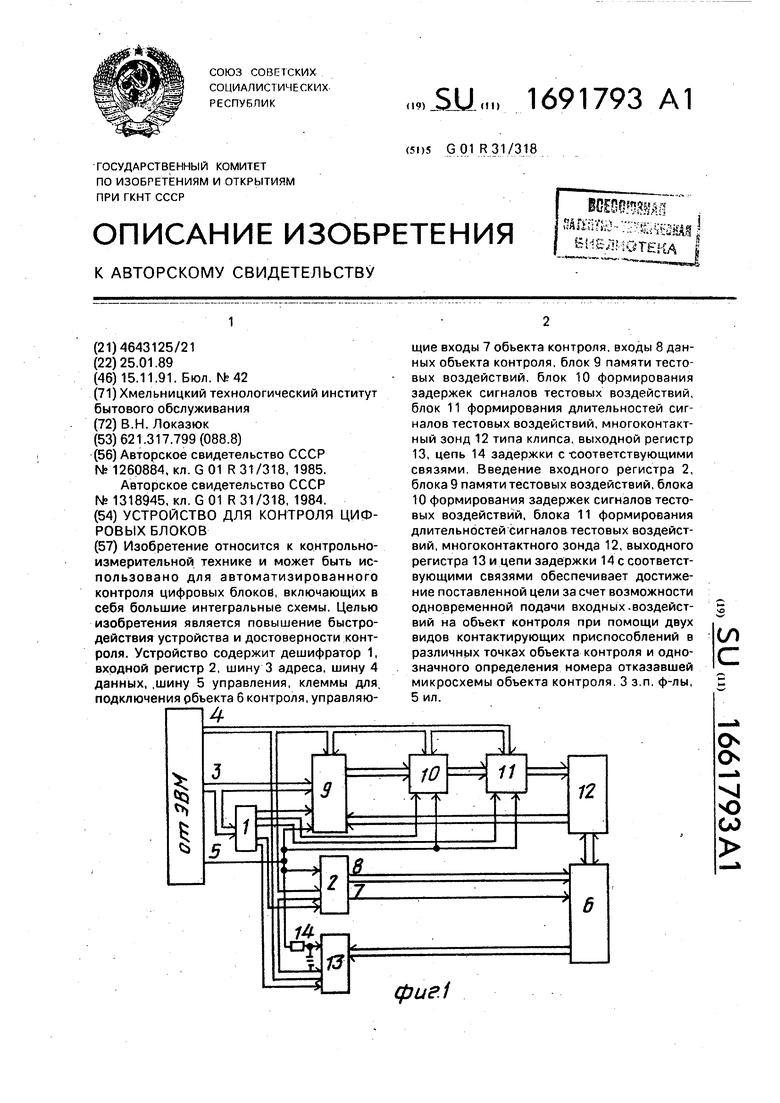

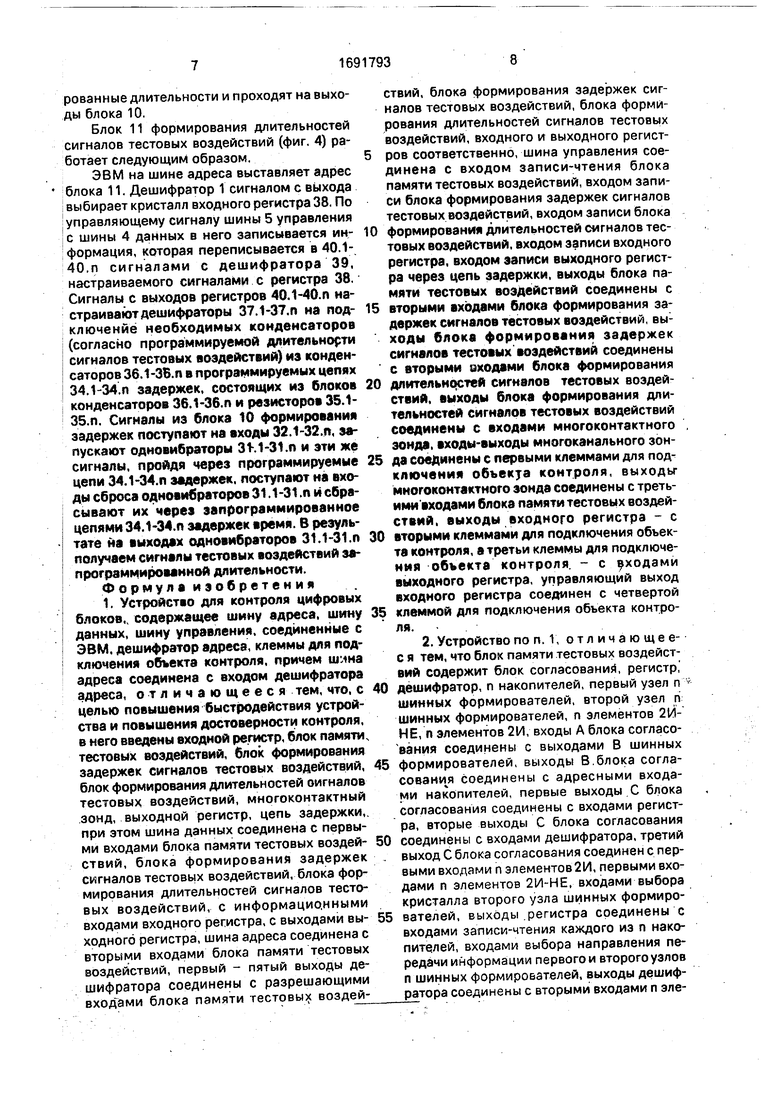

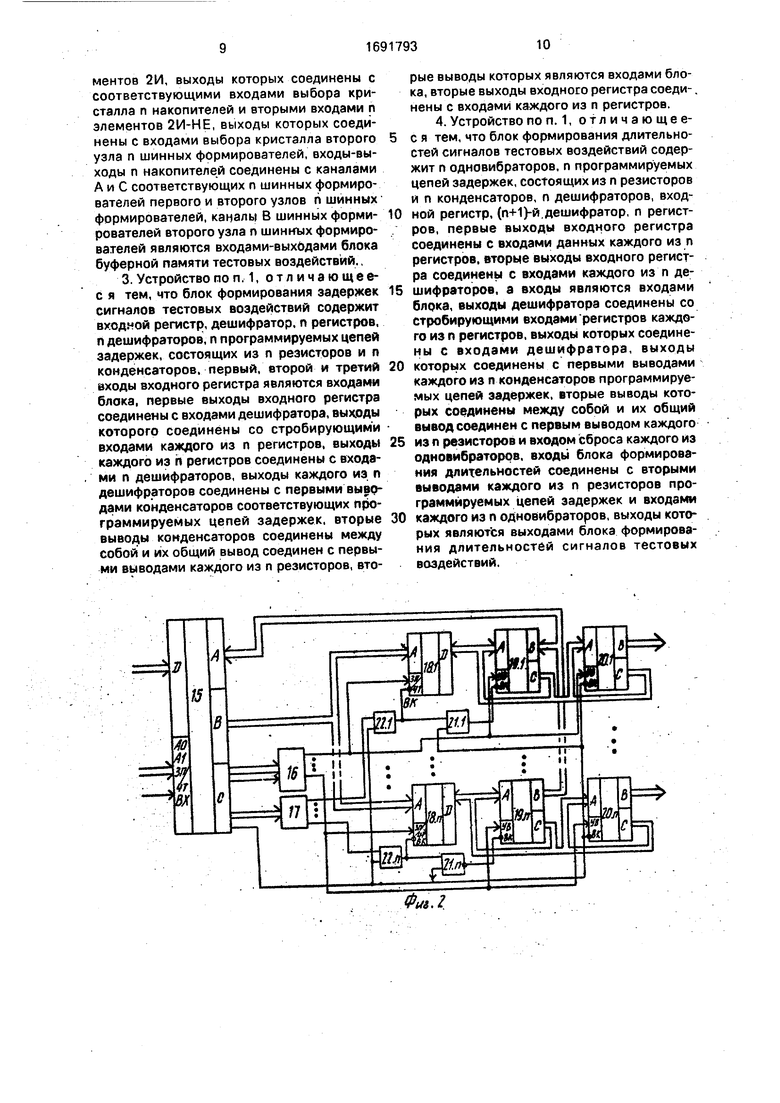

На фиг. 1 приведена блок-схема предложенного устройства; на фиг. 2 - то же. блока памяти тестовых воздействий; на фиг. 3 - то же, блока формирования задержек сигналов тестовых воздействий; на фиг, 4 -то же, блока формирования длительностей сигналов тестовых воздействий; на фиг. 5 - фрагмент объекта контроля.

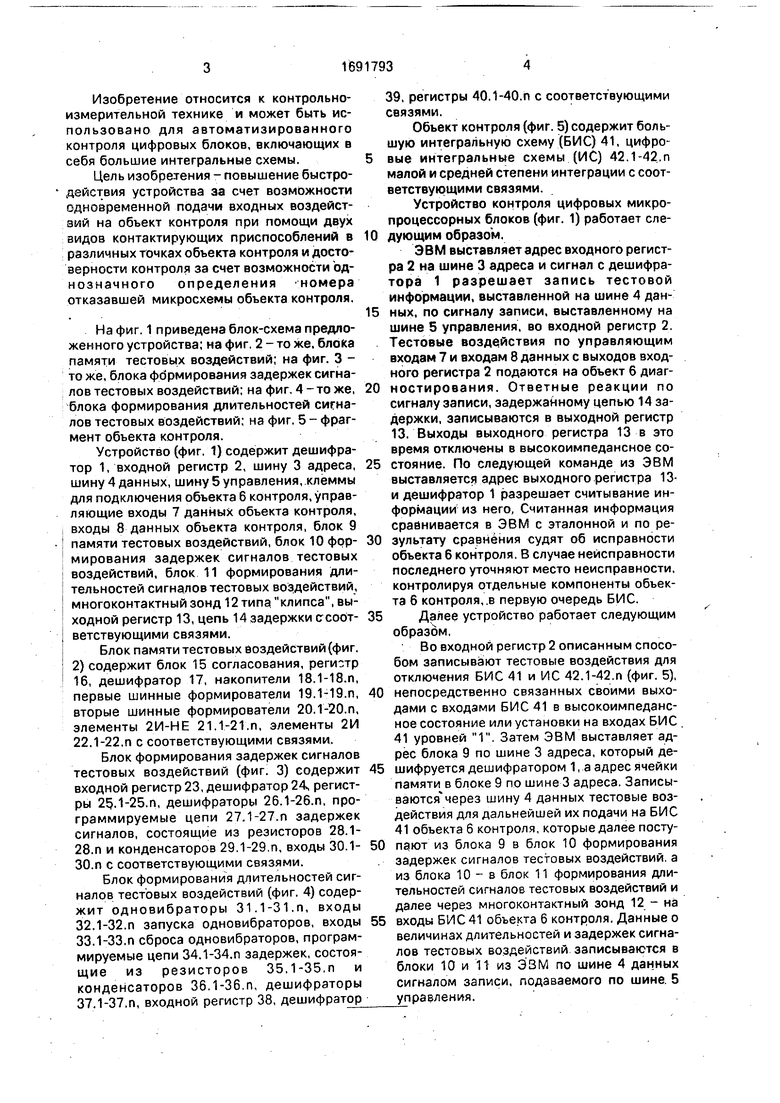

Устройство (фиг. 1} содержит дешифратор 1, входной регистр 2, шину 3 адреса, шину 4 данных, шину 5управления, клеммы для подключения объекта 6 контроля, управляющие входы 7 данных объекта контроля, входы 8 данных объекта контроля, блок 9 памяти тестовых воздействий, блок 10 формирования задержек сигналов тестовых воздействий, блок 11 формирования дли- тельностей сигналов тестовых воздействий, многоконтактный зонд 12 типа клипса, выходной регистр 13, цепь 14 задержки ссоот- ветствующими связями.

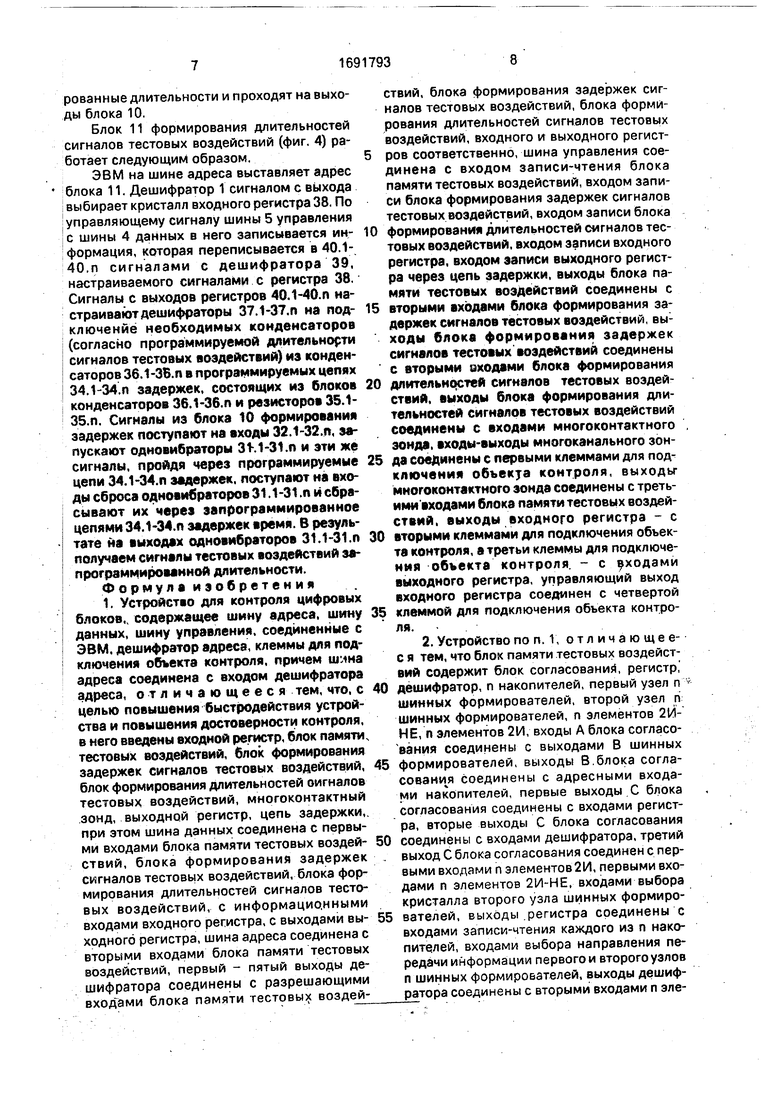

Блок памяти тестовых воздействий (фиг. 2) содержит блок 15 согласования, регистр 16, дешифратор 17, накопители 18.1-18.п, первые шинные формирователи 19.1-19.п, вторые шинные формирователи 20.1-20.п, элементы 2И-НЕ 21.1-21.п, элементы 2И 22.1-22.п с соответствующими связями.

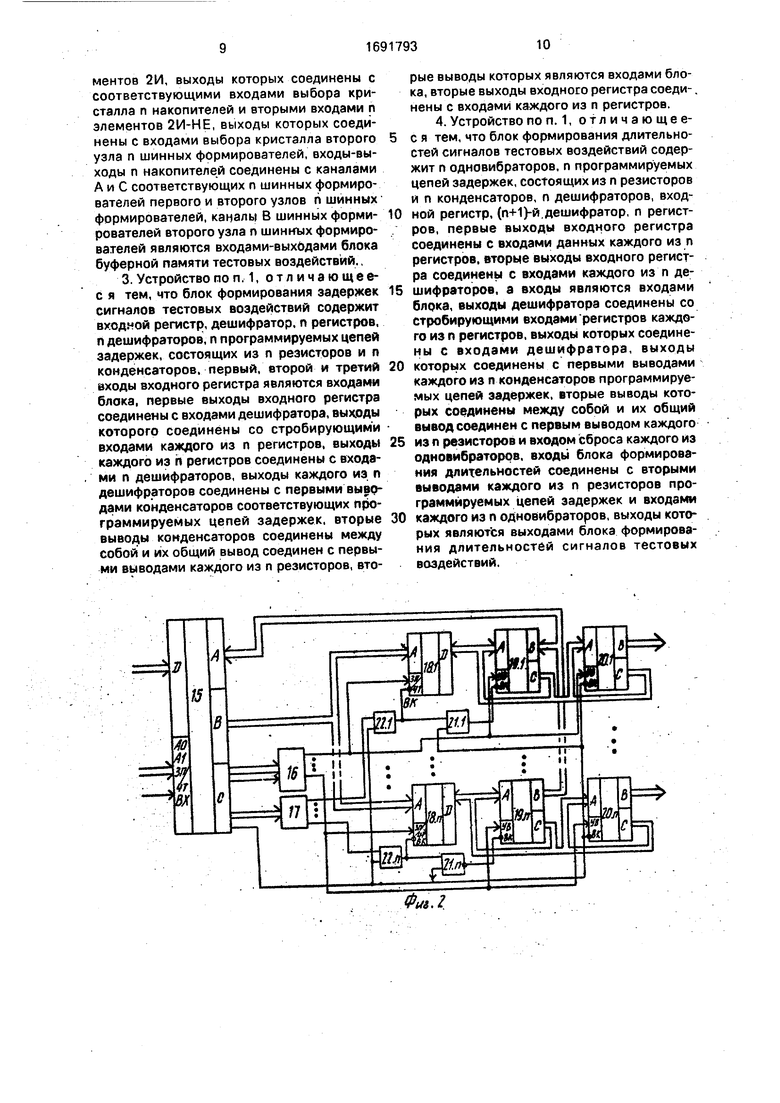

Блок формирования задержек сигналов тестовых воздействий (фиг. 3) содержит входной регистр 23, дешифратор 2 регистры 25-1-25.п, дешифраторы 26.1-26.ri, программируемые цепи 27.1-27.п задержек сигналов, состоящие из резисторов 28.1- 28.п и конденсаторов 29.1-29 п, входы 30.1- 30.п с соответствующими связями.

Блок формирования длительностей сигналов тестовых воздействий (фиг. 4) содержит одновибраторы 31.1-31.п, входы 32.1-32.п запуска одновибраторов, входы 33.1-33.п сброса одновибраторов, программируемые цепи 34.1-34.п задержек, состоящие из резисторов 35.1-35.п и конденсаторов 36.1-36 п, дешифраторы 37.1-37.п, входной регистр 38, дешифратор

39, регистры 40.1-40.п с соответствующими связями.

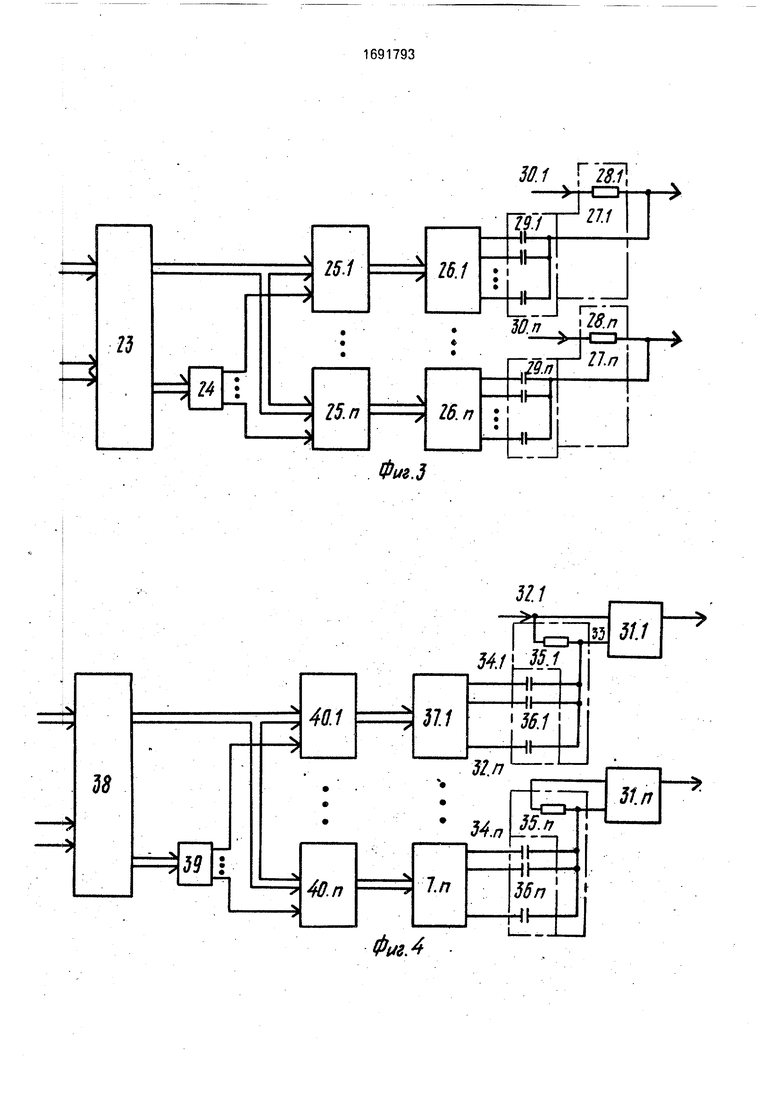

Объект контроля (фиг. 5) содержит большую интегральную схему (БИС) 41, цифровые интегральные схемы (ИС) 42.1-42.п малой и средней степени интеграции с соответствующими связями.

Устройство контроля цифровых микропроцессорных блоков (фиг. 1) работает сле0 дующим образом.

ЭВМ выставляет адрес входного регистра 2 на шине 3 адреса и сигнал с дешифратора 1 разрешает запись тестовой информации, выставленной на шине 4 дан5 ных, по сигналу записи, выставленному на шине 5 управления, во входной регистр 2. Тестовые воздействия по управляющим входам 7 и входам 8 данных с выходов входного регистра 2 подаются на объект 6 диаг0 ностирования. Ответные реакции по сигналу записи, задержанному цепью 14 задержки, записываются в выходной регистр 13. Выходы выходного регистра 13 в это время отключены в высокоимпедансное со5 стояние. По следующей команде из ЭВМ выставляется адрес выходного регистра 13- и дешифратор 1 разрешает считывание информации из него, Считанная информация срайнивается в ЭВМ с эталонной и по ре0 зультату сравнения судят об исправности объекта 6 контроля. В случае неисправности последнего уточняют место неисправности, контролируя отдельные компоненты объекта 6 контроля, в первую очередь БИС.

5 Далее устройство работает следующим образом.

Во входной регистр 2 описанным способом записывают тестовые воздействия для отключения БИС 41 и ИС 42.1-42.п (фиг. 5),

0 непосредственно связанных своими выходами с входами БИС 41 в высокоимпедансное состояние или установки на входах БИС 41 уровней 1. Затем ЭВМ выставляет адрес блока 9 по шине 3 адреса, который де5 шифруется дешифратором 1, а адрес ячейки памяти в блоке 9 по шине 3 адреса. Записываются через шину 4 данных тестовые воздействия для дальнейшей их подачи на БИС 41 объекта 6 контроля, которые далее посту0 пдют из блока 9 в блок 10 формирования задержек сигналов тестовых воздействий а из блока 10 - в блок 11 формирования длительностей сигналов тестовых воздействий и далее через многоконтактный зонд 12 - на

5 входы БИС 41 объекта 6 контроля. Данные о величинах длительностей и задержек сигналов тестовых воздействий записываются в блоки 10 и 11 из ЭВМ по шине 4 данных сигналом записи, подаваемого по шине 5 управления.

Далее ответные реакции с БИС 41 объекта 6 контроля поступают через многоконтактный зонд 12 сначала в блок 9 памяти, а затем ЭВМ считывает их из блока 9 памяти. По результату сравнения в ЭВМ ответных реакций, снятых с выходов БИС 41 объекта 6 контроля, с эталонными реакциями судят об исправности БИС 41 объекта 6 контроля. Описанной методикой определяется исправность и других ИС объекта б контроля.

Блок 9 памяти (фиг. 2) работает следующим образом.

Из ЭВМ выставляется адрес блока 9 и по сигналу из дешифратора 1 адреса разрешается выбор кристалла блока 15 согласо- вания. Подачей информации из ЭВМ по шине 3 адреса, шине 4 данных и шине 5 управления блок 15 согласования программируется в режим для записи информации в каналы А, В, С. Сигналом с канала С блока 15 согласования регистр 16 настраивается на запись. Сигналы с выходов этого регистра устанавливают режим работы (запись или чтение) накопителей 18.1-18.п блока 9 памяти.

Запись информации из ЭВМ посредством блока 15 согласования производится следующим образом.

В канале В блока 15 устанавливается адрес ячейки памяти, в которую необходимо записывать информацию, и сигналы с выходов канала В блока 15 устанавливают на адресных входах накопителей 18.1-18.п адрес. С помощью логических уровней, установленных на выходах регистра 16, задается режим записи для накопителей 18.1-18.п. Информация, поданная на входы дешифратора 17, настраивает его на подачу активного сигнала с его выхода на вход выбора кристилла того из накопителей 18.1- 18.п, в который необходимо записать информацию. Данные, которые необходимо записать в адресованную ячейку памяти избранного накопителя, записываются в канал А блока 15 согласования и поступают из него на входы В избранного идентично накопителю 18.i сигналом из дешифратора 17, который проходит через элемент 2И 22.1, элемент 2И;-НЕ 21.1 первого шинного формирователя 19.1. Сигналом из регистра 16, который настраивает накопитель 18.1 на запись, первый шинный формирователь 19.1 настраивается на передачу информации из канала В в канал С и информация, таким образом, из канала А блока 15 поступает на входы данных накопителя 18.1,и записывается в адресуемую ячейку. Чтение информации из накопителей 18.1-18.п в ЭВМ производится идентичным образом, с тем отличием, что на входе записи/чтения 1-го

накопителя устанавливается сигнал чтения и соответственно i-й первый шинный формирователь настраивается на передачу информации с канала А в канал В.

Чтение тестовых воздействий для подачи на БИС 41 объекта 6 контроля через блоки 10, 11 и многоконтактный зонд 12 происходит следующим образом.

Описанным способом через блок 15 устанавливается адрес ячеек накопителей 18.1-18.п, с которых необходимо считать информацию. Сигналами с регистра 16 накопители из накопителей-18.1-18.п, с которых необходимо считать информацию, настраиваются на чтение. Сигнал из канала С блока 15 разрешает выбор кристаллов всех накопителей 18.1-18.ri и вторых шинных формирователей 20.1-20.п. Этим же сигналом запрещается выбор кристаллов первых шинных формирователей 19.1-19.п. Информация с выходов данных, настроенных на чтение накопителей 18.1-18.П, поступает на входы каналов С вторых шинных формирователей и далее.на выходы В, Запись ответных реакций -с выходов БИС 41 происходит синхронно чтению тестовых воздействий в те накопители, которые с помощью регистра 16 были настроены на запись. Идентично им настраиваются и соответствующие им вторые шинные формирователи из шинных формирователей 20.1-20.п. Информация в таком случае поступает на входы каналов В вторых шинных формирователей и затем с выходов каналов С далее поступает на входы данных накопителей, которые настроены на запись из накопителей 18.1-18.п.

Блок 10 формирования задержек сигналов тестовых воздействий (фиг. 3) работает следующим образом.

ЭВМ по шине 3 адреса выставляет адрес блока 10. Дешифратор 1 сигналом с выхода выбирает кристалл входного регистра 23. По управляющему сигналу шины 5 управлениях шины 4 данных в него записывается информация, которая переписывается в регистры 25.1-25.П сигналами с дешифратора 24, настраиваемого сигналами с регистра 23. Сигналы с выходов регистров 25.1-25.п настраивают дешифраторы 26.1- 26.п на подключение необходимых конденсаторов (согласно программируемым задержкам) из блоков конденсаторов 29.1- 29.п в программируемых цепях 27.1-27.П, состоящих из конденсаторов 29.1-29.п и резисторов 28.1-28.ri. Сигналы из блока 9 буферной памяти поступают на входы 30.1-30.п, задерживаются на запрограммированные длительности и проходят на выходы блока 10.

Блок 11 формирования длительностей сигналов тестовых воздействий (фиг. 4) работает следующим образом.

ЭВМ на шине адреса выставляет адрес блока 11. Дешифратор 1 сигналом с выхода выбирает кристалл входного регистра 38. По управляющему сигналу шины 5 управления с шины 4 данных в него записывается информация, которая переписывается в 40.1- 40.п сигналами с дешифратора 39, настраиваемого сигналами с регистра 38. Сигналы с выходов регистров 40.1-40.П настраивают дешифраторы 37.1-37.п на подключение необходимых конденсаторов (согласно программируемой длительности сигналов тестовых воздействий) из конденсаторов 36.1-ЗБ.п в программируемых цепях 34.1-34.п задержек, состоящих из блоков конденсаторов 36.1-Зб.п и резисторов 35.1- 35.п. Сигналы из блока 10 формирования задержек поступают на входы 32.1-32.it, запускают одновибраторы 31-.1-31.П и эти же сигналы, пройдя через программируемые цепи 34.1-34.П задержек, поступают на входы сброса одновибраторов 31.1-31 .п И сбрасывают их через запрограммированное цепями 34.1-34.п задержек время. В результате йа выходах одновибраторов 31.1-31.0 получаем сигналы тестовых воздействий запрограммированной длительности.

Формула изобретения

1. Устройство для контроля цифровых блоков, содержащее шину адреса, шину данных, шину управления, соединенные с ЭВМ, дешифратор адреса, клеммы для подключения объекта контроля, причем шина адреса соединена с входом дешифратора адреса, отличающееся тем, что, с целью повышения быстродействия устройства и повышения достоверности контроля, в него введены входной регистр, блок памяти, тестовых воздействий, блок формирования задержек сигналов тестовых воздействий, блок формирования длительностей сигналов тестовых воздействий, многоконтактный зонд, выходной регистр, цепь задержки, при этом шина данных соединена с первыми входами блока памяти тестовых воздействий, блока формирования задержек сигналов тестовых воздействий, блока формирования длительностей сигналов тестовых воздействий, с информационными входами входного регистра, с выходами выходного регистра, шина адреса соединена с вторыми входами блока памяти тестовых воздействий, первый - пятый выходы дешифратора соединены с разрешающими входами блока памяти тестовых воздей

ствий, блока формирования задержек сигналов тестовых воздействий, блока формирования длительностей сигналов тестовых воздействий, входного и выходного регистров соответственно, шина управления соединена с входом записи-чтения блока памяти тестовых воздействий, входом записи блока формирования задержек сигналов тестовых воздействий, входом записи блока

0 формирования длительностей сигналов тестовых воздействий, входом записи входного регистра, входом записи выходного регистра через цепь задержки, выходы блока памяти тестовых воздействий соединены с

5 вторыми входами блока формирования задержек сигналов тестовых воздействий, выходы блока формирования задержек сигналов тестовых воздействий соединены с вторыми входами блока формирования

0 длительностей сигналов тестовых воздействий, выходы блока формирования длительностей сигналов тестовых воздействий соединены с входами многоконтактного зонда, входы-выходы многоканального зон5 да соединены с первыми клеммами для подключения объекта контроля, выходы многоконтактного зонда соединены с третьими входами блока памяти тестовых воздействий, выходы входного регистра - с

0 вторыми клеммами для подключения объекта контроля, а третьи клеммы для подключения объекта контроля. - с входами выходного регистра, управляющий выход входного регистра соединен с четвертой

5 клеммой для подключения объекта контроля.

2. Устройство по п. 1, отличающее- с я тем, что блок памяти тестовых воздействий содержит блок согласований, регистр,

0 дешифратор, п накопителей, первый узел п шинных формирователей, второй узел п шинных формирователей, п элементов 2И НЕ, п элементов 2И, входы А блока согласования соединены с выходами В шинных

5 формирователей, выходы В блока согласования соединены с адресными входами накопителей, первые выходы С блока согласования соединены с входами регистра, вторые выходы С блока согласования

0 соединены с входами дешифратора, третий выход С блока согласования соединен с первыми входами п элементов2И, первыми входами п элементов 2И-НЕ, входами выбора кристалла второго узла шинных формиро5 вателей, выходы регистра соединены с входами записи-чтения каждого из п накопителей, входами выбора направления передачи информации первого и второго узлов п шинных формирователей, выходы дешифратора соединены с вторыми входами п элементов 2И, выходы которых соединены с соответствующими входами выбора кристалла п накопителей и вторыми входами п элементов 2И-НЕ, выходы которых соединены с входами выбора кристалла второго узла п шинных формирователей, входы-выходы п накопителей соединены с каналами А и С соответствующих п шинных формирователей первого и второго узлов h шинных формирователей, каналы В шинных форми- рователей второго узла п шинных формирователей являются входами-выходами блока буферной памяти тестовых воздействий,,

3.Устройствопоп.1, отличающее- с я тем, что блок формирования задержек сигналов тестовых воздействий содержит входной регистр, дешифратор, п регистров, п дешифраторов, п программируемых цепей задержек, состоящих из л резисторов и п конденсаторов, первый, второй и третий входы входного регистра являются входами блока, первые выходы входного регистра соединены с входами дешифратора, выходы которого соединены со стробирующими входами каждого из п регистров, выходы каждого из h регистров соединены с входами п дешифраторов, выходы каждого из п дешифраторов соединены с первыми выводами конденсаторов соответствующих п0о- граммируемых цепей задержек, вторые выводы конденсаторов соединены между собой и их общий вывод соединен с первыми выводами каждого из п резисторов, вторые выводы которых являются входами блока, вторые выходы входного регистра соединены с входами каждого из п регистров.

4. Устройство по п. 1, отличающее- с я тем, что блок формирования длительностей сигналов тестовых воздействий содержит п одновибраторов, п программируемых цепей задержек, состоящих из п резисторов и п конденсаторов, п дешифраторов, входной регистр, (гн-1)-й. дешифратор, п регистров, первые выходы входного регистра соединены с входами данных каждого из п регистров, вторые выходы входного регистра соединены с входами каждого из п дешифраторов, а входы являются входами блока, выходы дешифратора соединены со стробирующими входами регистров каждого из п регистров, выходы которых соединены с входами дешифратора, выходы которых соединены с первыми выводами каждого из п конденсаторов программируемых цепей задержек, вторые выводы которых соединены между собой и их общий вывод соединен с первым выводом каждого из п резисторов и входом сброса каждого из одновибраторрв, входы блока формирования длительностей соединены с вторыми выводами каждого из п резисторов программируемых цепей задержек и входами каждого из п одновибраторов, выходы которых являются выходами блока формирования длительностей сигналов тестовых воздействий.

Фм.5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1989 |

|

SU1762280A2 |

| Автоматизированная система тестового контроля и диагностирования цифровых микропроцессорных блоков | 1989 |

|

SU1705782A1 |

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Устройство для записи и контроля программируемой постоянной памяти | 1986 |

|

SU1376121A2 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для функционального контроля цифровых схем | 1987 |

|

SU1583884A1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА ДИАГНОСТИРОВАНИЯ ЦИФРОВЫХ УСТРОЙСТВ | 1994 |

|

RU2097827C1 |

Изобретение относится к контрольно- измерительной технике и может быть использовано для автоматизированного контроля цифровых блоков, включающих в себя большие интегральные схемы. Целью изобретения является повышение быстродействия устройства и достоверности контроля. Устройство содержит дешифратор 1, входной регистр 2, шину 3 адреса, шину 4 данных, ,шину 5 управления, клеммы для. подключения объекта 6 контроля, управляющие входы 7 объекта контроля, входы 8 данных объекта контроля, блок 9 памяти тестовых воздействий, блок 10 формирования задержек сигналов тестовых воздействий, блок 11 формирования длительностей сигналов тестовых воздействий, многоконтактный зонд 12 типа клипса, выходной регистр 13, цепь 14 задержки с-соответствующими связями. Введение входного регистра 2, блока 9 памяти тестовых воздействий, блока 10 формирования задержек сигналов тестовых воздействий, блока 11 формирования длительностей сигналов тестовых воздействий, многоконтактного зонда 12, выходного регистра 13 и цепи задержки 14с соответствующими связями обеспечивает достижение поставленной цели за счет возможности одновременной подачи входных.воздействий на объект контроля при помощи двух видов контактирующих приспособлений в различных точках объекта контроля и однозначного определения номера отказавшей микросхемы объекта контроля. 3 з.п. ф-лы, 5 ил. (Л С

| Способ поиска дефектов в цифровых блоках и устройство для его осуществления | 1985 |

|

SU1260884A1 |

| Автоматизированная система контроля и диагностики неисправностей электронных цифровых блоков | 1984 |

|

SU1318945A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-11-15—Публикация

1989-01-25—Подача