Изобретение относится к контрольно-измерительной технике и может быт использовано для проверки работоспособности, установления неисправносте и определения мест их возникновения в электронных цифровых блоках.

Цель изобретения - повышение быстродействия за счет исключения коммутации входов объекта контроля.

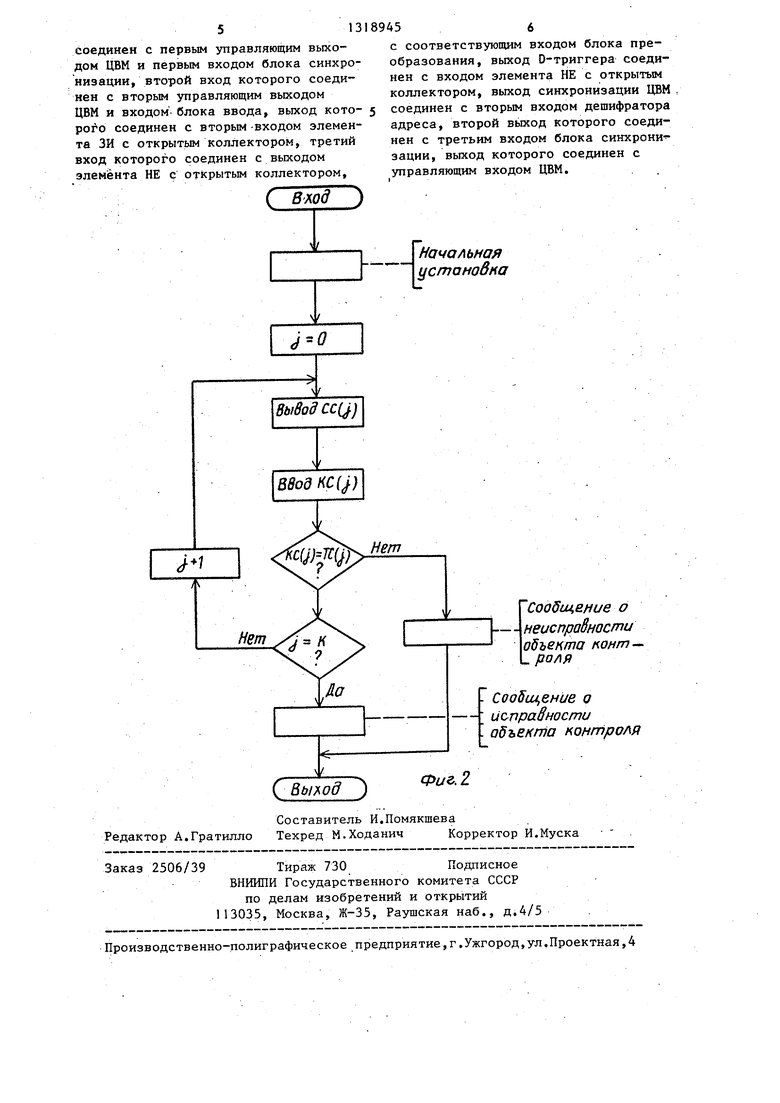

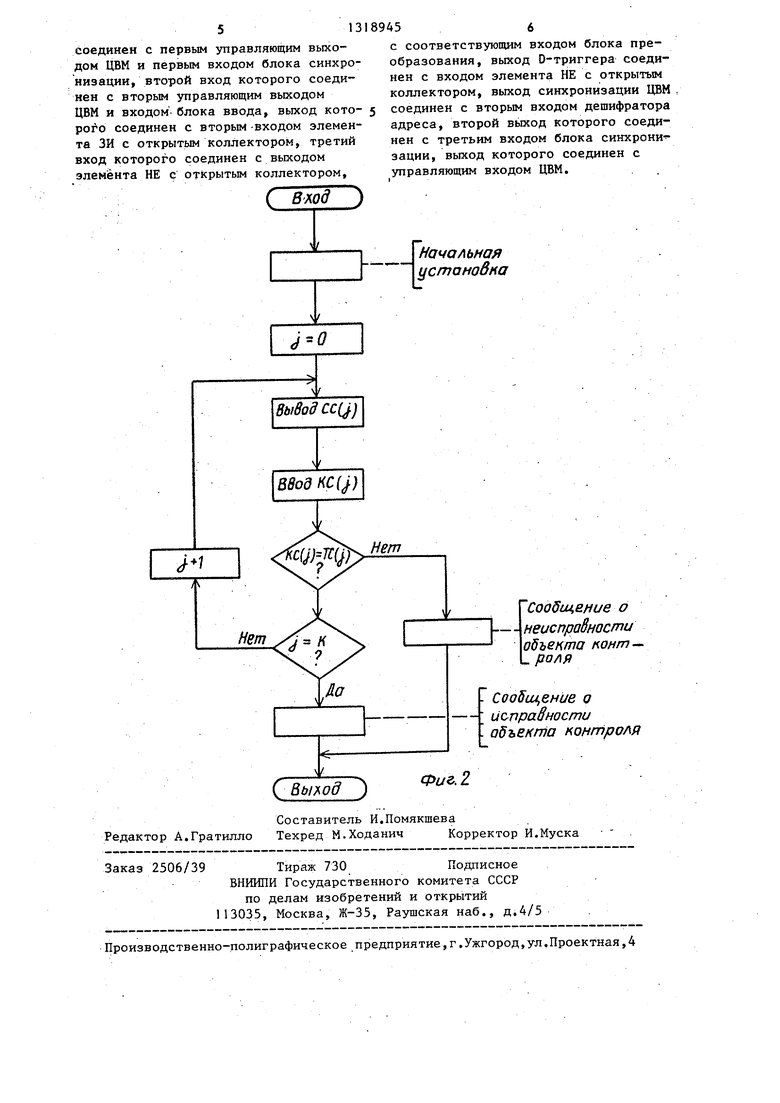

На фиг.1 приведена функциональная схема устройства; на фиг.2 - блок- схема алгоритма функционирования ЦВМ в устройстве.

Устройство содержит ЦВМ, в которую входит процессор 1 с единым двунаправленным каналом 2 передачи данных, блок 3 ввода программ, блок 4 памяти, блок 5 регистрации, блок 6 согласования, блок 7 преобразования, блок 8 контактирования с контактами Х.. .Х .. .X.jj (например, разъем), объект 9 контроля. Блок 6 согласования имеет блок 10 синхронизации, первый и второй входы которого соединены соответственно с первым и вторым управляющими выходами канала 2, а выход - с управляющим входом канала 2, дешифратор П адреса, первым входом соединенный с третьим управляющим выходом канала 2, входами О...п соединенный с входами-выходами О...п канала 2, а N+1 выходом соединенный с третьим входом блока 10 синхронизации, ячейки 12.1-12,N согласования каждая из которых имеет элемент 2И 13.1, элемент ЗИ.14. с открытым коллектором, D-триггер 15.i, и элемент НЕ. 16. i с открытым коллектором, причем первый вход элемента 13.i соединен с одним изО.,.п...Н выходов дешифратора 11 адреса и с первым входом элемента 14.1, выход которого соединен с одним из О...П входов- выходов канала 2 и с входом D-тригге ра 15.1, вход С которого соединен с выходом элемента 13.i, а выход кото- jporo соединен с входом элемента НЕ 16.1, выход которого соединен с соответствующим входом-выходом блока 7 преобразования и с вторым входом элемента 14.1, блок 17 ввода, вход которого соединен с вторым входом

блока 10 синхронизации и с вторым уПравляюпу1М выходом канала 2, а выход которого соединен с третьими входами всех элементов 14.1-14.N, блок 18 вывода, вход которого соединен с первым входом блока 10 синхроO

S

0

5

0

5

0

5

0

5

низации и с первым управляющим выходом канала 2, а выход которого соединен с вторыми входами всех элементов ЗИ 14.i. Линия 19 соединена с одним из О...П входов-вькодов канала 2.

Устройство работает следующим образом.

Объект 9 контроля подключается к блоку 8 контактирования, который обеспечивает электрическую связь между контактами объекта контроля и блоком 7 преобразования. Блок 7 преобразования обеспечивает сбответствие уровней сигналов объекта 9 контроля и блока 6 согласования. Если объект контроля и блок согласования выполнены на совместимых по уровням сигна- лов элементах (например, на микросхемах одного типа логики), блок преобразования не нужен и объект контроля через блок контактирования подключается непосредственно к блоку согласования . Диагностическая программа вводится в блок 4 памяти ЦВМ с помощью блока 3 ввода программ. В соответствии с диагностической программой процессор 1 формирует стимулирующие сигналы, которые поступают че рез канал 2, блок 6 согласования, блок 7 преобразования и блок 8 контактирования на контакты-приемники объекта 9 контроля. Информация с контактов-передатчиков объекта 9 контроля поступает через блок 8 контактирования и блок 7 преобразования на блок 6 согласования. В нужные моменты времени процессор 1 считывает эту информацию с блока 6 согласования.и обрабатывает ее в соответствии с диагно- стиче ской программой. При обнаруже-. НИИ неисправности в объекте контроля На блоке 5 регистрации вьшодится сообщение о неисправности.

В начале диагностической программы производится начальная установка, т.е. на вьгходах всех элементов НЕ 16.1 с открытым коллектором блока 6 согласования устанавливаются высокие уровни сигналов. Это необходимо для того, чтобы контролируемые сигналы с- контактов-передатчиков объекта контроля могли беспрепятственно по- ступат ь на вторые входы элементов ЗИ 14.1.

Далее индексу j присваивается значение нуля (j 0), где j является порядковым номером сигнала в таблицах стимулирующих и тестовых сигналов.

Далее выводится стимулирующий сигнал на входные контакты объекта контроля 4 В скобках указан порядковый номер этого сигнала .из таблицы стимулирующих сигналов.

Вводится контролируемый сигнал с вьпсодньк контактов объекта контроля и сравнивается с i-м тестовым сигна- лсу. При несравнении этих сигналов выводится сообщение о неисправности объекта контроля, при сравнении на объект.контроля выводится очередной стимулирующий сигнал. Если все контролируемые сигналы будут равны соответ10

блок 8 контактирования на нужный контакт объекта 9 контроля. При наличии сигналов на первом и третьем входах блока 10 синхронизации« на его выходе формируется ответный Синхросигнал. Если происходит ввод контролируемого сигнала с объекта 9 контроля, процессор 1 устанавливает сигнал на втором управляющем выходе канала 2. Блок 17 ввода формирует сигнал, поступающий на все ячейки 12.1-12.N согласования. По этому сигналу происходит передача информации с второго входа элемента ЗИ 14.1

ствующим тестовым сигналам,то после вы-f5 ранее выделенной ячейки 12.1 согласо

вода последнего стимулирующего сигнала на объект контроля (К - количество сигналов в таблице стимулирующих сиг налов) выводится сообщение о неисправности объекта контроля.

Все контакты объекта контроля и соответствующие им ячейки 12.1-12.N согласования блока 6 согласования имеют определенные адреса, которые содержатся в диагностической програм ме. Вывод стимулирующего сигнала на объект контроля или ввод контролируемого сигнала с объекта контроля начинается с того, что код адреса нужного объекта контроля устанавливается на входах-выходах О...П канала 2, Этот код поступает на входы 0... п дещифратора 11 адреса. Далее процессор 1 вырабатывает синхросигнал, который с третьего управляющего выхода канала 2 поступает на вход дещифратора 11 адреса. По этому сигналу и в соответствии с кодом адреса

устанавливается и запоминается сигнал на N+1 выходе и на одном из 0... n.,.N вькоде дешифратора 11 адреса. Таким образом выделяется та ячейка 12.1 согласования, к которой подключен нужный контакт объекта контроля. Если происходит вывод стимулирующего сигнала, процессор 1 устанавливает код стимулирующего сигнала на входах выходах О...п канала 2 и сигнал на первом управляющем выходе канала 2. Блок 18 вывода формирует сигнал, поступающий на все ячейки 32.1-12.N согласования. По этому сигналу происходит запись и запоминание информаци с одного из О...П входов-выходов канала 2 в D-триггер ранее вьщеленной ячейки 12.1 согласования. С выхода элемента НЕ 16.i эта информация поступает через блок 7 преобразования.

блок 8 контактирования на нужный контакт объекта 9 контроля. При наличии сигналов на первом и третьем входах блока 10 синхронизации« на его выходе формируется ответный Синхросигнал. Если происходит ввод контролируемого сигнала с объекта 9 контроля, процессор 1 устанавливает сигнал на втором управляющем выходе канала 2. Блок 17 ввода формирует сигнал, поступающий на все ячейки 12.1-12.N согласования. По этому сигналу происходит передача информации с второго входа элемента ЗИ 14.1

0

0

5

0

5

0

5

вания на один из О...П входов-выходов канала 2. При наличии сигналов на втором и третьем входах блока 0 синхронизации на его выходе формируется ответный синхросигнал.

Формула изобретения

Автоматизированная система контроля и диагностики неисправностей электронных цифровых блоков, содержащая ЦВМ, блок регистрации, блок согласования, блок преобразования, входы которого соединены с клеммами для подключения выходов объекта контроля блока контактирования, вход блока регистрации соединен с выходом ЦВМ, отличающаяся тем, что, с целью повышения быстродействия, клеммы для подключения входов объекта контроля блока контактирования соединены с входами блока преобразования, блок согласования содержит блок синхронизации, дешифратор адреса, блок ввода, блок вывода, N ячеек согласования, где N - количество выводов объекта контроля, каждая из которых содержит элемент 2И, элемент ЗИ с открытым коллектором D-триггер и элемент НЕ с открытым коллектором, причем первый вход каждого элемента 2И соединен с. соответствующими первыми выходами дешифратора адреса и с первым входом элемента ЗИ с открытым коллектором, выход каждого из которых соединен с соответствующими входами-выходами ЦВМ, с первыми входами дешифратора адреса и с информационным входом соответствующего D-триггера, синхронизирующий вход которого соединен с выходом соответствующего элемента 2И, второй вход каждого из которых соединен с выходом блока вывода, вход которого

51

соединен с первым управляющим выходом ЦВМ и первым входом блока синхро низации, второй вход которого соединен с вторым управляющим выходом ЦВМ и входом-блока ввода, выход кото рого соединен с вторым -входом элемен та ЗИ с открытым коллектором, третий вход которого соединен с выходом элемента НЕ с открытым коллектором.

С Вмд )

189456

с соответствующим входом блока преобразования, выход D-триггера соединен с входом элемента НЕ с открытым коллектором, выход синхронизации ЦВМ соединен с вторым входом дешифратора адреса, второй выход которого соединен с третьим входом блока синхрони- зации, выход которого соединен с управляющим входом ЦВМ.

С Вы)(од J

Начальная (установка

Соо5щение о неисправности

объекта конт- L роля

Сообщение о испраЗности объекта контроля

Фиг,.2

Составитель И.Помякшева Редактор А.Гратилло Техред М.Ходанич Корректор И.Муска

Заказ 2506/39 Тираж 730Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие,г.Ужгород,ул.Проектная,4

| название | год | авторы | номер документа |

|---|---|---|---|

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА ДИАГНОСТИРОВАНИЯ ЦИФРОВЫХ УСТРОЙСТВ | 1994 |

|

RU2097827C1 |

| Автоматизированная система тестового контроля и диагностирования цифровых микропроцессорных блоков | 1989 |

|

SU1705782A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для сопряжения цифровой вычислительной машины с линиями связи | 1983 |

|

SU1166123A1 |

| Устройство для обмена информацией между аналоговой и цифровой вычислительными машинами | 1990 |

|

SU1755372A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для вывода информации | 1983 |

|

SU1124279A1 |

| Устройство для сопряжения ведущей и N ведомых цифровых вычислительных машин | 1988 |

|

SU1531104A1 |

Изобретение относится к контрольно-измерительной технике. Цель изобретения - повышение быстродействия устройства. Автоматизированная система содержит ЦВМ, включающую процессор ЦВМ 1, канал 2 передачи данных, блок 3 ввода программ и блок 4 памяти. Кроме того, устройство включает блок 5 регистрации, блок 6 согласования, блок 7 преобразования и блок 8 контактирования. Новым в устройстве является вьтолнение блока 6 согласования в виде блока 10 синхронизации, дешифратора 11 адреса, ячеек 12.1.... 12.N согласования, элементов 2И 13.1... 13.i, элементов ЗИ I4.1...l4.i, D- триггеров 15.1...15.1, элементов НЕ 16.1...16., блока 17 ввода и блока 18 вывода. При этом клеммы для подключения входов объекта 9 контроля и блока 8 контактирования соединены с входами блока 7 преобразования. Это позволяет исключить коммутацию входов объекта контроля. 2 ил. ся 00 00 СО 4 сд п Кн Фиг.1

| Устройство для контроля логических блоков | 1977 |

|

SU779943A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Викторов Б.Н., Чурабо Д.Д | |||

| Конструирование контрольно-испытательной аппаратуры для ЭВМ.М.: Машиностроение, 1979, с.32-34. | |||

Авторы

Даты

1987-06-23—Публикация

1984-06-28—Подача