Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники, в синтезаторах частот.

Цель изобретения - повышение надежности работы - достигается за счет обеспечения фиксации сигналов переноса первого и второго программируемых делителей частоты.

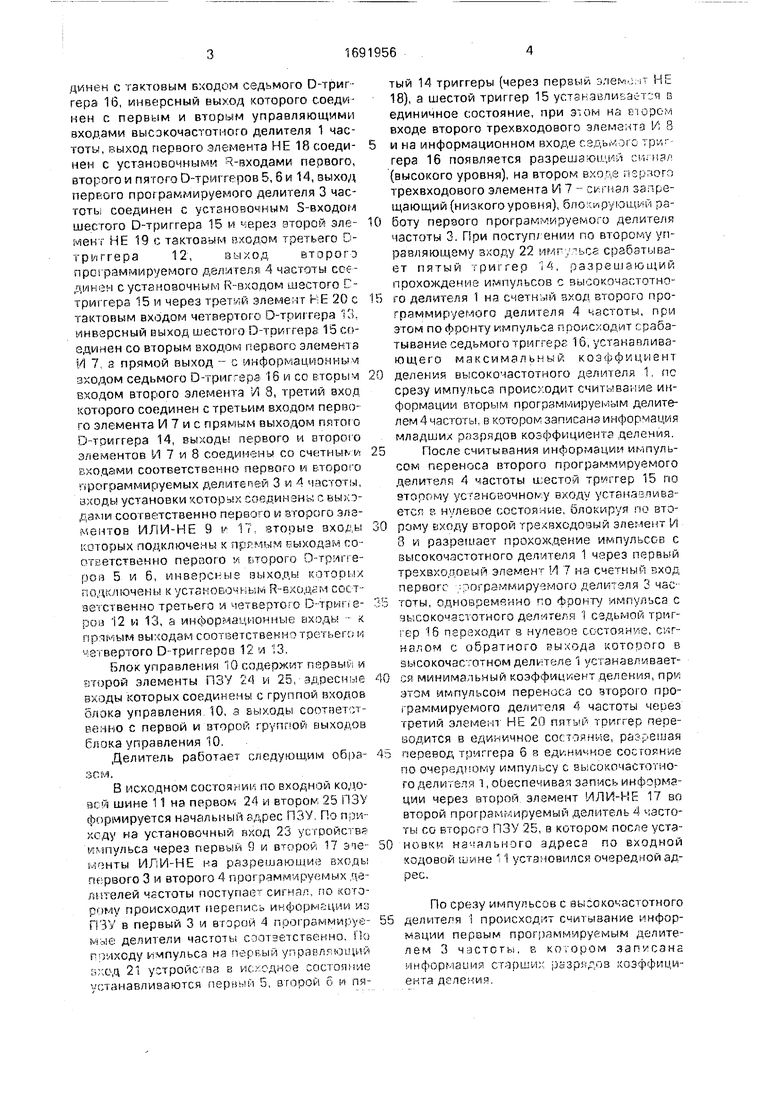

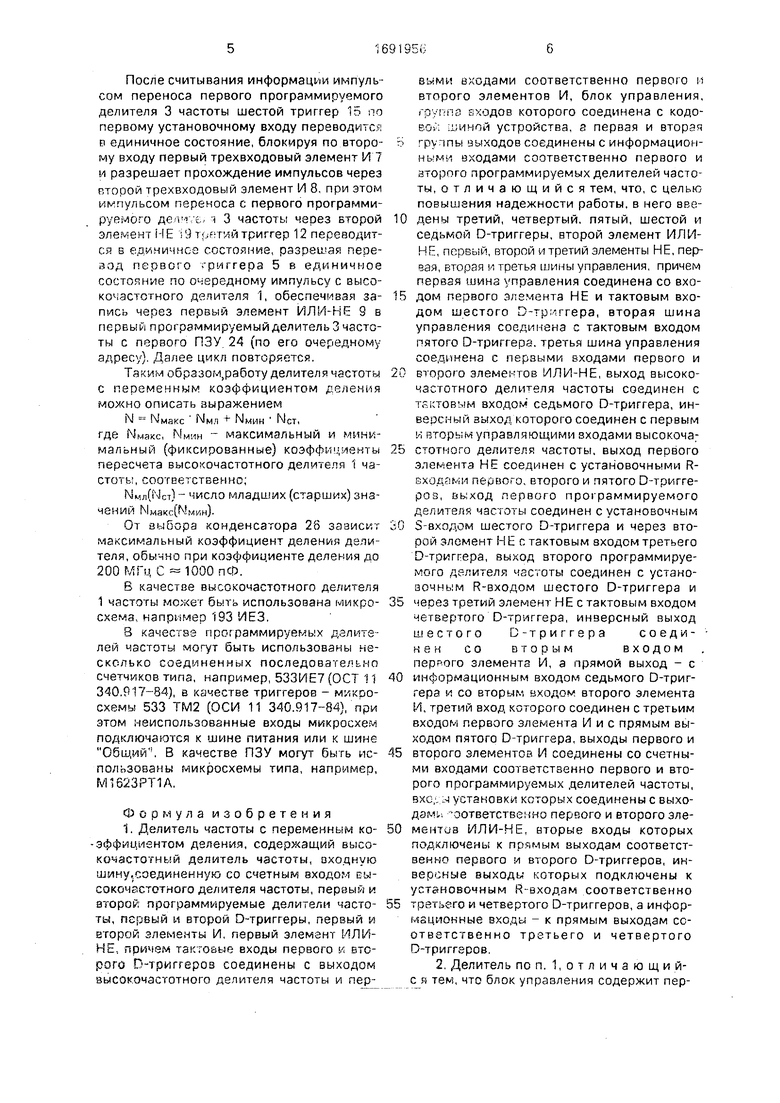

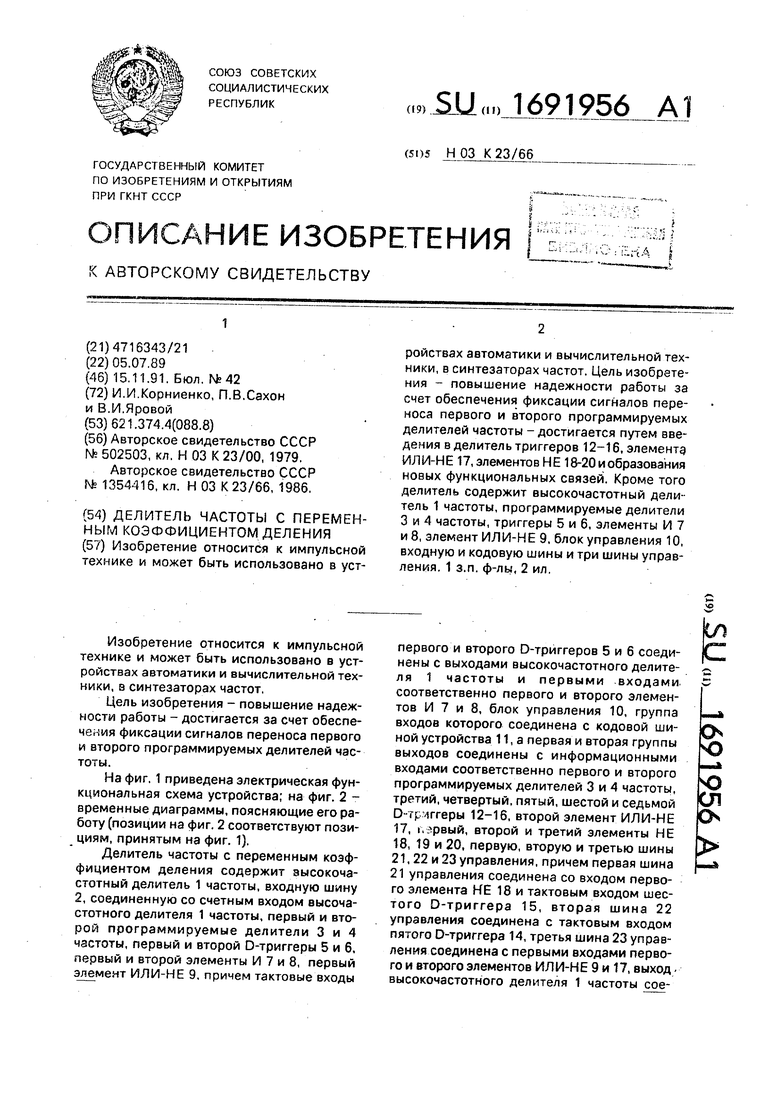

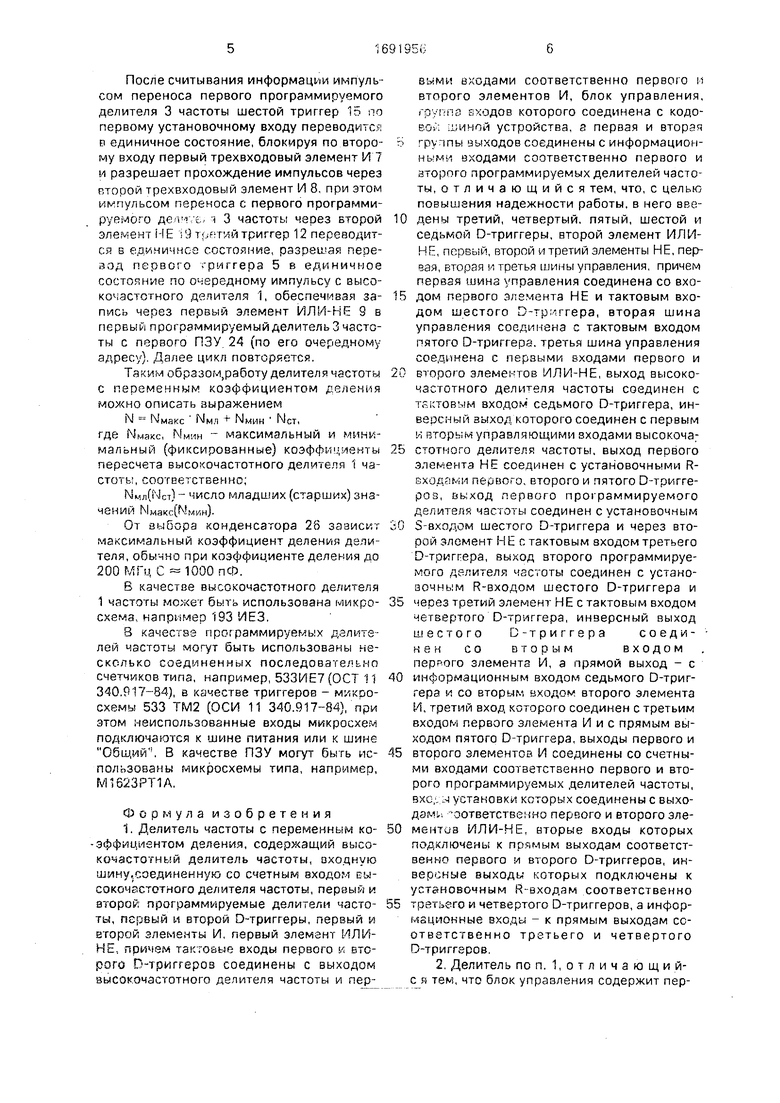

На фиг. 1 приведена электрическая функциональная схема устройства; на фиг. 2 - временные диаграммы, поясняющие его работу (позиции на фиг. 2 соответствуют позициям, принятым на фиг. 1).

Делитель частоты с переменным коэффициентом деления содержит высокочастотный делитель 1 частоты, входную шину 2, соединенную со счетным входом высоча- стотного делителя 1 частоты, первый и второй программируемые делители 3 и 4 частоты, первый и второй Ь-триггеры 5 и 6. первый и второй элементы И 7 и 8, первый элемент ИЛИ-НЕ 9, причем тактовые входы

первого и второго D-триггеров 5 и 6 соединены с выходами высокочастотного делителя 1 частоты и первыми входами соответственно первого и второго элементов И 7 и 8, блок управления 10, группа входов которого соединена с кодовой шиной устройства 11, а первая и вторая группы выходов соединены с информационными входами соответственно первого и второго программируемых делителей 3 и 4 частоты, третий, четвертый, пятый, шестой и седьмой D-триггеры 12-16, второй элемент ИЛИ-НЕ

17,к фвый, второй и третий элементы НЕ

18,19 и 20, первую, вторую и третью шины 21,22 и 23 управления, причем первая шина 21 управления соединена со входом первого элемента НЕ 18 и тактовым входом шестого D-триггера 15, вторая шина 22 управления соединена с тактовым входом пятого D-триггера 14, третья шина 23 управления соединена с первыми входами первого и второго элементов ИЛИ-НЕ 9 и 17, выход высокочастотного делителя 1 частоты соеО

ю ю

СП

о

динен с тактовым входом седьмого D-триг гера 16, инверсный выход которого соединен с первым и вторым управляющими входами высокочастотного делителя 1 частоты, выход первого элемента НЕ 18 соединен с установочными R-входами первого, второго и пятого D-триггеров 5,6 и 14, выход первого программируемого делителя 3 частоты соединен с установочным S-входом шестого D-триггера 15 и через второй элемент НЕ 19с тактовым входом третьего D- триггера 12, выход второго программируемого делителя 4 частоты соединен с установочным R-входом шестого D- триггера 15 и через третий элемент НЕ 20 с тактовым входом четвертого D-триггера 13, инверсный выход шестого D-триггера 15 соединен со вторым входом первого элемента И 7, а прямой выход - с информационным входом седьмого D-триггера 16 и со вторым входом второго элемента И 8, третий вход которого соединен с третьим входом первого элемента И 7 и с прямым выходом пятого D-триггера 14, выходы первого и второго элементов И 7 и 8 соединены со счетными входами соответственно первого и второго программируемых делителей 3 и 4 частоты, входы установки которых соединены с выходами соответственно первого и второго элементов ИЛИ-НЕ 9 и 17, вторые входы которых подключены к прямым выходам соответственно первого и второго D-тригге- ров 5 и 6, инверсные выходы которых подключены к установочным R-входзм соответственно третьего и четвертого D-тригге- ров 12 и 13, а информационные входы - к прямым выходам соответственно третьего и четвертого D-триггеров 12 и 13,

Блок управления 10 содержит первый и второй элементы ПЗУ 24 и 25, адресные входы которых соединены с группой входов блока управления 10, а выходы соответственно с первой и второй группой выходов блока управления 10,

Делитель работает следующим образом.

В исходном состоянии по входной кодовой шине 11 на первом 24 и втором 25 ПЗУ формируется начальный адрес ПЗУ. По приходу на установочный вход 23 устройства импульса через первый 9 и второй 17 элементы ИЛИ-НЕ на разрешающие входы первого 3 и второго 4 программируемых делителей частоты поступает сигнал, по которому происходит перепись информации из ПЗУ в первый 3 и второй 4 программируемые делители частоты соответственно. По приходу импульса на первый управляющий вход 21 устройства в исходное состояние устанавливаются первый 5, агорой б и пятый 14 триггеры (через первый элеми.и НЕ 18), а шестой триггер 15 устанавливается в единичное состояние, при этом на втором входе второго трехвходового элемента Л 3

и на информационном входе седьмого триггера 16 появляется разрешающий ситнзл (высокого уровня), на втором входе первого трехвходового элемента И 7 - сигнал запрещающий (низкого уровня), блокирующий работу первого программируемого делителя частоты 3. При поступлении по второму управляющему входу 22 ир пуьса срабатывает пятый триггер 14, разрешающий прохождение импульсов с высокочастотного делителя 1 на счетный вход второго программируемого делителя 4 частоты, при этом по фронту импульса происходит срабатывание седьмого триггера 16, устанавливающего максимальный коэффициент

деления высокочастотного делителя 1, по срезу импульса происходит считывание информации вторым программируемым делителем 4 частоты, в котором записана информация младших разрядов коэффициента деления.

После считывания информации импульсом переноса второго программируемого делителя 4 частоты шестой триггер 15 по второму установочному входу устанавливается в нулевое состояние, блокируя по второму входу второй трехвходоэый элемент И 8 и разрешает прохождение импульсов с высокочастотного депителя 1 через первый трехвхо,аовый элемент И 7 на счетный вход первого программируемого делителя 3 час-тоты, одновременно по Фронту импульса с аысокочастотного делителя 1 седьмой триггер 16 переходит в нулевое состояние, сигналом с обратного выхода которого в высокочастотном делителе 1 устанавливается минимальный коэффициент деления, при этом импульсом переноса со второго про- фаммируемого делителя 4 частоты через третий элемент НЕ 20 пятый триггер переводится в единичное состояние, разрешая

перевод триггера 6 а единичное состояние по очередному импульсу с высокочастотного делителя 1, обеспечивая запись информации через второй элемент ИЛИ-НЕ 17 во второй программируемый делитель 4 частоты со второго ПЗУ 25, в котором после установки начального адреса по входной кодовой шине 11 установился очередной адрес.

По срезу импульсов с высокочастотного делителя 1 происходит считывание информации первым программируемым делителем 3 частоты, в котором записана информация старших разрядов коэффициента деления.

После считывания информации импульсом переноса первого программируемого делителя 3 частоты шестой триггер 15 по первому установочному входу переводится в единичное состояние, блокируя по второму входу первый трехвходовый элемент И 7 и разрешает прохождение импульсов через второй трехвходовый элемент И 8 при этом импульсом переноса с первого программируемого дс 1 i i } 3 частоты чеоез второй элемент НЕ 19 тр -гий триггер 12 переводится в единичное состояние, разрешая перевод первою триггера 5 в единичное состояние по очередному импульсу с высокочастотного депителя 1, обеспечивая запись через первый элемент ИЛИ-НЕ 9 в первый программируемый делитель 3 частоты с первого ПЗУ 24 (по его очередному адресу) Далее цикл повторяется.

Таким образом,работу делителя частоты с переменным коэффициентом деления можно описать выражением

N Ммакс NM,I + NMHH NCT,

где Ммахс, NMHH - максимальный и минимальный (фиксированные) коэффициенты пересчета высокочастотного делителя 1 частоты, соответственно,

Ымл(Мст) - число младших (старших) значении Ммакс().

От выбора конденсатора 28 зависит максимальный коэффициент деления делителя, обычно при коэффициенте деления до 200МГц С 1000nCD.

Б качестве высокочастотного делителя 1 частоты мохет быть использована микросхема, например 193 ИЕЗ.

В качестве программируемых делитеей частоты могут быть использованы несколько соединенных последовательно четчиков типа, например, 533ИЕ7 (ОСТ 11 340.9 Г/-84), в качестве триггеров - микросхемы 533 ТМ2 (ОСИ 11 340.917-84), при этом неиспользованные входы микросхем подключаются к шине питания или к шине Общий, В качестве ПЗУ могут быть использованы микросхемы типа, например, М1623РТ1А.

Формула изобретения 1. Делитель частоты с переменным коффициентом деления, содержащий высокочастотный делитель частоты, входную шичу.соединенную со счетным входом выокочастотного делителя частоты, первый и горой программируемые делители частоы, первый и второй D-триггеры, первый и торой элементы И, первый элемент ИЛИ- Е причем тактовые входы первого к втоого D-триггеров соединены с выходом ысокочастотного делителя частоты и первыми входами соответственно первою и второго элементов И, блок управления, гр- гпл БХОДОВ которого соединена с кодо- вои пичой устройства, а первая и вторая - rpv-щы выходов соединены с информационными входами соответственно первого и второго программируемых делителей частоты, отличающийся тем, что, с целью повышения надежности работы, в него вве- 10 дены третий, четвертый, пятый, шестой и седьмой D-триггеры, второй элемент ИЛИ- НЕ, первый, второй и третий элементы НЕ, первая, вторая и третья шины управления, причем первая шинз управления соединена со вхо- 15 дом первого элемента НЕ и тактовым входом шестого D-триггера, вторая шина управления соединена с тактовым входом пятого D-триггера, третья шина управления соединена с первыми входами первого и

0 второго элементов ИЛИ-НЕ, выход высокочастотного делителя частоты соединен с тестовым входом седьмого D-триггера, инверсный выход которого соединен с первым к вторым управляющими входами высокоча5 статного делителя частоты, выход первого элемента НЕ соединен с установочными R- оходамм первого, второго и пятого D-тригге- pos, сыход первого npoi раммируемого делителя частоты соединен с установочным

0 S-входом шестого D-триггера и через второй элемент НЕ с тактовым входом третьего D-триггера, выход второго программируемого делителя частоты соединен с устано- аочным R-входом шестого D-триггера и

5 чеоез третий элемент НЕ с тактовым входом четвертого D-триггера, инверсный выход шестого D-триггера соеди- нем со вторымвходом

первого элемента И, а прямой выход - с

0 информационным входом седьмого D-триггера и со вторым входом второго элемента И, третий вход которого соединен с третьим входом первого элемента И и с прямым выходом пятого D-триггера. выходы первого и

5 второго элементов И соединены со счетными входами соответственно первого и второго программируемых делителей частоты, вхс, ы установки которых соединены с выходами ответственно первог о и второго эле0 ментив ИЛИ-НЕ, вторые входы которых подключены к прямым выходам соответственно первого и второго D-триггеров, инверсные выходы которых подключены к установочным R-входам соответственно

5 третьего и четвертого D-триггеров, а информационные входы - к прямым выходам соответственно третьего и четвертого D-триггеров

2. Делитель поп. 1,отличающий- с я тем, что блок управления содержит первый и второй постоянные запоминающие устройства, адресные входы которых соединены с группой входов блока управления,

а выходы соответственно с первой -л второй группой выходов блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с переменным коэффициентом деления | 1986 |

|

SU1354416A1 |

| Программируемый многоканальный формирователь серий импульсов | 1991 |

|

SU1775846A1 |

| СЕЛЕКТОР ИНФОРМАЦИОННЫХ ИМПУЛЬСОВ | 1990 |

|

RU2042266C1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| ЧАСТОТОМЕР ДЛЯ ЭНЕРГОСИСТЕМ И ЭЛЕКТРОСТАНЦИЙ ЕРМАКОВА-ФЕДОРОВА (ВАРИАНТЫ) | 2007 |

|

RU2362174C1 |

| Устройство генерации импульсов управления шаговым двигателем с электронной коррекцией | 1991 |

|

SU1829022A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Умножитель частоты следования импульсов | 1988 |

|

SU1547050A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники, в синтезаторах частот. Цель изобретения - повышение надежности работы за счет обеспечения фиксации сигналов переноса первого и второго программируемых делителей частоты - достигается путем введения в делитель триггеров 12-16, элемента ИЛИ-НЕ 17, элементов НЕ 18-20 и образования новых функциональных связей. Кроме того делитель содержит высокочастотный делитель 1 частоты, программируемые делители 3 и 4 частоты, триггеры 5 и 6, элементы И 7 и 8, элемент ИЛИ-НЕ 9, блок управления 10, входную и кодовую шины и три шины управления. 1 з.п. ф-лы, 2 ил.

Фиг 2

(pue.i

Выход 1 Вход 21 Вход 23 Вход 22

Выход44 Выход 5

Выход Ц, Выход 6 Выход 13

Выход 16

ВходУЗ Вход СЗ ВыходЗ Вход V4 ВходС4 Выходб

| Делитель частоты с переменным коэффициентом деления | 1974 |

|

SU502503A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Делитель частоты с переменным коэффициентом деления | 1986 |

|

SU1354416A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-11-15—Публикация

1989-07-05—Подача