(Л

С

Изобретение относится к вычислительной .технике, предназначено для реализации узлов и устройств цифровых у}.|ч и;литель ых машин методами интегральной технологии со средним и боль i(Hr.; уровнями интеграции и является дооо.-ппгге. ьным к авт.ев, № 1062688.

Целью изобретения являе тся расйш- peiiHe функциональных возможностей модуля за Счет выполнения функции арийиметического сложения двух двоичных: операндов.

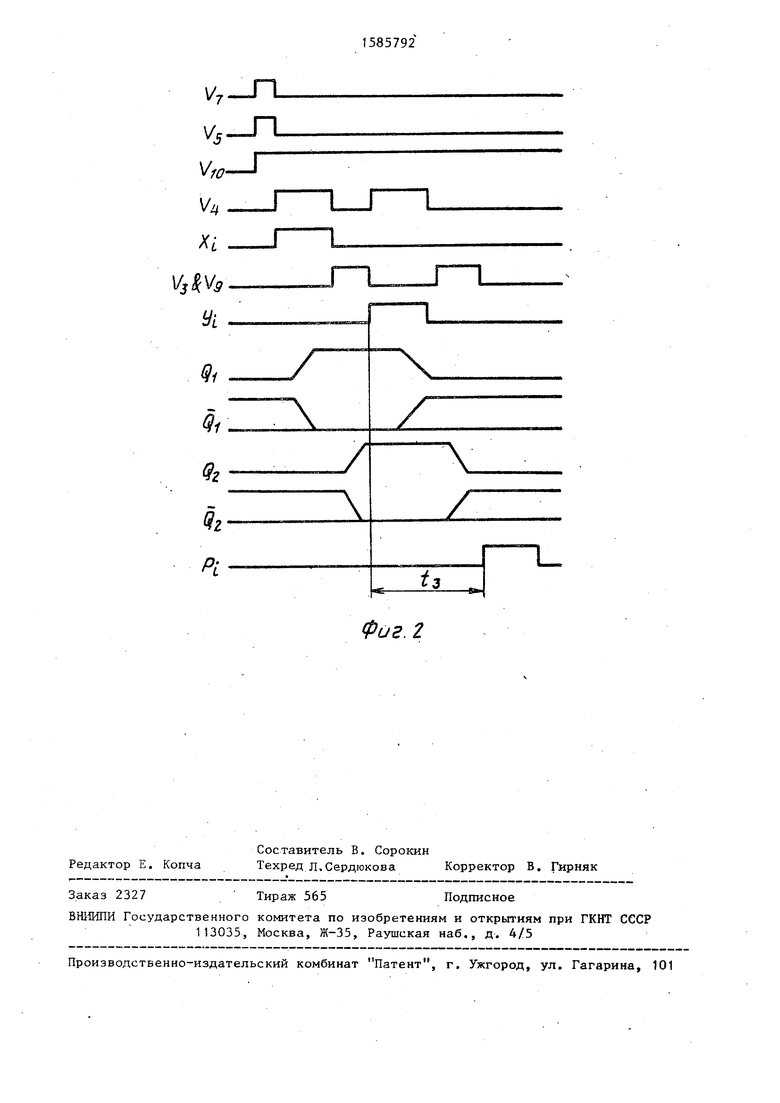

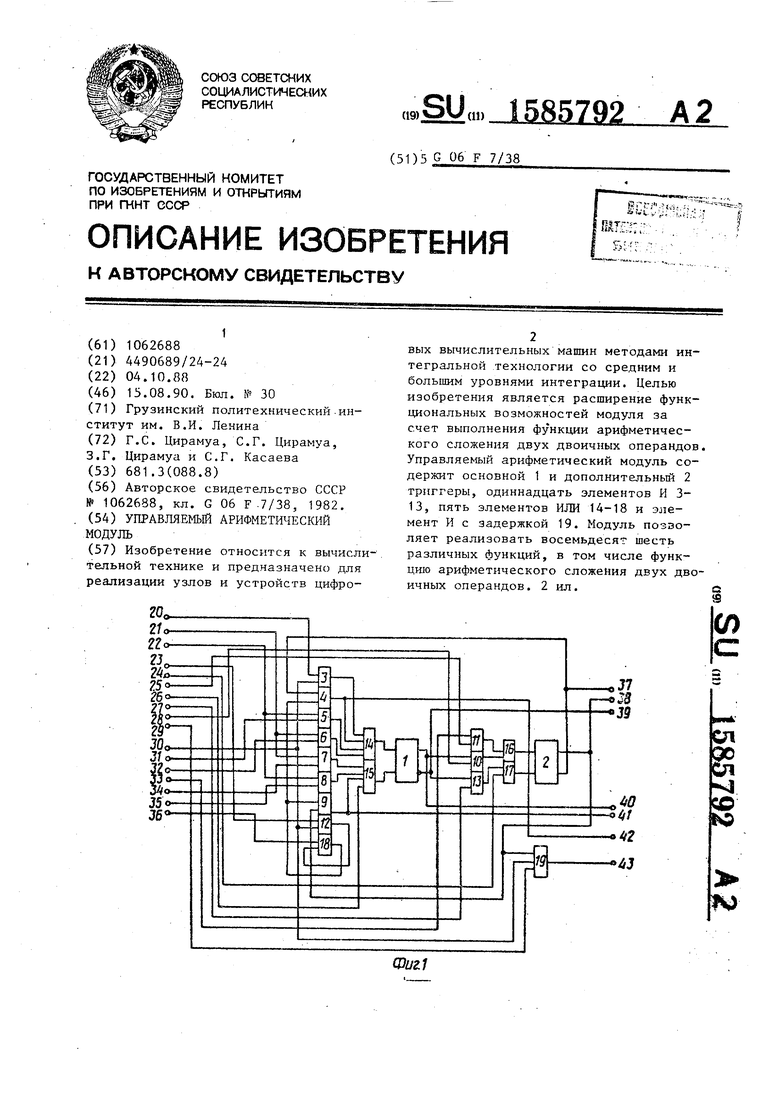

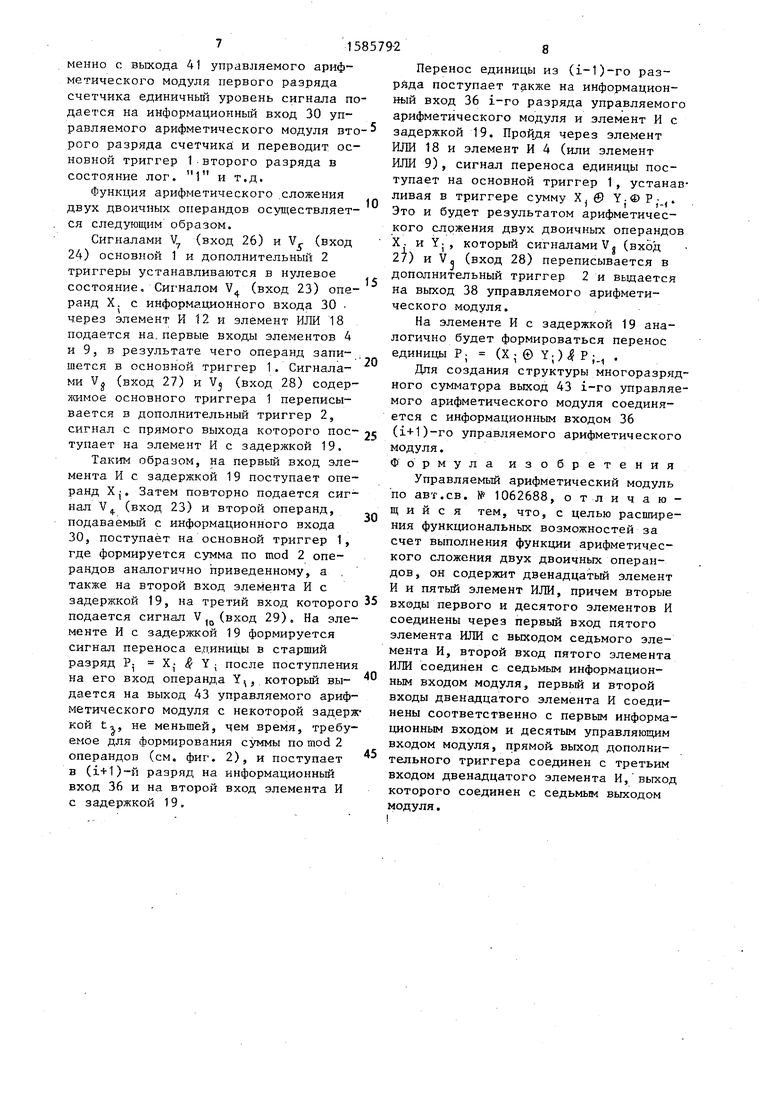

Па фиг„ 1 представлена функциональная схема управляемого арифмети- ческого модуля; на фиг, 2 - временные диаграммы работы управляемого арифметического модуля в режиме арифметического суммирования двух двоичных операндов.

Угфавляемый арифметический модуль (фиг« 1) содержит основной 1 и допол- млтольиый 2 триггеры, одиннадцать эле менто)з И 3-13, пять элементов ИЛИ 14- 18, --элемент И с задержкой 19, управ- ляющие входы 20-29, информационные входы 30-36,, выходы 37-43.

На управляю1 ;ие и информационные входы управляемого арифметического модуля подаются следующие сигналы: V, управляющие сигналы (управля- юн1,ие входы 20-29 содтветственно);. X j-i - разряд кода X (информационный вход 30); Q ;, - содержимое соседнего старшего разряда (информационный вход 31); Qj - содержимое соседнего младшего разряда (информационный вход 32); Y j-i - разряд кода Y (информационный вход 33); Qj - содержимое соседнего младшегр разряда (информацион ньш вход 34); Qj, - содержимое соседнего старшего разряда (информаци- О1П1ЫЙ вход 35); Р ; - перенос единиц из соседнего младшего разряда (информационный вход 36),

Сигналы V , - V р обеспечивают выполнение следующих операций: V, (вход

20)- прием операнда в основной триггер 1 и логическое сложение; УЗ (вход

21)- сдвиг в сторону старших разрядов; V (вход 22) - сдвиг в сторону младпшх разрядов: V (вход 23) - сложение по mod 2; Vj (вход 24) - обнуление дополнительного триггера 2; V (вход 25) - прием операнда в дополнительный, триггер 2; Vj (вход 26) - об- нуление основного триггера 1; Vj (вход 27) - конъюнкция содержимьЕх основного 1 и дополнительного 2 триг

0

0

s

5

50 5

0

45

геров; Vg (вход 28) - дизъюнкция содержимых основного 1 и дополнительного 2 триггеров; V (вход 29) т арифметическое сложение двух двоичных операндов . .

С помощью управляемого арифметического модуля реализуются все шестнадцать функций булевой алгебры двух переменных, некоторые функции трех и четырех переменных, функции двух самостоятельных регистров, функция двухступенчатого регистра, функция преобразования параллельного кода в последовательный и обратно, функция реверсивного регистра сдвига числа, функция двоичного суммирующего или вычитающего счетчика, функция циклического реверсивного регистра сдвига, функция параллельного сумматора с последовательным переносом, функция распространения единицы, нуля и другие.

Используя два и более управляемых арифметических модуля, можно реализовать и более сложные функции, в частности функции схем контроля, функции сравнения кодов, функции дешифратора, шифратора, коммутатора каналов, функции преобразования кода Грея в двоич- ньй и наоборот и другие,

С помощью управляемого арифметического модуля реализуются -как сингулярные булевые функции и функции двух переменных, так и функции трех, четырех и более переменных.

Функция поразрядной конъюнкции двух двоичных чисел выполняется следующим образом.

Операнд Y , подается на четвертый информационный вход 33 и сигналом V (вход 25) через элемент И 11 и элемент ШШ 16 заносится в дополнительный триггер 2. Операнд X. подается на информационньй вход 30, и сигналом V (вход 20) через элемент И 3 . и элемент ИЛИ 14 заносится в основной триггер 1. Предварительно основной 1 и дополнительный 2 триггеры соответственно сигналами V (вход 26) и V (вход 24) устанавливаются в нулевое состояние. Дпя осуществления операции конъюнкции подается управляющий сигнал Vg (вход 27) и содержимое основного триггера 1 с инверсного вьпсода через элементы И 13 и ИЛИ 17 перепи- сьюается в дополнитель йый триггер 2. В результате в дополнительном триггере 2 (выход 38) устанавливается логическое произведение.

Последовательность выполнения функции поразрядной дизъюнкции аналогична предыдущему, но вместо сигнала Vg (вход 27) следует подать сигнал V (вхЪд 28).

Функция поразрядной дизъюнкции реализуется также при подаче управляющи сигналов V/ (вход 20) и V (вход 25). Прямые коды .X и Y. подаются на информационные входы 30 и 33 и через элементы И 3, ИЛИ 14, И 11, ИЛИ 16 подаются на вход установки S единицу основного 1 и дополнительного 2 триггеров, В результате в основном триггере 1 реализуется функция X j X , а в дополнительном триггере 2 функция Y, V Y . , где X . и Y - содержимое основного 1 и дополнительного 2 триггеров, т.е. третья и четвертая переменные. Далее можно получить (Х,УХ|)У V(Y. V Yl) или (X; V xp (Y i V Y.) и т.д.

функция сложения по mod 2 двух двоичных операндов X. и Y. выполняется следующим образом.

Сигналами V (вход 26) и Vj- (вход 24) основной 1 и Дополнительный 2 триггеры устанавливаются в нулевое состояние . Сигналом V (вход 23) операнд X. с информационного входа 30 через элемент И 12 и элемент ИЛИ 18 подается на первые входы элементов И 4 и 9, в результате чего в основном триггере 1 устанавливается сумма (где

«

©- сложение по mod 2). Сигналами V (вход 27) и Vg (вход 28) содержимое основного триггера 1 переписывается в дополнительный триггер 2. Повторно подается сигнал V (вход 23) и второй операнд, подаваемый с информационного входа 30, через элементы И 12, ИЛИ 18 и,И 4 (пли И 9), формирует в основном триггер 1 сумму YJ. Результат выдается на выход 40 управляемого арифметического модуля.

Для реализации функции Пирса, Шеф- фера и эквивалентности производится дизъюнкция, конъюнкция и сложение по mod 2 соответственно и результаты устанавливаются на инверсных вькодах основного 1 (выход 39) и дополнительного 2 (выход 37) триггеров.

Функция сдвига в сторону младших разрядов осуществляется за два полутакта. В первом полутакте сигналом Vj (вход 22) парафазный код содержимого дополнительного триггера 2

(Q-,-,

Q . ) (i-l)-ro разряда через

85792

10

15

20

25

30

40

45

50

информационные входы 31 и 35, через элементы И 5 и 8; переписьшается в основной триггер 1 i-ro разряда. Перепись из основного триггера 1 в дополнительный триггер 2 осуществляе гся сигналами V (вход 27) и V (вход 28) .

Функция сдвига в сторону старших разрядов осуществляется аналогично предыдущему за два полутакта. Сигналом У (вход 21) парафазный код содержимого дополнительного триггера 2 (i+1)-ro разряда подается на информационные входы 32 и 34-i-ro разряда,- Открывается элемент И 6 (или элемент И 7) и возбуждается соответствующий вход основного триггера 1 i-ro разряда. Перепись в дополнительный триггер 2 осуществляется сигналами V. (вход 27) и Vg (вход 28).

Счетчик работает как обычный двухтактный суммирующий двоичньй, счетчик с последовательным переносом.

Для создания структуры многоразрядного двоичного счетчика выход 21 i-ro управляемого арифметического модуля соединяется с информационным входом 30 (i+1)-ro управляемого арифметического модуля.

Двоичный счет осуществляется после установки основного 1 и дополнительного 2 триггеров в нулевое состояние сигналами V-, (вход 26) и Vs (вход 24). Импульсы счета поступают на информационный вход 30 управляемого арифме- 35 тического модуля первого разряда счетчика .

До начала счета на ,управляющий вход 23 подается нулевой уровень синхроимпульса, а на управляющие входы 27 и 28 - единичньш уровень. При подаче первого импульса счета на информационный вход 30 младшего разряда счетчика одновременно на управляющий вход 23 поступает сигнал единичного уровня импульса, который через элемент И 12, элемент RHM 18 и элемент И 4 переводит основной триггер 1 . первого разряда счетчика из состояния лог. О в состояние лог. 1. За второй полупериод синхроимпульса, который подается на управляющие, входы 27 и 28, дополнительный триггер 2 переходит из состояния лог. О в состояние лог. 1. После подачи второго импульса счета и первого полупериода синхроимпульса основной триггер 1 первого разряда счетчика переходит в состояние лог, О. Одновре7158579-2

менно с выхода 41 управляемого арифныа

метического модуля первого разряда счетчика единичньй уровень сигнала подается на информационный вход 30 упПеренос единицы из (i-l)-ro раз ряда поступает на информацио ный вход 36 i-ro разряда управляем арифметического модуля и элемент И

. i ,f -- jii ai nvi«4c 1ичс1 ли1 и модуля И элемент и

равляемого арифметического модуля вто-5 задержкой 19. Пройдя через элемент

рого разряда счетчика: и переводит основной триггер 1.второго разряда в состояние лог. 1 и т.д.

Функция арифметического .сложения двух двоичных операндов осуществляется следующим образом.

Сигналами V., (вход 26) и V (вход 24) основной 1 и дополнительный 2 триггеры устанавливаются в нулевое состояние. Сигналом V. (вход 23) опе10

15

20

ранд X. с информационного входа 30 через элемент И 12 и элемент ИЛИ 18 подается на. первые входы элементов 4 и 9, в результате чего операнд запишется в основной триггер 1. Сигналами V (вход 27) и Vj (вход 28) содер- ясимое основного триггера 1 переписывается в дополнительный триггер 2, сигнал с прямого выхода которого пос- jc тупает на элемент И с задержкой 19.

Таким образом, на первый вход элемента И с задержкой 19 поступает операнд Xj. Затем повторно подается сигнал V (вход 23) и второй операнд, подаваемый с информационного входа 30, поступает на основной триггер 1, где формируется сумма по mod 2 операндов аналогично приведенному, а , также на второй вход элемента И с задержкой 19, на третий вход которого подается сигнал V , (вход 29). На элементе И с задержкой 19 формируется сигнал переноса единицы в старший разряд р. ($ Y ; после поступления

30

35

ИЛИ 18 и элемент И 4 (или элемент ИЛИ 9), сигнал переноса единицы по тупает на основной триггер 1, устан ливая в триггере сумму Х ® Y.® р. Это и будет результатом арифметичес кого сложения двух двоичных операнд Х- и YJ, который сигналамиVj (вход

и V. (вход 28) переписывается в дополнительный триггер 2 и вьздаетс на выход 38 управляемого арифметического модуля.

На элементе И с задержкой 19 ана логично будет формироваться перенос единицы Р; (X - © Y; ) J Р ; .

Для создания структуры многоразр ного сумматрра выход 43 i-ro управл мого арифметического модуля соединя ется с информационным входом 36 (i+1)-ro управляемого арифметическо модуля. Формула изобретени

Управляемый арифметический модул по авт.св. № 1062688, отличаю щийся тем, что, с целью расшир ния функциональных возможностей за счет выполнения функции арифметичес кого сложения двух двоичных операндов, он содержит двенадцатый элемен И и пятый элемент ИЛИ, причем вторы входы первого и десятого элементов соединены через первый вход пятого элемента ИЛИ с выходом седьмого эле мента И, второй вход пятого элемент ИЛИ соединен с седьмым информационг- -- -, 1 ..v v--iv iiwv, jiiji nri iijizi ииединеи с седьмым информацион на его вход операнда Y, который вы- ° ным входом модуля, первый и второй

дается на выход 43 управляемого арифметического модуля с некоторой задержкой t,, не меньшей, чем время, требуемое для формирования суммы по mod 2 операндов (см. фиг. 2), и поступает в ()-й разряд на информационный вход 36 и на второй вход элемента И с задержкой 19.

45

входы двенадцатого элемента И соеди нены соответственно с первым информ ционным входом и десятым управляюсщм входом модуля, прямой выход дополнительного триггера соединен с третьим входом двенадцатого элемента И, выхо которого соединен с седьмьЕм выходом модуля.

8

Перенос единицы из (i-l)-ro разряда поступает на информационный вход 36 i-ro разряда управляемого арифметического модуля и элемент И с

ai nvi«4c 1ичс1 ли1 и модуля И элемент и

задержкой 19. Пройдя через элемент

5 задержкой 19. Пройдя через элемент

0

5

0

c

0

5

ИЛИ 18 и элемент И 4 (или элемент ИЛИ 9), сигнал переноса единицы поступает на основной триггер 1, устанавливая в триггере сумму Х ® Y.® р. . Это и будет результатом арифметического сложения двух двоичных операндов Х- и YJ, который сигналамиVj (вход

и V. (вход 28) переписывается в дополнительный триггер 2 и вьздается на выход 38 управляемого арифметического модуля.

На элементе И с задержкой 19 аналогично будет формироваться перенос единицы Р; (X - © Y; ) J Р ; .

Для создания структуры многоразрядного сумматрра выход 43 i-ro управляемого арифметического модуля соединяется с информационным входом 36 (i+1)-ro управляемого арифметического модуля. Формула изобретения

Управляемый арифметический модуль по авт.св. № 1062688, отличающийся тем, что, с целью расширения функциональных возможностей за счет выполнения функции арифметического сложения двух двоичных операндов, он содержит двенадцатый элемент И и пятый элемент ИЛИ, причем вторые входы первого и десятого элементов И соединены через первый вход пятого элемента ИЛИ с выходом седьмого элемента И, второй вход пятого элемента ИЛИ соединен с седьмым информационiijizi ииединеи с седьмым информацион ° ным входом модуля, первый и второй

iijizi ииединеи с седьмым информацион ным входом модуля, первый и второй

входы двенадцатого элемента И соединены соответственно с первым информационным входом и десятым управляюсщм входом модуля, прямой выход дополнительного триггера соединен с третьим входом двенадцатого элемента И, выход которого соединен с седьмьЕм выходом модуля.

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый арифметический модуль | 1989 |

|

SU1695292A1 |

| Управляемый арифметический модуль | 1979 |

|

SU832553A1 |

| Управляемый арифметический модуль | 1982 |

|

SU1062688A1 |

| Универсальный вычислительный автомат | 1983 |

|

SU1196844A1 |

| Реверсивный регистр сдвига | 1983 |

|

SU1176385A1 |

| Управляемый логический модуль | 1984 |

|

SU1196851A1 |

| Многофункциональный регистр | 1988 |

|

SU1624529A1 |

| Управляемый логический модуль | 1985 |

|

SU1273916A1 |

| Универсальный операционный блок | 1990 |

|

SU1714585A1 |

| Многофункциональный регистр | 1986 |

|

SU1411828A1 |

Изобретение относится к вычислительной технике и предназначено для реализации узлов и устройств цифровых вычислительных машин методами интегральной технологии со средним и большим уровнями интеграции. Целью изобретения является расширение функциональных возможностей модуля за счет выполнения функции арифметического сложения двух двоичных операндов. Управляемый арифметический модуль содержит основной 1 и дополнительный 2 триггеры, одиннадцать элементов И 3-13, пять элементов ИЛИ 14-18 и элемент И с задержкой 19. Модуль позволяет реализовать восемьдесят шесть различных функций, в том числе функцию арифметического сложения двух двоичных операндов. 2 ил.

| Управляемый арифметический модуль | 1982 |

|

SU1062688A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-08-15—Публикация

1988-10-04—Подача