Изобретение относится к вычисли,тельной технике и Г1редназиачеио для реализащ1И узлов и устройств цифровых вычислительных машин методами интегральной технологии со средним 5 и большим уровнем интеграции.

Цель изобретения - прощение моДУля.

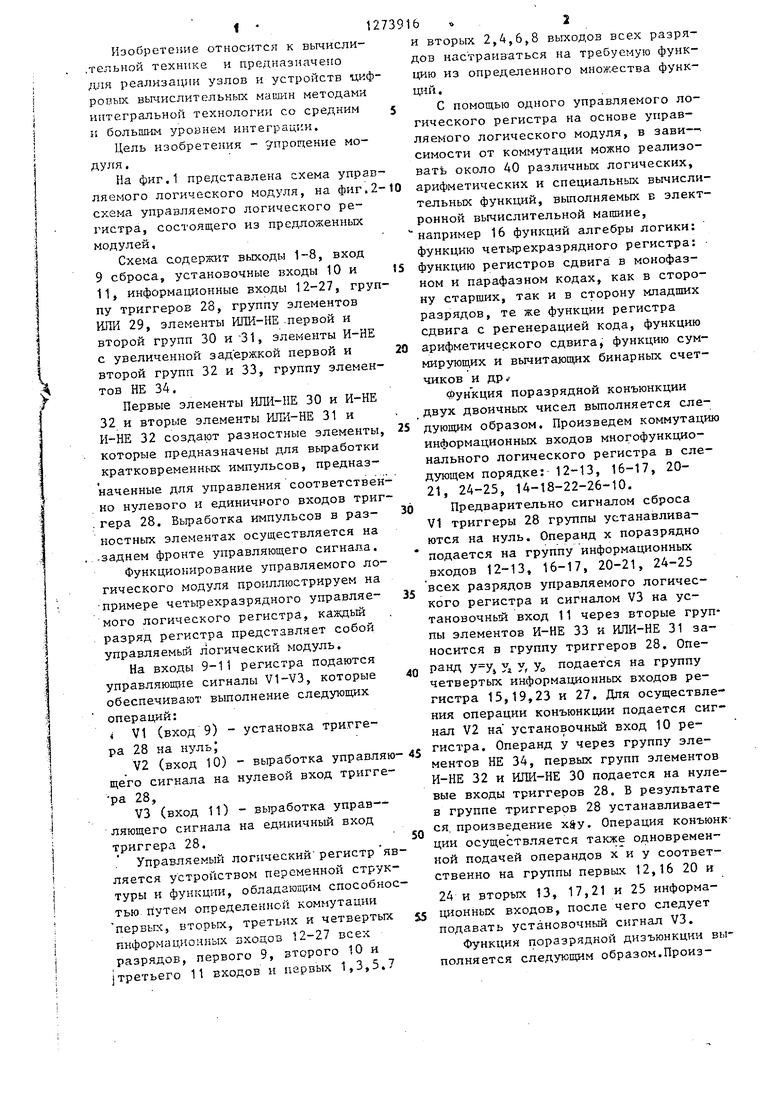

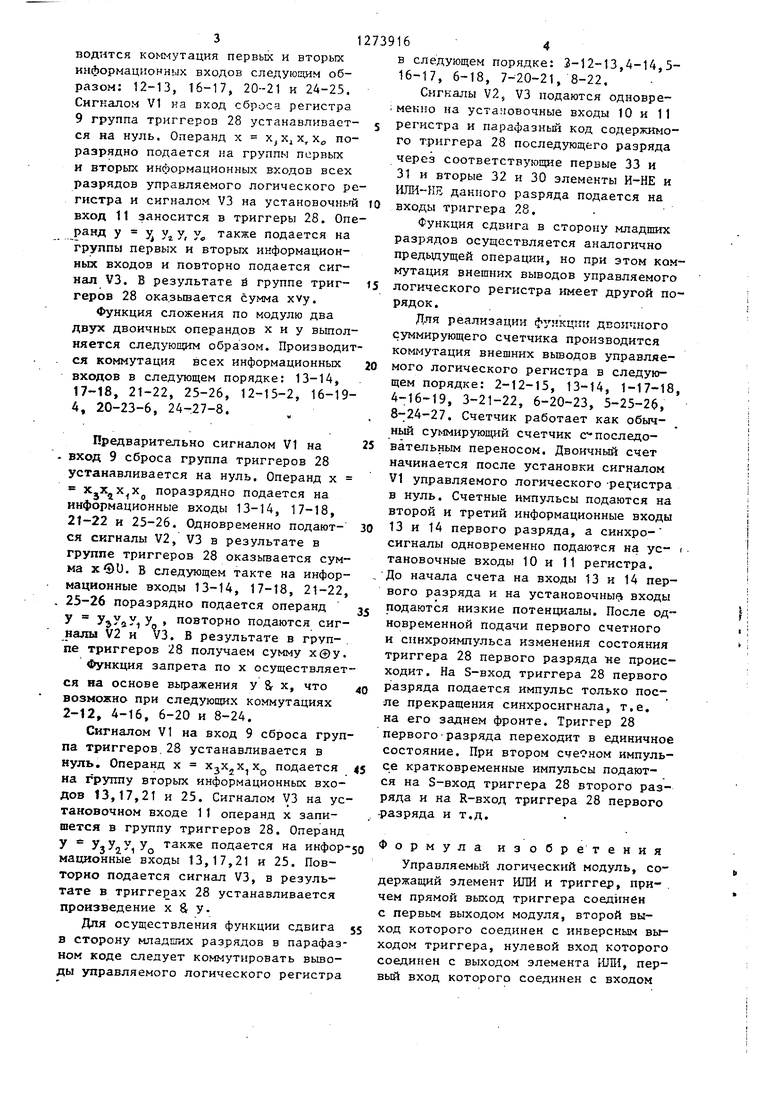

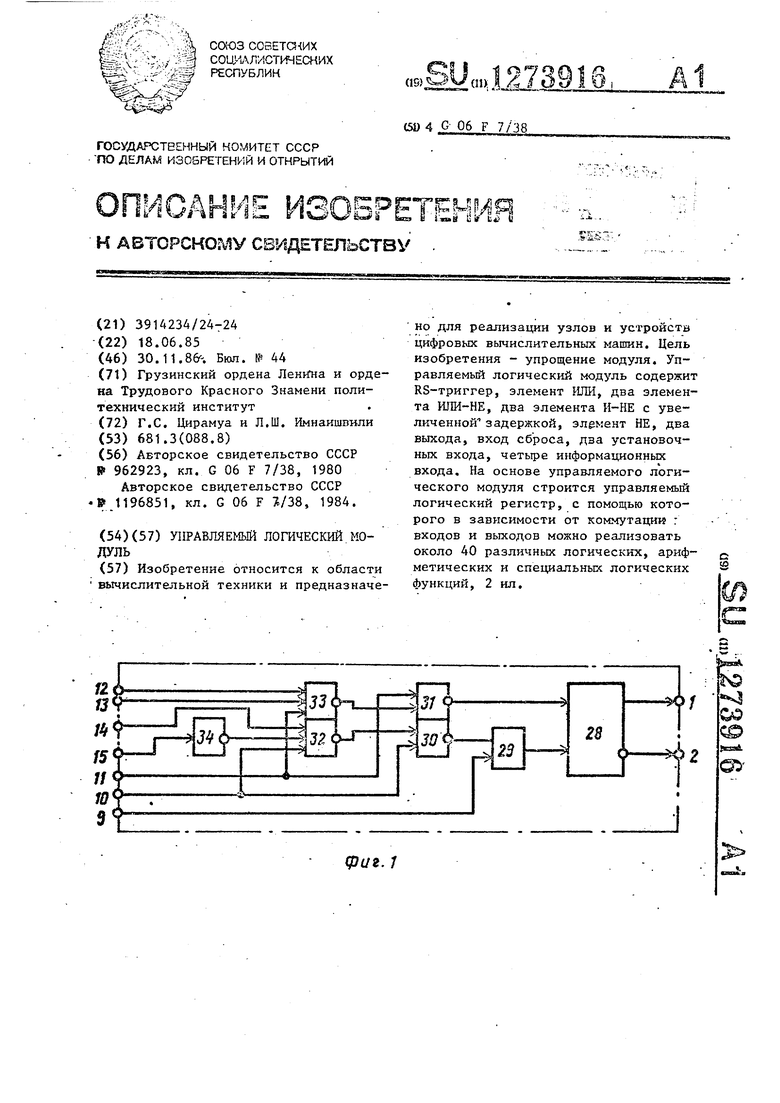

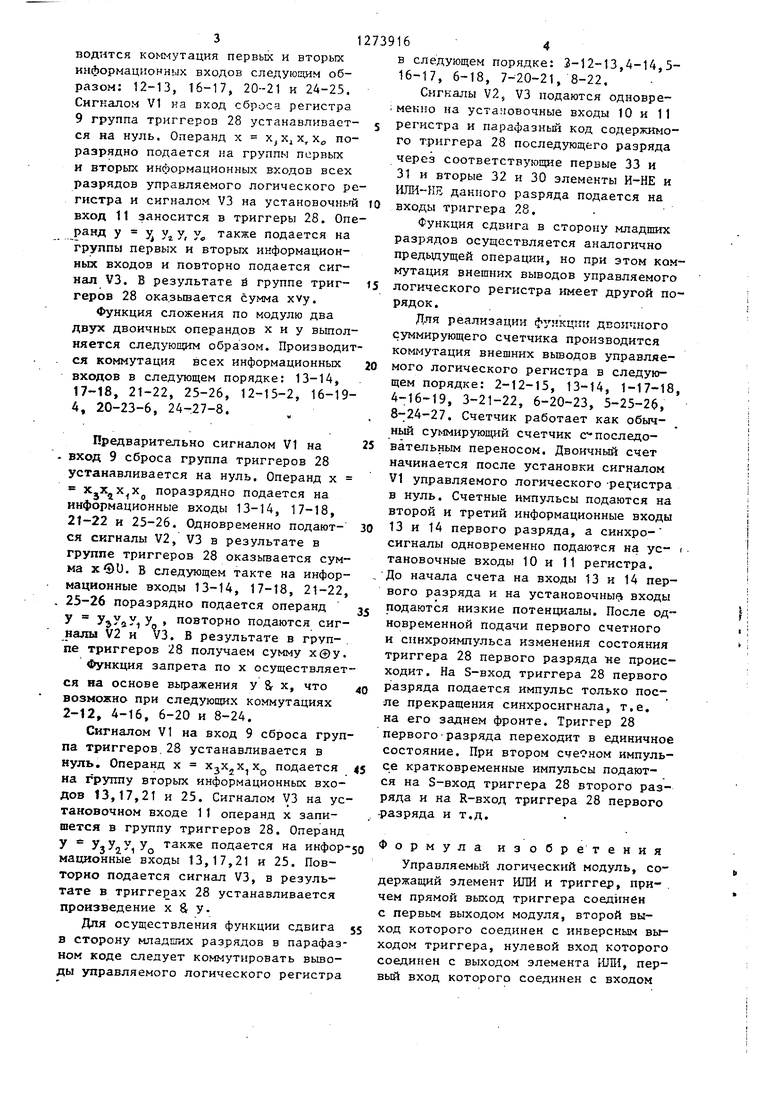

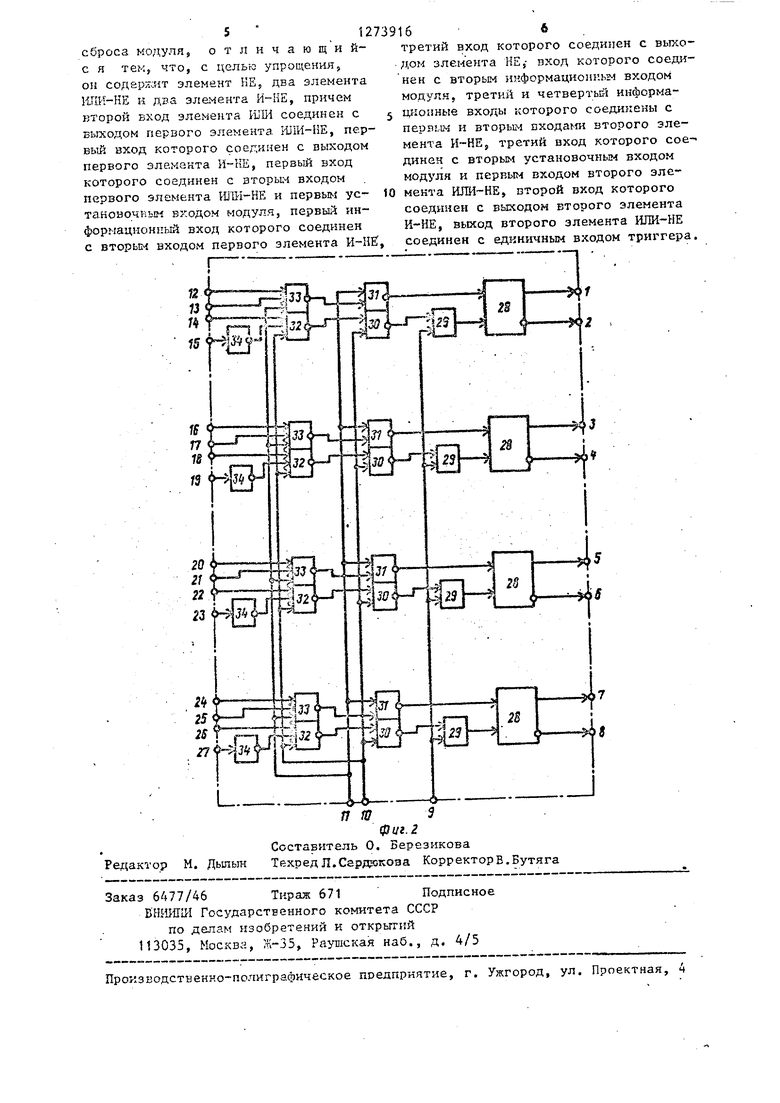

На фиг.1 представлена схема управляемого логического модуля, на фиг.2-10 схема управляемого логического регистра, состоящего из предложенных модулей.

Схема содержит выходы 1-8, вход 9 сброса, установочные входы 10 и tS 11, информационные входы 12-27, группу триггеров 28, группу элементов ИЛИ 29, элементы ШШ-НЕ -первой и второй групп 30 и 31, элементы И-НЕ с увеличенной задержкой первой и 20 второй групп 32 и 33, группу элементов НЕ 34.

Первые элементы ИЛИ-НЕ 30 и И-НЕ 32 и вторые элементы ИЛИ-НЕ 31 и И-НЕ 32 создают разностные элементы, 25 которые предназначены для выработки кратковременных импульсов, предназначенные для управления соответственно нулевого и единичного входов триггера 28. Вьфаботка импульсов в раз- 30 ностных элементах осуществляется на -заднем фронте управляющего сигнала.

Функционирование управляемого логического модуля проиллюстрируем на примере четьфехразрядного управляе- 35 мого логического регистра, каждый . разряд регистра представляет собой управляемый логический модуль.

На входы 9-11 регистра подаются управляющие сигналы V1-V3, которые 40 обеспечивают выполнение следуюпщх операций:

4 VI (вход 9) - установка триггера 28 на нуль;

V2 (вход 10) - выработка управляю- 45 щего сигнала на нулевой вход триггера 28,

V3 (вход 11) - выработка управ- ляющего сигнала на единичный вход триггера 28.50

Управляемый логический регистр является устройством переменной структуры и функции, обладающим способностью путем определенной коммутации первых, вторых, третьу Х и четвертых js информационных входов 12-27 всех разрядов, первого 9, второго 10 и

;рвых 1,3,5.7

jтретьего 11 входов и п

и вторых 2,4,6,8 выходов всех разрядов настраиваться на требуемую функцию из определенного множества функций .

С помощью одного управляемого логического регистра на основе управляемого логического модуля, в зави- симости от коммутации можно реализовать около 40 различных логических, арифметических и специальных вычислительных функций, вьтолняемых в электронной вычислительной матине, например 16 функций алгебры логики: функцию четьфехразрядного регистра: функцию регистров сдвига в монофазном и парафазном кодах, как в сторону старших, так и в сторону младших разрядов, те же функции регистра сдвига с регенерацией кода, функцию арифметического сдвига, функцию суммирующих и вычитающих бинарных счетчиков и Apv

Функция поразрядной конъюнкции двух двоичных чисел вьтолняется следующим образом. Произведем коммутацию информационных входов многофункционального логинеского регистра в следующем порядке: 12-13, 16-17, 2021, 24-25, 14-18-22-26-10.

Предварительно сигналом сброса VI триггеры 28 группы устанавливаются на нуль. Операнд х поразрядно подается на группу информационных входов 12-13, 16-17, 20-21, 24-25 всех разрядов управляемого логического регистра и сигналом V3 на установочньй вход 11 через вторые группы элементов И-НЕ 33 и ИЛИ-НЕ 31 заносится в группу триггеров 28. Операнд Vj у, у подается на группу четвертых информационных входов регистра 15,19,23 и 27, Для осуществления операции конъюнкции подается сигнал V2 на установочный вход 10 реистра. Операнд у через группу элеентов НЕ 34, первых групп элементов -НЕ 32 и ШШ-НЕ 30 подается на нулеые входы триггеров 28. В результате группе триггеров 28 устанавливаетя, произведение . Операция конъюнкии осуществляется также одновременой подачей операндов х и у соответтвенно на группы первых 12,16 20 и

24 и вторых 13, 17,21 и 25 информационных входов, после чего следует подавать установочный сигнал V3.

Функция поразрядной дизъюнкции выполняется следующим образом.Произ3водится коммутация первых и вторых информационных входов следующим образом: 12-13, 16-17, 20--21 и 24-25. Сигналом VI на вход сброса регистра 9 группа триггеров 28 устанавливается на нуль. Операнд х , х поразрядно подается на группы первых и вторых информационных входов всех разрядов управляемого логического ре гистра и сигналом V3 на установочный вход 11 заносится в триггеры 28. Опе ранд У У Уг У, Ув также подается на группы первых и вторых информационных входов и повторно подается сигнал V3. В результате и группе триггеров 28 оказьшается сумма xvy. Функция сложения по модулю два двух двоичньк операндов х и у вьшол няется следующим образом. Производи ся коммутация всех информационных входов в следующем порядке: 13-14, 17-18, 21-22, 25-26, 12-15-2, 16-19 4, 20-23-6, 24-27-8. Предварительно сигналом VI на вход 9 сброса группа триггеров 28 устанавливается на нуль. Операнд х к. поразрядно подается на информационные входы 13-14, 17-18, 21-22 и 25-26. Одновременно подаются сигналы V2, V3 в результате в группе триггеров 28 оказывается сумма хФи. В следующем такте на информационные входы 13-14, 17-18, 21-22, 25-26 поразрядно подается операнд У У5УдУ, У повторно подаются сигналы V2 и V3. В результате в группе триггеров 28 получаем сумму х@у. Функция запрета по х осуществляет ся на основе выражения У & х, что возможно при следующих коммутациях 2-12, 4-16, 6-20 и 8-24. Сигналом VI на вход 9 сброса груп па триггеров.28 устанавливается в нуль. Операнд х подается на группу вторых информационных входов 13,17,21 и 25. Сигналом V3 на ус тановочном входе 11 операнд х запишется в группу триггеров 28. Операнд у у у у у также подается на инфор мационные входы 13,17,21 и 25. Повторно подается сигнал V3, в результате в триггерах 28 устанавливается произведение х S УДля осуществления функции сдвига в сторону младпих разрядов в парафаз ном коде следует коммутировать вьшоды управляемого логического регистра 164 в следующем порядке: 3-12-13,4-14,516-17, 6-18, 7-20-21, 8-22. Сигналы V2, V3 подаются одновремекио на устаповочные входы 10 и 11 регистра и парафазньй код содержимого триггера 28 последующего разряда через соответствующие первые 33 и 31 и вторые 32 и 30 злементы И-НЕ и 11ЛИ-НЕ данного разряда подается на входы триггера 28. Функция сдвига в сторону младших разрядов осуществляется аналогично предыдущей операции, но при этом коммутация внешних выводов управляемого логического регистра имеет другой порядок. Для реализации Фзякции двоичного суммирующего счетчика производится коммутация внешних вьюодов управляемого логического регистра в следующем порядке: 2-12-15, 13-14, 1-17-18, 4-16-19, 3-21-22, 6-20-23, 5-25-26, 8-24-27. Счетчик работает как обычньй суммирующий счетчик с последовательным переносом. Двоичный счет начинается после установки сигналом VI управляемого логического -pei HCTpa в нуль. Счетные импульсы подаются на второй и третий информационные входы 13 и 14 первого разряда, а синхросигналы одновременно подаются на ус- t тановочные входы 10 и 11 регистра. До начала счета на входы 13 и 14 первого разряда и на установочные входы подаются низкие потенциалы. После одновременной подачи первого счетного и синхроимпульса изменения состояния триггера 28 первого разряда не происходит . На S-вход триггера 28 первого разряда подается импульс только после прекращения синхросигнала, т.е. на его заднем фронте. Триггер 28 первого-разряда переходит в единичное состояние. При втором счес-ном импульсе кратковременные импульсы подаются на S-вход триггера 28 второгь разряда и на R-вход триггера 28 первого разряда и т.д. Формула изобретения Управляемый логический модуль, содержащий злемент ИЛИ и триггер, при- . чем прямой выход триггера соединен с первым вьгходом модуля, второй выход которого соединен с инверсным выходом триггера, нулевой вход которого соединен с выходом элемента i-ШИ, первый вход которого соединен с входом

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый логический модуль | 1984 |

|

SU1196851A1 |

| Реверсивный регистр сдвига | 1983 |

|

SU1176385A1 |

| Управляемый арифметический модуль | 1989 |

|

SU1695292A1 |

| Управляемый арифметический модуль | 1979 |

|

SU832553A1 |

| Устройство для выполнения команд реализации систем многоместных логических функций | 1981 |

|

SU999051A1 |

| Универсальный вычислительный автомат | 1983 |

|

SU1196844A1 |

| Управляемый арифметический модуль | 1982 |

|

SU1062688A1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для определения числа единиц в двоичном коде с контролем | 1990 |

|

SU1795460A1 |

УПРАВЛЯЕМЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ

Изобретение относится к области вычислительной техники и предназначено для реализации узлов и устройств цифровых вычислительных машин. Цель изобретения - упрощение модуля. Управляемьй логический модуль содержит RS-триггер, элемент ИЛИ, два элемента ШШ-НЕ, два элемента И-НЕ с увеличенной задержкой, элемент НЕ, два выхода, вход сброса, два установочных входа, четыре информационных входа. На основе управляемого логического модуля строится управляемый логический регистр, с помощью которого в зависимости от коммутации : входов и выходов можно реализовать около 40 различных логических, арифс (Л метических и специальных логических функций, 2 ил. Г2 О /«t /5 И Ю В iralA Ю с 1 Z Сриг. 1

| Управляемый логический модуль | 1980 |

|

SU962923A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Управляемый логический модуль | 1984 |

|

SU1196851A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-30—Публикация

1985-06-18—Подача