w

Ј

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для межмашинного обмена | 1985 |

|

SU1298756A1 |

| Устройство для записи и анализа циклограмм дискретных блоков | 1985 |

|

SU1313221A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для связи процессоров | 1984 |

|

SU1193682A1 |

| Программное временное устройство | 1990 |

|

SU1762298A1 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах обмена информацией управляющей ЭВМ с объектами по последовательному каналу группами р-разрядных слов. Цель изобретения - расширение области применения за счет возможности обмена группами р-разрядных слов по последовательному каналу. Устройство для обмена информацией содержит триггер, генератор импульсов, элемент И, элемент И-НЕ, формирователь импульса, элемент ИЛИ, счетчиктактов, регистр, элемент задержки, блок постоянной памяти, шинный формирователь, регистр управления, два коммутатора сигналов, счетчик записи-чтения, два элемента НЕ. блок оперативной памяти, счетчик слов. 5 ил., 1 табл.

Изобретение относится к вычислительной технике и может быть использовано в системах обмена информацией управляющей ЭВМ с объектами по последовательному каналу группами р-разрядных слов.

Целью изобретения является расширение области применения за счет возможности обмена группами р-разрядных слов по последовательному каналу.

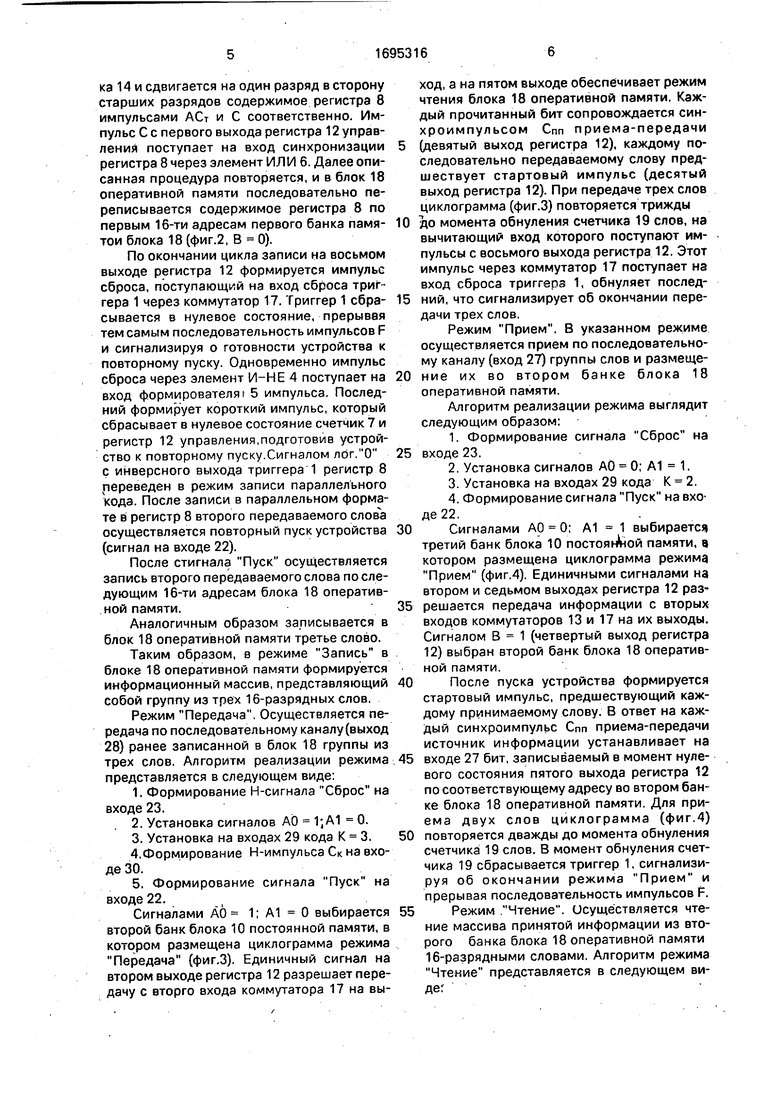

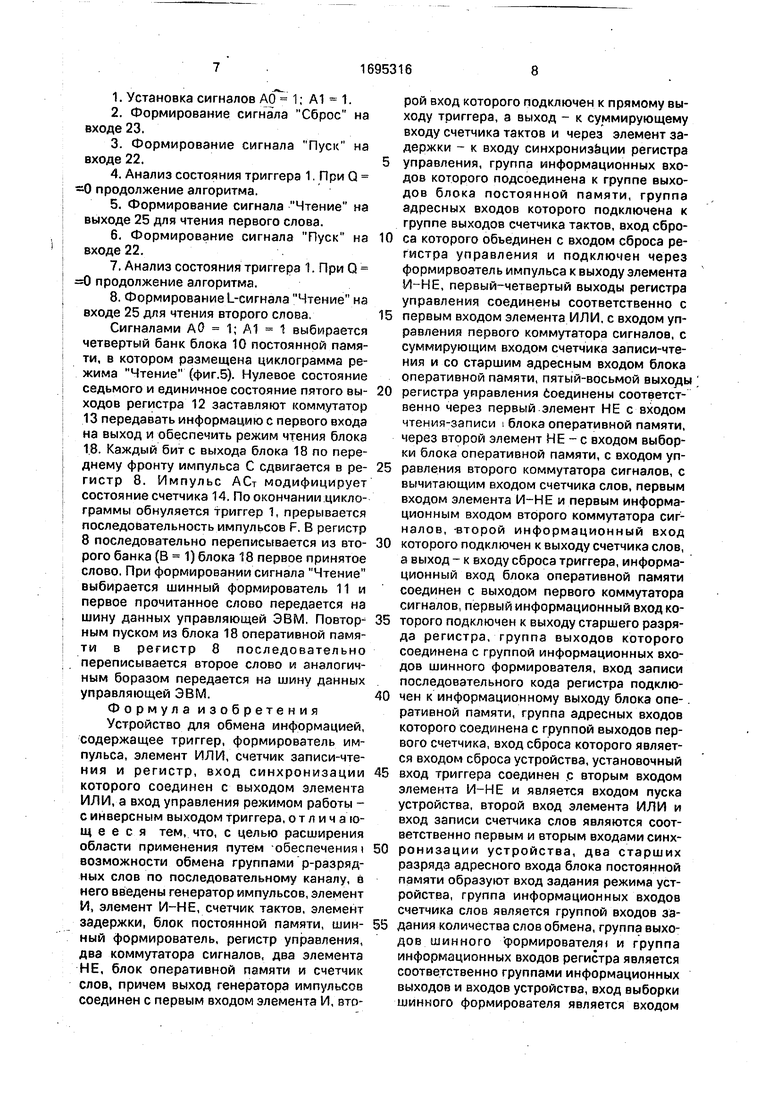

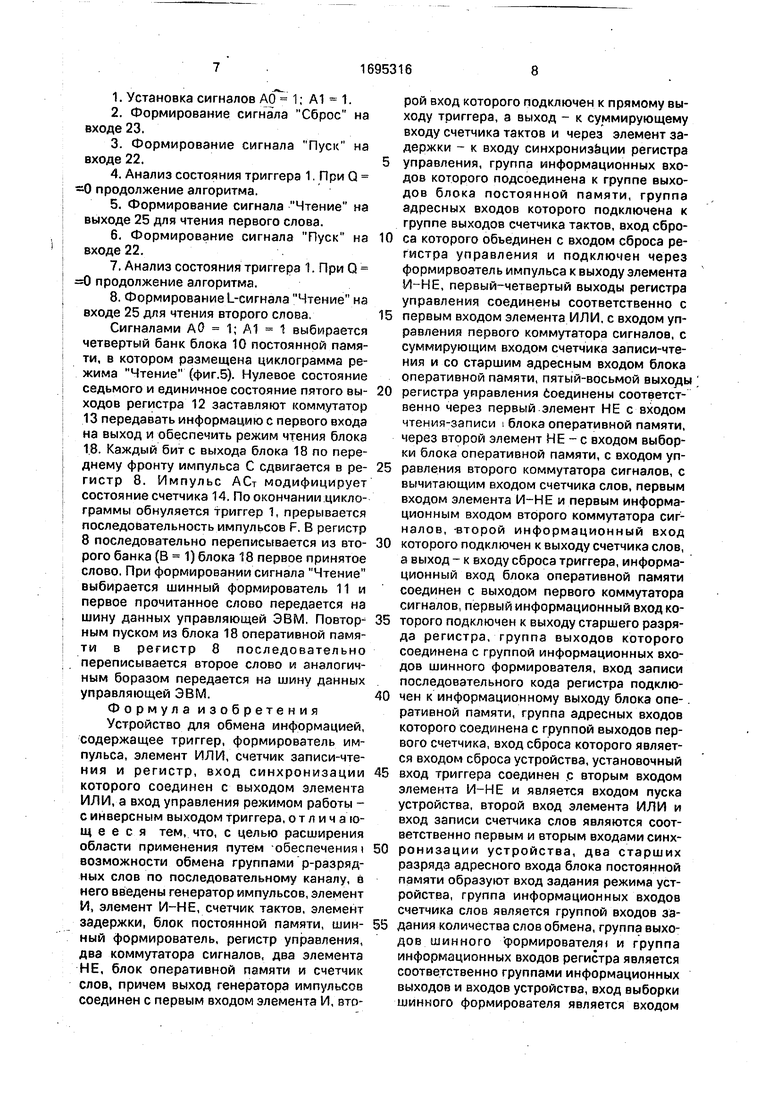

На фиг.1 приведена функциональная схема устройства для обмена информацией; на фиг.2-5 - временные диаграммы работы в режимах Запись, Передача, Прием и Чтение соответственно.

Устройство содержит (фиг.1) триггер 1, генератор 2 импульсов, элемент И 3, элемент И-НЕ 4, формирователь 5 импульсов, элемент ИЛИ 6, счетчик 7 тактов, регистр 8. элемент 9 задержки, блок 10 постоянной памяти, шинный формирователь 11, регистр

12 управления, первый коммутатор 13 сигналов, счетчик 14 записи-чтения, элементы НЕ 15 и 16, второй коммутатор 17 сигналов, блок 18 оперативной памяти, счетчик 19 слов, параллельные информационные входы 20 и выходы 21 устройства, вход 22 пуска устройства, вход 23 сброса устройства, первый вход 24 синхронизации устройства, вход 25 чтения устройства, входы 26 задания режима работы устройства, последовательные информационные вход 27 и выход 28 устройства, входы 29 задания кода количества передаваемых-принимаемых по последовательному каналу р-разрядных слов, второй вход 30 синхронизации, выход 31 синхроимпульсов приема-передачи и выход 32 стартового импульса устройства.

Блок 10 постоянной памяти может быть реализован, например, на двух микросхемах типа 556РТ5, программируемых в соотON Ю СЛ

СО

«я

о

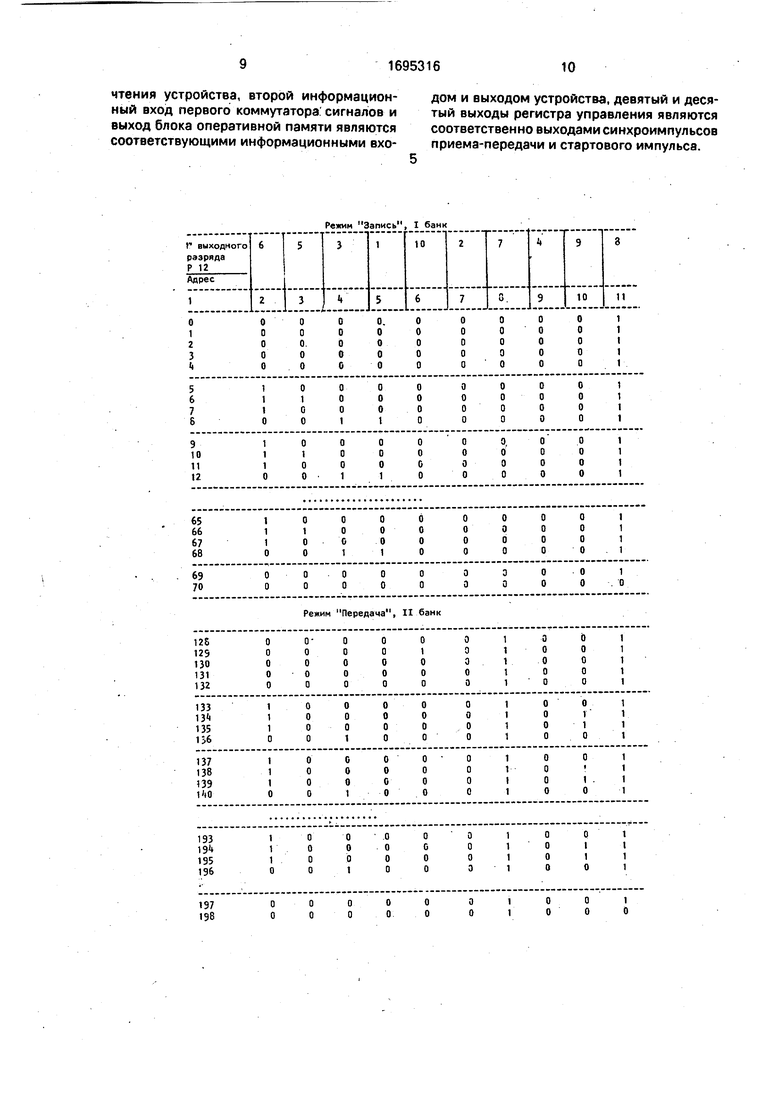

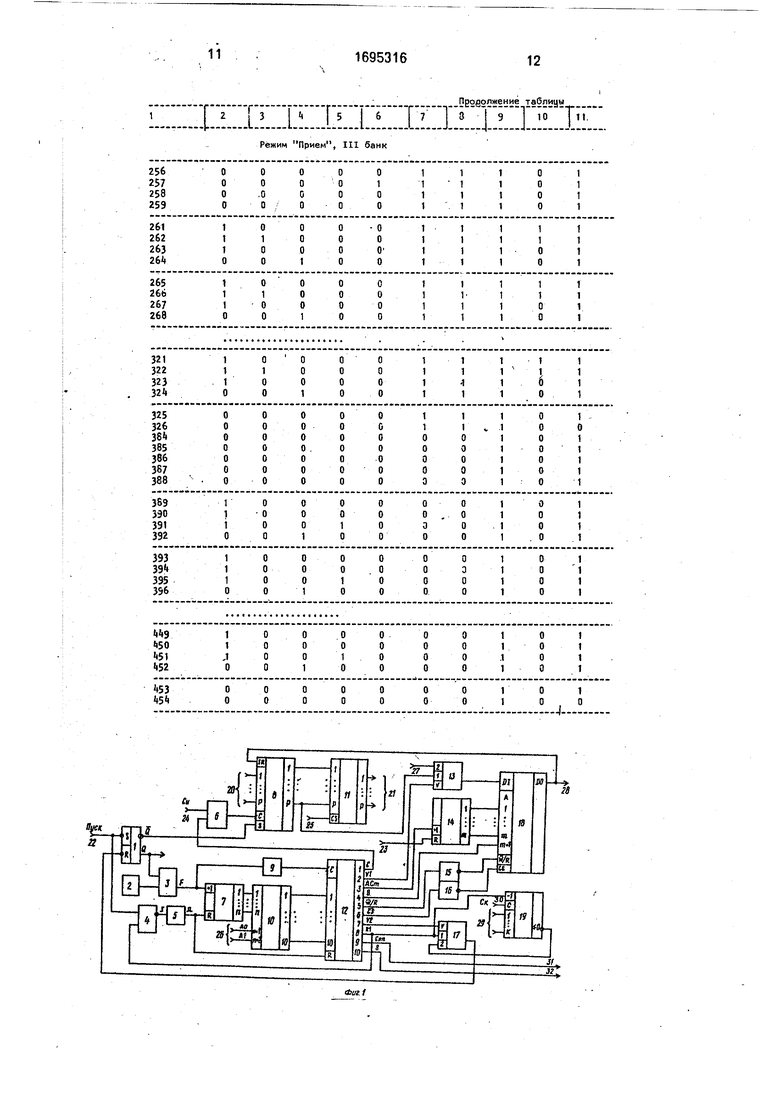

ветствии с таблицей. Циклопрограммы режимов Запись, Передача, Прием и Чтение, размещенные в четырех банках памяти, позволяют вести обмен группами 16-разрядных слов.

Устройство работает следующим образом.

Обмен информацией между ЭВМ и объектами по последовательному каналу осуществляется под управлением ЭВМ, формирующей сигналы Сброс, Пуск, Чтение, код К, сигналы ОА и А1 задания режима работы, синхроимпульсы Си и С.

Полный цикл обмена информацией включает последовательную работу устройства в режимах Запись, Передача, Прием и Чтение. По желанию пользователя возможны любые варианты одностороннего обмена.

Принцип работы и алгоритм управления устройством рассматриваются на примере организации полного цикла обмена с передачей по последовательному каналу трех и приемом двух 16-разрядных слов.

В режиме Запись в блоке 18 оперативной памяти формируется массив из трех 16- разрядных слов. Алгоритм формирования массива выглядит следующим образом:

При формировании сигнала Сброс единичный импульс на входе 23 - сбрасывается в нулевое состояние счетчик 14. По переднему фронту импульса Си на входе 24 16-разрядное слово с входов 20 записывается в регистр 8. Записанное слово может

быть проконтролировано программными средствами при формировании сигнала Чтение на входе 25, чем обеспечивается передача на выход 21 содержимого регист5 ра 8 через шинный формирователь 11 на шину данных управляющей ЭВМ. По сигналу Пуск на входе 22. устанавливается в единичное состояние триггер 1. Одновременно сигнал Пуск, инвертируемый элементом

0 И-НЕ 4, поступает на вход формирователе 5 импульса. По переднему фронту формирователь 5 импульса вырабатывает короткий импульс, поступающий на входы сброса счетчика 7 и регистра 12 управления. Ре5 гистр 12 управления и счетчик 7 сбрасываются в нулевое состояние. Единичный уровень с выхода триггера 1 поступает на первый вход элемента И 3, разрешая прохождение импульсов с генератора 2 импуль0 сов на суммирующий вход счетчика 7 и через элемент 9 задержки на вход синхронизации регистра 12 управления. Сигналами АО 0; А1 0 выбирается первый банк блока 10 постоянной памяти, в котором раз5 мещена циклограмма режима Запись (фиг.2). Сигналом лог. О с инверсного выхода триггера 1 регистр 8 переведен в режим сдвига. По переднему фронту каждого импульса генератора 2 (последовательность F)

0 счетчик 7 изменяет свое состояние в сторону увеличения. Содержимым счетчика 7 осуществляется адресация к ячейкам блока 10 постоянной памяти, Содержимое каждой адресуемой ячейки блока 10 постоянной па5 мяти переписывается с задержкой в регистр 12 управления. Наличие регистра 12 в составе устройства необходимо для устранения состояний на выходах блока 10 постоянной памяти при модификации адресов. Наличие

0 элементов НЕ 15 и 16 обеспечивает невыбранное состояние блока 18 оперативной памяти в начальный момент формирования циклограммы при обнулении регистра 12 управления и устраняет несанкционирован5 ное обращение к блоку 18. Нулевые сигналы на втором и седьмом выходах регистра 12 обеспечивают передачу информации коммутаторами 13 и 17 с первых входов на выходы. После пятого импульса последовательности F

0 нулевым сигналом на шестом выходе регистра 12 выбирается блок 18 оперативной памяти, на информационный вход которого через коммутатор 13 поступает сигнал с выхода старшего разряда регистра 8. После

5 шестого импульса последовательности F (фиг.2) названный сигнал при нулевом сигнале на пятом выходе регистра 12 записывается по нулевому адресу в блок 18 оперативной памяти. После восьмого импульса F модифицируется состояние счетчика 14 и сдвигается на один разряд в сторону старших разрядов содержимое регистра 8 импульсами АСт и С соответственно. Импульс С с первого выхода регистра 12 управления поступает на вход синхронизации регистра 8 через элемент ИЛИ 6. Далее описанная процедура повторяется, и в блок 18 оперативной памяти последовательно переписывается содержимое регистра 8 по первым 16-ти адресам первого банка памя- той блока 18 (фиг.2, В 0).

По окончании цикла записи на восьмом выходе регистра 12 формируется импульс сброса, поступающий на вход сброса триггера 1 через коммутатор 17. Триггер 1 сбра- сывается в нулевое состояние, прерывая тем самым последовательность импульсов F и сигнализируя о готовности устройства к повторному пуску. Одновременно импульс сброса через элемент И-НЕ 4 поступает на вход формирователя 5 импульса. Последний формирует короткий импульс, который сбрасывает в нулевое состояние счетчик 7 и регистр 12 управления,подготовив устройство к повторному пуску.Сигналом лог.О с инверсного выхода триггера 1 регистр 8 переведен в режим записи параллельного кода. После записи в параллельном формате в регистр 8 второго передаваемого слова осуществляется повторный пуск устройства (сигнал на входе 22).

После стигнала Пуск осуществляется запись второго передаваемого слова по следующим 16-ти адресам блока 18 оперативной памяти.

Аналогичным образом записывается в блок 18 оперативной памяти третье слово.

Таким образом, в режиме Запись в блоке 18 оперативной памяти формируется информационный массив, представляющий собой группу из трех 16-разрядных слов.

Режим Передача. Осуществляется передача по последовательному каналу(выход 28) ранее записанной в блок 18 группы из трех слов. Алгоритм реализации режима представляется в следующем виде:

Сигналами АО 1; А1 0 выбирается второй банк блока 10 постоянной памяти, в котором размещена циклограмма режима Передача (фиг.З). Единичный сигнал на втором выходе регистра 12 разрешает передачу с вторго входа коммутатора 17 на выход, а на пятом выходе обеспечивает режим чтения блока 18 оперативной памяти. Каждый прочитанный бит сопровождается синхроимпульсом Спп приема-передачи (девятый выход регистра 12), каждому последовательно передаваемому слову предшествует стартовый импульс (десятый выход регистра 12). При передаче трех слов циклограмма (фиг.З) повторяется трижды до момента обнуления счетчика 19 слов, на вычитающий вход которого поступают импульсы с восьмого выхода регистра 12. Этот импульс через коммутатор 17 поступает на вход сброса триггера 1, обнуляет последний, что сигнализирует об окончании передачи трех слов.

Режим Прием. В указанном режиме осуществляется прием по последовательному каналу (вход 27) группы слов и размещение их во втором банке блока 18 оперативной памяти.

Алгоритм реализации режима выглядит следующим образом:

Сигналами АО 0; А1 1 выбирается третий банк блока 10 постоянной памяти, в котором размещена циклограмма режима Прием (фиг.4). Единичными сигналами на втором и седьмом выходах регистра 12 разрешается передача информации с вторых входов коммутаторов 13 и 17 на их выходы. Сигналом В 1 (четвертый выход регистра 12) выбран второй банк блока 18 оперативной памяти.

После пуска устройства формируется стартовый импульс, предшествующий каждому принимаемому слову. В ответ на каждый синхроимпульс Спп приема-передачи источник информации устанавливает на входе 27 бит, записываемый в момент нулевого состояния пятого выхода регистра 12 по соответствующему адресу во втором банке блока 18 оперативной памяти. Для приема двух слов циклограмма (фиг.4) повторяется дважды до момента обнуления счетчика 19 слов. В момент обнуления счетчика 19 сбрасывается триггер 1, сигнализируя об окончании режима Прием и прерывая последовательность импульсов F.

Режим .Чтение. Осуществляется чтение массива принятой информации из второго банка блока 18 оперативной памяти 16-разрядными словами. Алгоритм режима Чтение представляется в следующем ви- дег

Сигналами АО 1; А1 1 выбирается четвертый банк блока 10 постоянной памяти, в котором размещена циклограмма режима Чтение (фиг.5). Нулевое состояние седьмого и единичное состояние пятого выходов регистра 12 заставляют коммутатор 13 передавать информацию с первого входа на выход и обеспечить режим чтения блока 18. Каждый бит с выхода блока 18 по переднему фронту импульса С сдвигается в регистр 8. Импульс АСТ модифицирует состояние счетчика 14. По окончании циклограммы обнуляется триггер 1, прерывается последовательность импульсов F. В регистр 8 последовательно переписывается из второго банка (В 1) блока 18 первое принятое слово. При формировании сигнала Чтение выбирается шинный формирователь 11 и первое прочитанное слово передается на шину данных управляющей ЭВМ. Повторным пуском из блока 18 оперативной памяти в регистр 8 последовательно переписывается второе слово и аналогичным боразом передается на шину данных управляющей ЭВМ.

Формула изобретения Устройство для обмена информацией, содержащее триггер, формирователь импульса, элемент ИЛИ, счетчик записи-чтения и регистр, вход синхронизации которого соединен с выходом элемента ИЛИ, а вход управления режимом работы - с инверсным выходом триггера, отличающееся тем, что, с целью расширения области применения путем -обеспечения t возможности обмена группами р-разряд- ных слов по последовательному каналу, в него введены генератор импульсов, элемент И, элемент И-НЕ, счетчик тактов, элемент задержки, блок постоянной памяти, шинный формирователь, регистр управления, два коммутатора сигналов, два элемента НЕ, блок оперативной памяти и счетчик слов, причем выход генератора импульсов соединен с первым входом элемента И, второй вход которого подключен к прямому выходу триггера, а выход - к суммирующему входу счетчика тактов и через элемент задержки - к входу синхронизации регистра

управления, группа информационных входов которого подсоединена к группе выходов блока постоянной памяти, группа адресных входов которого подключена к группе выходов счетчика тактов, вход сбро0 са которого объединен с входом сброса регистра управления и подключен через формирвоатель импульса к выходу элемента И-НЕ, первый-четвертый выходы регистра управления соединены соответственно с

5 первым входом элемента ИЛИ, с входом управления первого коммутатора сигналов, с суммирующим входом счетчика записи-чтения и со старшим адресным входом блока оперативной памяти, пятый-восьмой выходы

0 регистра управления соединены соответственно через первый элемент НЕ с входом чтения-записи : блока оперативной памяти, через второй элемент НЕ - с входом выборки блока оперативной памяти, с входом уп5 равления второго коммутатора сигналов, с вычитающим входом счетчика слов, первым входом элемента И-НЕ и первым информационным входом второго коммутатора сигналов, -второй информационный вход

0 которого подключен к выходу счетчика слов, а выход - к входу сброса триггера, информационный вход блока оперативной памяти соединен с выходом первого коммутатора сигналов, первый информационный вход ко5 торого подключен к выходу старшего разряда регистра, группа выходов которого соединена с группой информационных входов шинного формирователя, вход записи последовательного кода регистра подклю0 чен к информационному выходу блока оперативной памяти, группа адресных входов которого соединена с группой выходов первого счетчика, вход сброса которого является входом сброса устройства, установочный

5 вход триггера соединен с вторым входом элемента И-НЕ и является входом пуска устройства, второй вход элемента ИЛИ и вход записи счетчика слов являются соответственно первым и вторым входами синх0 ронизации устройства, два старших разряда адресного входа блока постоянной памяти образуют вход задания режима устройства, группа информационных входов счетчика слов является группой входов за5 дания количества слов обмена, группа выходов шинного формирователя) и группа информационных входов регистра является соответственно группами информационных выходов и входов устройства, вход выборки шинного формирователя является входом

чтения устройства, второй информационный вход первого коммутатора сигналов и выход блока оперативной памяти являются соответствующими информационными вхоРежим Запись, I банк

Режим Передача, II банк

дом и выходом устройства, девятый и десятый выходы регистра управления являются соответственно выходами синхроимпульсов приема-передачи и стартового импульса.

Продолжение таблицы

izziiniiEZLiiniziaiiiz.ii--.

Пуск

IT

F -jimMmmK...

cs

ty

MMmEL ...

с A

5

VI

V2

В

Cnn

R1 -

Пуск(Г

F -АлДАмшлям:::

Щ

летmm ...

с

««iBBii MaBMM

rt

Vf

i MMNNMMIWMWBHMMne iWBBBBBIia HMHHMHIV H HMMMH # «

V2

«

в

§ « ««ННННММ ННМВМВ | М М«В 1Н М Ш

Фиг. 3

Й1

Фиг. 2

n&fbf 2 3b5S789f6f 2/3

F -ЛШШЛЛЛЛЛШШП.

CS W/R.

ACm С ,

S VI

П В

snITL

мшмммм :::

cs

/Л

6f 6263№656667686970

IS

Фил А

ттш

па т

Фиг.5

U

| Устройство ввода-вывода информации | 1983 |

|

SU1226429A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обмена информацией | 1984 |

|

SU1277121A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-11-30—Публикация

1989-12-13—Подача