Изобретение относится к вычислительой технике, а именно к запоминающим устройствам и может найти применение в микропроцессорной технике.

Цель изобретения - повышение быстро- 5 действия устройства.

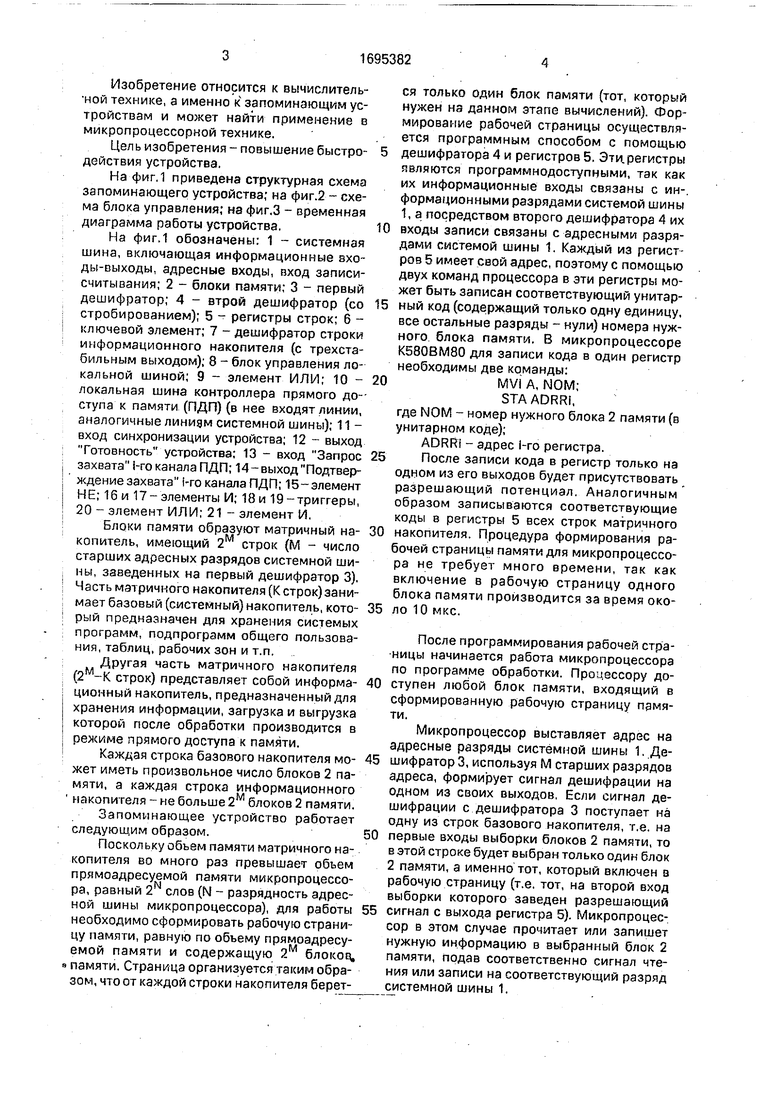

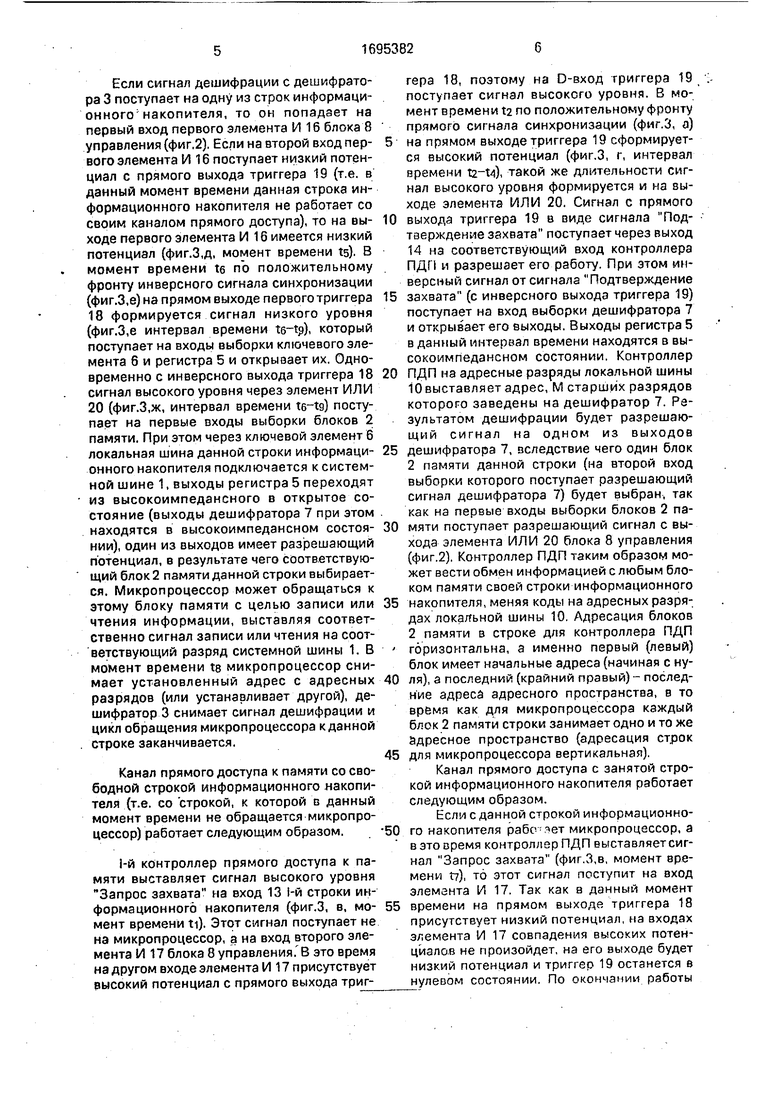

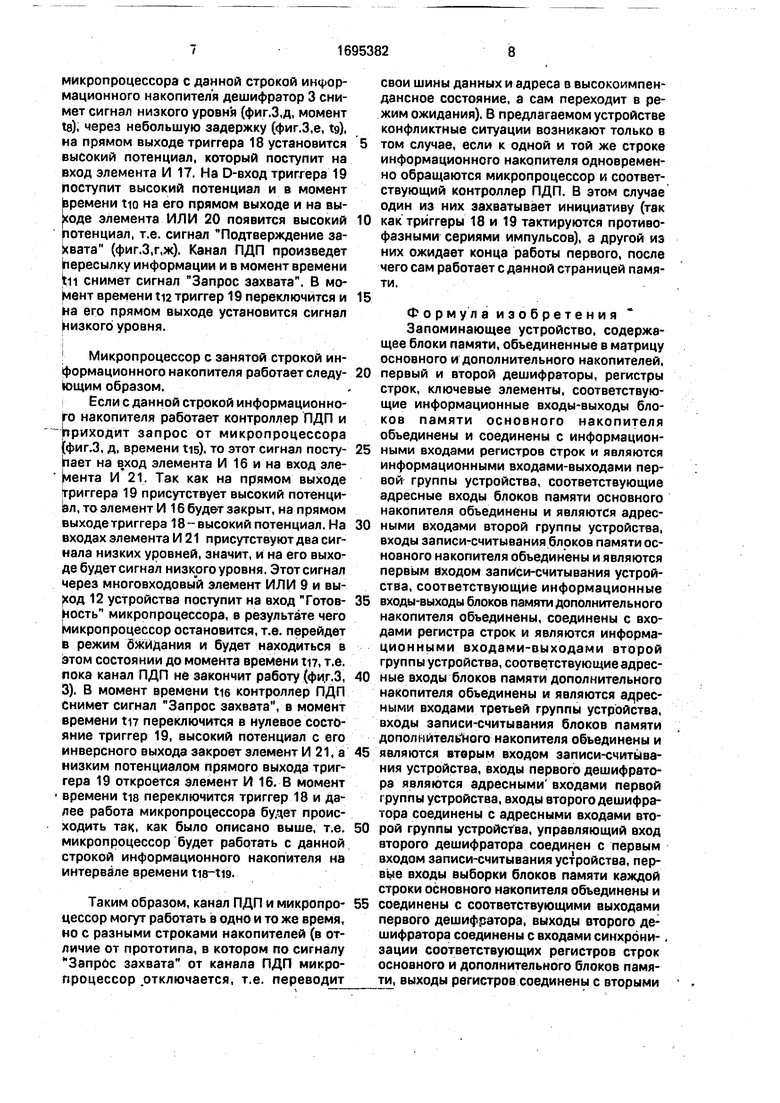

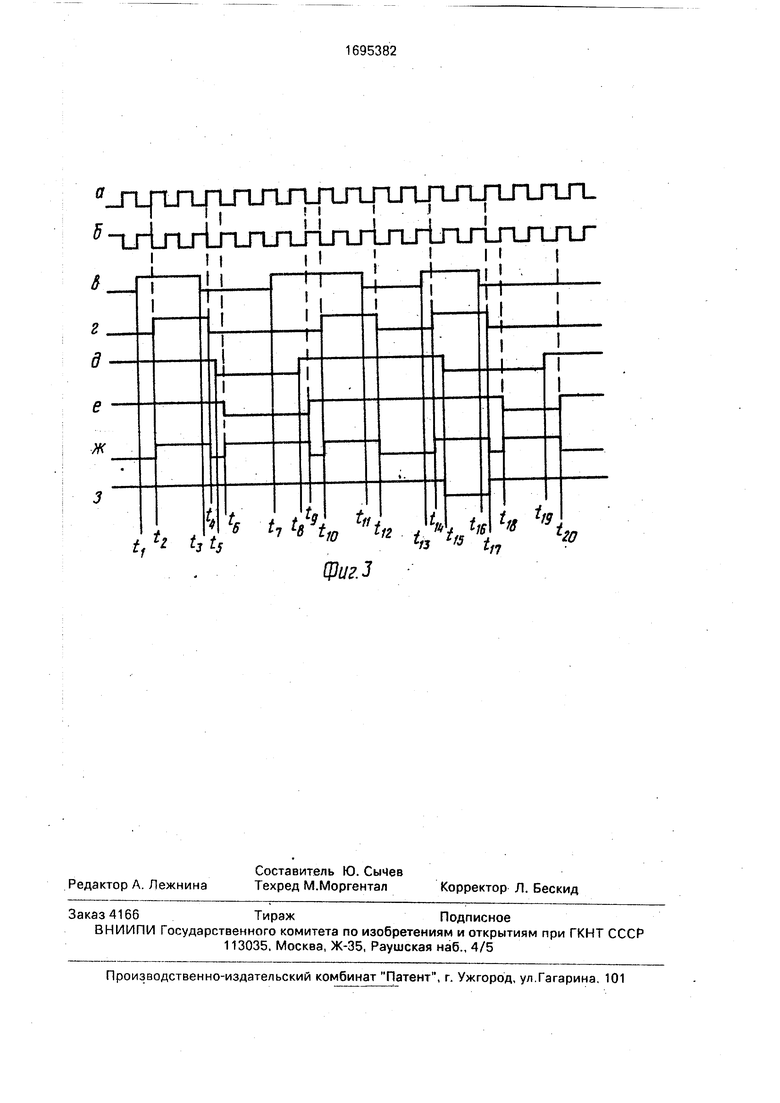

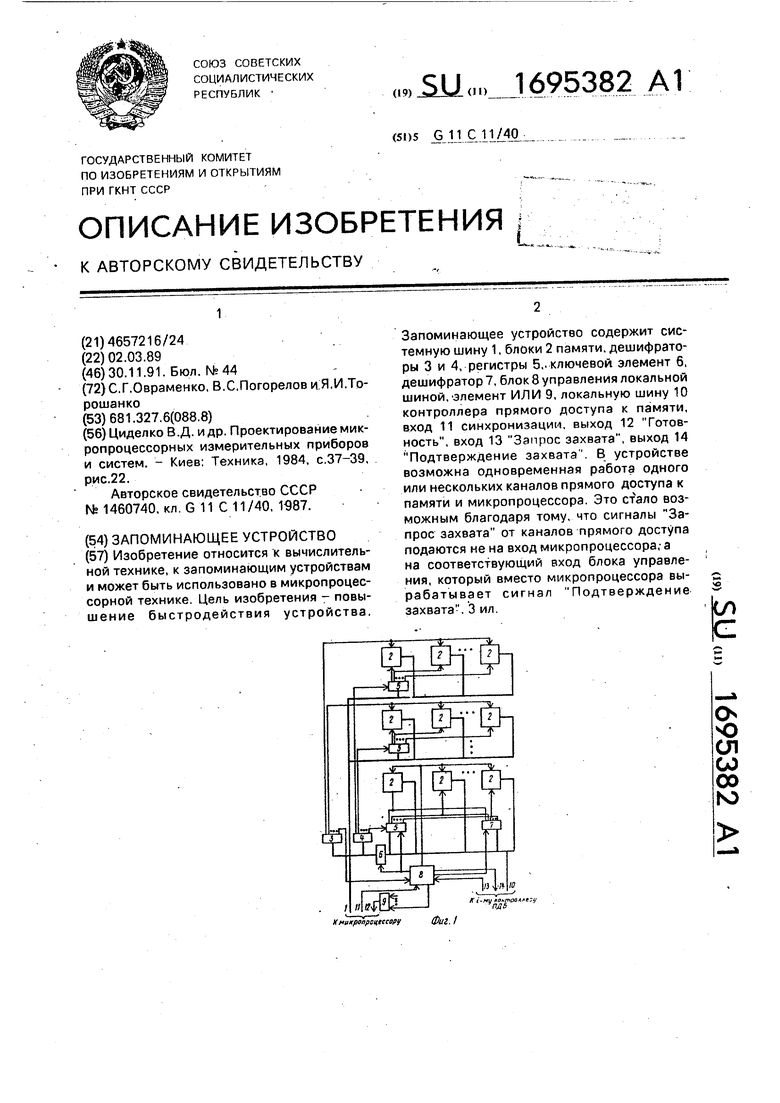

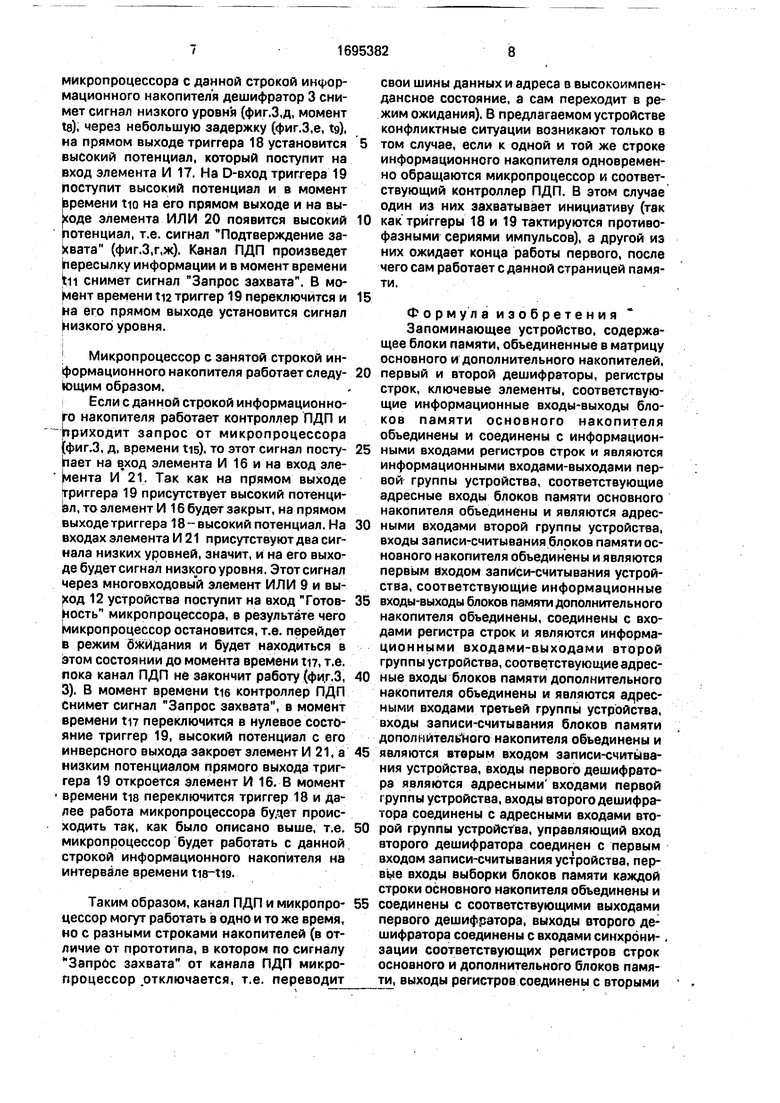

На фиг.1 приведена структурная схема запоминающего устройства; на фиг.2 - схема блока управления; на фиг.З - временная диаграмма работы устройства.10

На фиг.1 обозначены: 1 - системная шина, включающая информационные входы-выходы, адресные входы, вход записи- считывания; 2 - блоки памяти; 3 - первый дешифратор; 4 - втрой дешифратор (со 15 стробированием); 5 - регистры строк; 6 - ключевой элемент; 7 -дешифратор строки информационного накопителя (с трехста- бильным выходом); 8 - блок управления локальной шиной; 9 - элемент ИЛИ; 10 - 20 локальная шина контроллера прямого до-ступа к памяти (ПДП) (в нее входят линии, аналогичные линиям системной шины); 11- вход синхронизации устройства; 12 - выход Готовность устройства; 13 - вход Запрос 25 захвата i-ro канала ПДП; 14-выход Подтверждение захвата i-ro канала ПДП; 15-элемент НЕ; 16 и 17-элементы И; 18и 19-триггеры, 20 - элемент ИЛИ; 21 - элемент И.

Блоки памяти образуют матричный на- 30 копитель, имеющий 2м строк (М - число старших адресных разрядов системной шины, заведенных на первый дешифратор 3), Часть мат ричного накопителя (К строк) занимает базовый (системный) накопитель, кото- 35 рый предназначен для хранения системых программ, подпрограмм общего пользования, таблиц, рабочих зон и т.п.

Другая часть матричного накопителя (2М-К строк) представляет собой информа- 40 ционный накопитель, предназначенный для хранения информации, загрузка и выгрузка которой после обработки производится в режиме прямого доступа к памяти.

Каждая строка базового накопителя мо- 45 жет иметь произвольное число блоков 2 памяти, а каждая строка информационного накопителя - не больше 2 блоков 2 памяти.

Запоминающее устройство работает следующим образом.50

Поскольку обьем памяти матричного накопителя во много раз превышает обьем прямоадресуемой памяти микропроцессора, равный 2N слов (N - разрядность адресной шины микропроцессора), для работы 55 необходимо сформировать рабочую страницу памяти, равную по объему прямоадресуемой памяти и содержащую 2м блоков, памяти. Страница организуется таким образом, что от каждой строки накопителя берется только один блок памяти (тот, который нужен на данном этапе вычислений). Формирование рабочей страницы осуществляется программным способом с помощью дешифратора 4 и регистров 5. Эти. регистры являются программнодоступными, так как их информационные входы связаны с ин-. формационными разрядами системой шины 1, а посредством второго дешифратора 4 их входы записи связаны с адресными разрядами системой шины 1. Каждый из регистров 5 имеет свой адрес, поэтому с помощью двух команд процессора в эти регистры может быть записан соответствующий унитарный код (содержащий только одну единицу, все остальные разряды - нули) номера нужного блока памяти. В микропроцессоре К580ВМ80 для записи кода в один регистр необходимы две команды: MV A, NOM; STAADRRi,

где NOM - номер нужного блока 2 памяти (в унитарном коде);

ADRRi - адрес 1-го регистра.

После записи кода в регистр только на одном из его выходов будет присутствовать разрешающий потенциал. Аналогичным образом записываются соответствующие коды в регистры 5 всех строк матричного накопителя. Процедура формирования рабочей страницы памяти для микропроцессора не требует много времени, так как включение в рабочую страницу одного блока памяти производится за время около 10 мкс.

После программирования рабочей страницы начинается работа микропроцессора по программе обработки. Процессору доступен любой блок памяти, входящий в сформированную рабочую страницу памяти.

Микропроцессор выставляет адрес на адресные разряды системной шины 1. Дешифратор 3, используя М старших разрядов адреса, формирует сигнал дешифрации на одном из своих выходов, Если сигнал дешифрации с дешифратора 3 поступает на одну из строк базового накопителя, т.е. на первые входы выборки блоков 2 памяти, то в этой строке будет выбран только один блок 2 памяти, а именно тот, который включен в рабочую страницу (т.е. тот, на второй вход выборки которого заведен разрешающий сигнал с выхода регистра 5). Микропроцессор в этом случае прочитает или запишет нужную информацию в выбранный блок 2 памяти, подав соответственно сигнал чтения или записи на соответствующий разряд системной шины 1.

Если сигнал дешифрации с дешифратора 3 поступает на одну из строк информационного накопителя, то он попадает на первый вход первого элемента И 16 блоха 8 управления (фиг.2). Если на второй вход пер- вого элемента И 16 поступает низкий потенциал с прямого выхода триггера 19 (т.е. в данный момент времени данная строка информационного накопителя не работает со своим каналом прямого доступа), то на вы- ходе первого элемента И 16 имеется низкий потенциал (фиг.З.д, момент времени ts). В момент времени te по положительному фронту инверсного сигнала синхронизации (фиг.З.е) на прямом выходе первого триггера 18 формируется сигнал низкого уровня (фиг.3,е интервал времени te-tp), который поступает на входы выборки ключевого элемента б и регистра 5 и открывает их. Одновременно с инверсного выхода триггера 18 сигнал высокого уровня через элемент ИЛИ 20 (фиг.З.ж, интервал времени te-tg) поступает на первые входы выборки блоков 2 памяти. При этом через ключевой элемент 6 локальная шина данной строки информаци- онного накопителя подключается к системной шине 1, выходы регистра 5 переходят из высокоимпедансного в открытое состояние (выходы дешифратора 7 при этом находятся в высокоимпедансном состоя- нии), один из выходов имеет разрешающий потенциал, в результате чего соответствующий блок 2 памяти данной строки выбирается. Микропроцессор может обращаться к этому блоку памяти с целью записи или чтения информации, выставляя соответственно сигнал записи или чтения на соответствующий разряд системной шины 1. В момент времени te микропроцессор снимает установленный адрес с адресных разрядов (или устанавливает другой), дешифратор 3 снимает сигнал дешифрации и цикл обращения микропроцессора к данной строке заканчивается.

Канал прямого доступа к памяти со свободной строкой информационного накопителя (т.е. со строкой, к которой в данный момент времени не обращается микропроцессор) работает следующим образом.

i-й контроллер прямого доступа к памяти выставляет сигнал высокого уровня Запрос захвата на вход 13 1-й строки информационного накопителя (фиг.З, в, мо- мент времени ti). Этот сигнал поступает не на микропроцессор, а на вход второго элемента И 17 блока 8 управления. В это время на другом входе элемента И 17 присутствует высокий потенциал с прямого выхода триггера 18, поэтому на D-вход триггера 19 поступает сигнал высокого уровня. В момент времени t2 по положительному фронту прямого сигнала синхронизации (фиг.З, о) на прямом выходе триггера 19 сформируется высокий потенциал (фиг.З, г, интервал времени tz-fcs), такой же длительности сигнал высокого уровня формируется и на выходе элемента ИЛИ 20. Сигнал с прямого выхода триггера 19 в виде сигнала Подтверждение захвата поступает через выход 14 на соответствующий вход контроллера ПДП и разрешает его работу. При этом инверсный сигнал от сигнала Подтверждение захвата (с инверсного выхода триггера 19) поступает на вход выборки дешифратора 7 и открывает его выходы. Выходы регистра 5 в данный интервал времени находятся в высокоимпедансном состоянии. Контроллер ПДП на адресные разряды локальной шины 10 выставляет адрес, М старших разрядов которого заведены на дешифратор 7. Результатом дешифрации будет разрешающий сигнал на одном из выходов дешифратора 7, вследствие чего один блок 2 памяти данной строки (на второй вход выборки которого поступает разрешающий сигнал дешифратора 7) будет выбран, так как на первые входы выборки блоков 2 памяти поступает разрешающий сигнал с выхода элемента ИЛИ 20 блока 8 управления (фиг.2). Контроллер ПДП таким образом может вести обмен информацией с любым блоком памяти своей строки информационного накопителя, меняя коды на адресных разрядах локальной шины 10. Адресация блоков 2 памяти в строке для контроллера ПДП горизонтальна, а именно первый (левый) блок имеет начальные адреса (начиная с нуля), а последний (крайний правый) - последние адреса адресного пространства, в то время как для микропроцессора каждый блок 2 памяти строки занимает одно и то же адресное пространство (адресация строк для микропроцессора вертикальная).

Канал прямого доступа с занятой строкой информационного накопителя работает следующим образом.

Если с данной строкой информационного накопителя микропроцессор, а в это время контроллер ПДП еыставляетсиг- нал Запрос захвата (фиг.З,в, момент времени t), то этот сигнал поступит на вход элемента И 17. Так как в данный момент времени на прямом выходе триггера 18 присутствует низкий потенциал, на входах элемента И 17 совпадения высоких потенциалов не произойдет, на его выходе будет низкий потенциал и триггер 19 останется в нулевом состоянии. По окончании работы

икропроцессора с данной строкой инфорационного накопителя дешифратор 3 сниет сигнал низкого уровня (фиг.З.д, момент e), через небольшую задержку (фиг.З.е, tg), а прямом выходе триггера 18 установится ысокий потенциал, который поступит на ход элемента И 17. На D-вход триггера 19 оступит высокий потенциал и в момент ремени tio на его прямом выходе и на вы- ходе элемента ИЛИ 20 появится высокий 10 потенциал, т.е. сигнал Подтверждение захвата (фиг.3,г,ж). Канал ПДП произведет Пересылку информации и в момент времени tn снимет сигнал Запрос захвата. В момент времени На триггер 19 переключится и 15 на его прямом выходе установится сигнал низкого уровня.

Микропроцессор с занятой строкой информационного накопителя работает следу- 20 Ющим образом.

Если с данной строкой информационного накопителя работает контроллер ПДП и приходит запрос от микропроцессора (фиг,3, д, времени tis), то этот сигнал посту- 25 пает на вход элемента И 16 и на вход эле- мента И 21. Так как на прямом выходе триггера 19 присутствует высокий потенциал, то элемент И 16 будет закрыт, на прямом выходе триггера 18-высокий потенциал. На 30 входах элемента И 21 присутствуют два сигнала низких уровней, значит, и на его выходе будет сигнал низкого уровня. Этот сигнал через многовходовый элемент ИЛИ 9 и выход 12 устройства поступит на вход Готов- 35 Ность микропроцессора, в результате чего микропроцессор остановится, т.е. перейдет в режим бжидания и будет находиться в этом состоянии до момента времени ti, т.е. пока канал ПДП не закончит работу (фиг.З, 40 3). В момент времени tie контроллер ПДП Снимет сигнал Запрос захвата, в момент времени tn переключится в нулевое состояние триггер 19, высокий потенциал с его инверсного выхода закроет элемент И 21, а 45 низким потенциалом прямого выхода триггера 19 откроется элемент И 16. В момент времени tis переключится триггер 18 и далее работа микропроцессора будет происходить так, как было описано выше, т.е. 50 микропроцессор будет работать с данной строкой информационного накопителя на интервале времени tie-tig.

Таким образом, канал ПДП и микропро- 55 цессор могут работать в одно и то же время, но с разными строками накопителей (в отличие от прототипа, в котором по сигналу Запрос захвата от канала ПДП микропроцессор .отключается, т.е. переводит

свои шины данных и адреса в высокоимпен- дансное состояние, а сам переходит в режим ожидания). В предлагаемом устройстве конфликтные ситуации возникают только в том случае, если к одной и той же строке информационного накопителя одновременно обращаются микропроцессор и соответствующий контроллер ПДП. В этом случае один из них захватывает инициативу (так как триггеры 18 и 19 тактируются противофазными сериями импульсов), а другой из них ожидает конца работы первого, после чего сам работает с данной страницей памяти.

Ф о р м у л а и з о б р е т е н и я Запоминающее устройство, содержащее блоки памяти, объединенные в матрицу основного и дополнительного накопителей, первый и второй дешифраторы, регистры строк, ключевые элементы, соответствующие информационные входы-выходы блоков памяти основного накопителя объединены и соединены с информационными входами регистров строк и являются информационными входами-выходами первой группы устройства, соответствующие адресные входы блоков памяти основного накопителя объединены и являются адресными входами второй группы устройства, входы записи-считывания блоков памяти основного накопителя объединены и являются первым входом записи-считывания устройства, соответствующие информационные входы-выходы блоков памяти дополнительного накопителя объединены, соединены с входами регистра строк и являются информационными входами-выходами второй группы устройства, соответствующие адресные входы блоков памяти дополнительного накопителя объединены и являются адресными входами третьей группы устройства, входы записи-считывания блоков памяти дополнительного накопителя объединены и являются вторым входом записи-считывания устройства, входы первого дешифратора являются адресными входами первой группы устройства, входы второго дешифратора соединены с адресными входами второй группы устройства, управляющий вход второго дешифратора соединен с первым входом записи-считывания устройства, первые входы выборки блоков памяти каждой строки основного накопителя объединены и соединены с соответствующими выходами первого дешифратора, выходы второго дешифратора соединены с входами синхронизации соответствующих регистров строк основного и дополнительного блоков памяти, выходы регистров соединены с вторыми

входами выборки соответствующих блоков памяти основного и дополнительного накопителей, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены элемент ИЛИ, а в 5 каждую строку дополнительного накопителя-дешифратор строки, блок управления, ключевой элемент, первые информационные входы-выходы ключевого элемента соединены с

хвата соответствующего канала прямого доступа к памяти устройства, вход синхронизации блока управления является одноименным входом устройства, первый выход блока управления соединен с входами задания режима ключевого элемента и регистра строк, второй выход блока управления соединен с первыми входами выборки блоков памяти дополнительного

информационными входами-выходами вто- 10 накопителя, третий выход блока управле- рой группы устройства, адресными входа- ния является выходом Подтверждение захвата соотвеютвующего канала прямого доступа к памяти, четвертый выход блока

управления соединен с управляющим вхоми третьей группы устройства, вторым

входом записи-считьГвания устройства,

вторые информационные входы-выходы

ключевого элемента соединены с ин- 15 дом дешифратора строк, входы дешифратоформационными входами-выходами ра строк соединены с адресными входами

первой группы устройства, адресными

входами второй группы устройства, первым входом записи-считывания устройтретьей группы устройства, выходы дешифратора строк - с соответствующими выходами регистра строк дополнительного блока ства, вход задания режима блока 20 памяти, пятый выход блока управления сое- управления соединен с соответствующим динен с одним из входов эт мента ИЛИ, выходом первого дешифратора, вход Запрос захвата является входом Запрос

выход которого является выходом Готовность устройства.

хвата соответствующего канала прямого доступа к памяти устройства, вход синхронизации блока управления является одноименным входом устройства, первый выход блока управления соединен с входами задания режима ключевого элемента и регистра строк, второй выход блока управления соединен с первыми входами выборки блоков памяти дополнительного

управления соединен с управляющим вхотретьей группы устройства, выходы дешифратора строк - с соответствующими выходами регистра строк дополнительного блока 20 памяти, пятый выход блока управления сое- динен с одним из входов эт мента ИЛИ,

К1

выход которого является выходом Готовность устройства.

: #7 л

ля

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1987 |

|

SU1460740A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для регенерации динамической памяти | 1980 |

|

SU943845A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

| Устройство сопряжения с памятью | 1985 |

|

SU1262515A1 |

| Запоминающее устройство с произвольной выборкой | 1988 |

|

SU1548790A1 |

| Станция локальной вычислительной сети | 1990 |

|

SU1805474A1 |

| ЭВМ | 1990 |

|

RU2024928C1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1352477A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

Изобретение относится к вычислительной технике, к запоминающим устройствам и может быть использовано в микропроцессорной технике Цель изобретения - повышение быстродействия устройства. К нихропроцкеору Запоминающее устройство содержит системную шину 1, блоки 2 памяти, дешифраторы 3 и 4, регистры 5,. ключевой, элемент 6, дешифратор 7, блок 8 управления локальной шиной, элемент ИЛИ 9, локальную шину 10 контроллера прямого доступа к памяти, вход 11 синхронизации выход 12 Готовность, вход 13 Запрос захвата, выход 14 Подтверждение захвата В устройстве возможна одновременная работа одного или нескольких каналов прямого доступа к памяти и микропроцессора Это стало возможным благодаря тому, что сигналы Запрос захвата от каналов прямого доступа подаются не на вход микропроцессора, а на соответствующий вход блока управления, который вместо микропроцессора вырабатывает сигнал Подтверждение захвата 3 ил СП С о ю 01 со 00 го Kt ну о, t. Фиг I

фиг.1

ff.-Tl-pJl JT

5 u jrir{jr jrijr

ИI | I I | I

| Циделко В.Д идр Проектирование микропроцессорных измерительных приборов и систем | |||

| - Киев Техника, 1984, с 37-39, рис.22 | |||

| Запоминающее устройство | 1987 |

|

SU1460740A1 |

Авторы

Даты

1991-11-30—Публикация

1989-03-02—Подача