Фиг.

Изобретение относится к радиотехнике и связи и может быть использовано в измерительной технике.

Целью изобретения является повышение точности умножения частоты.

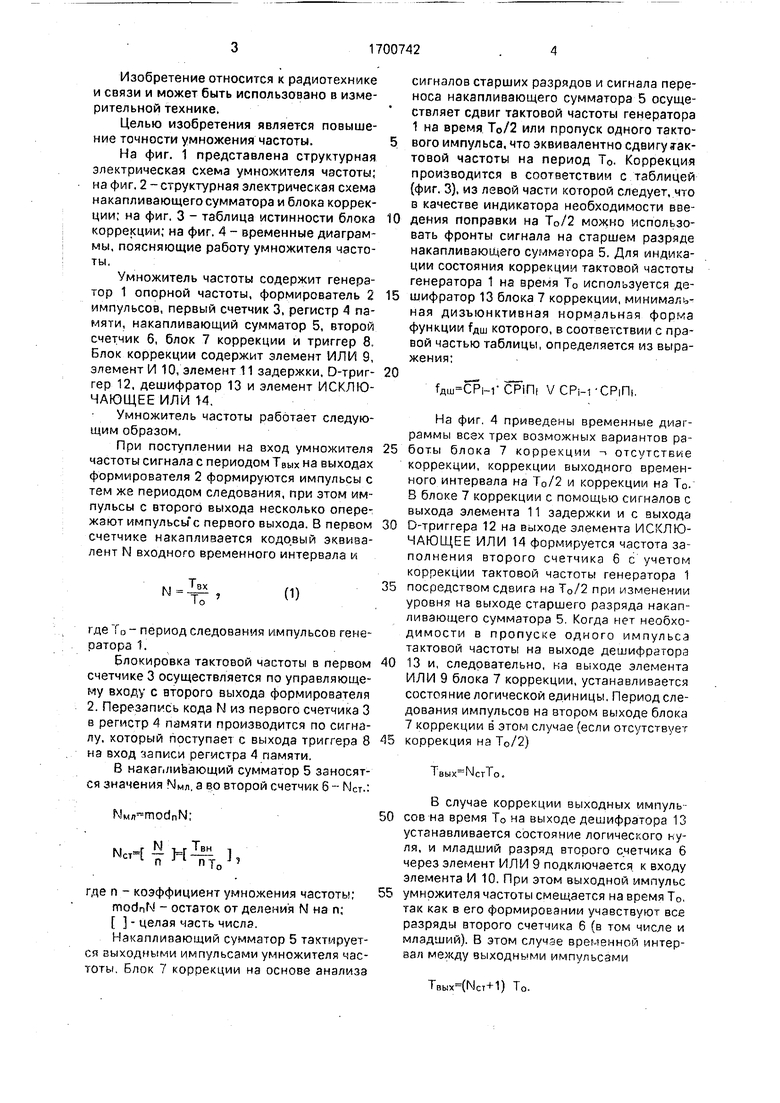

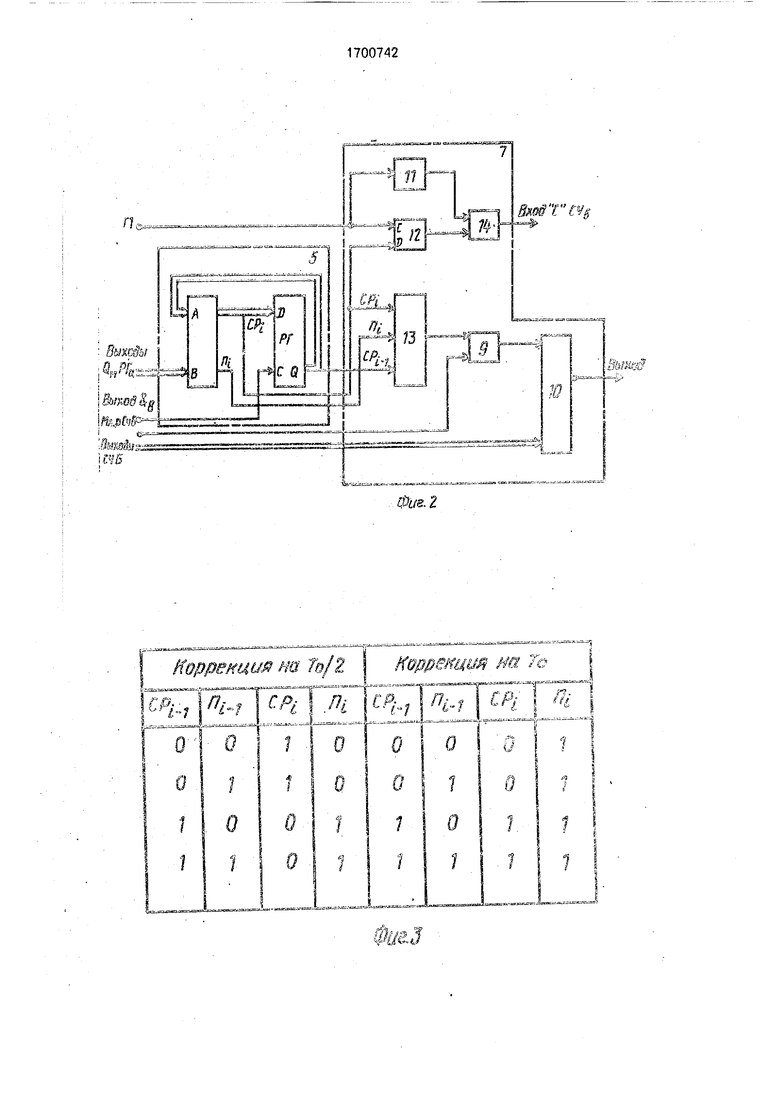

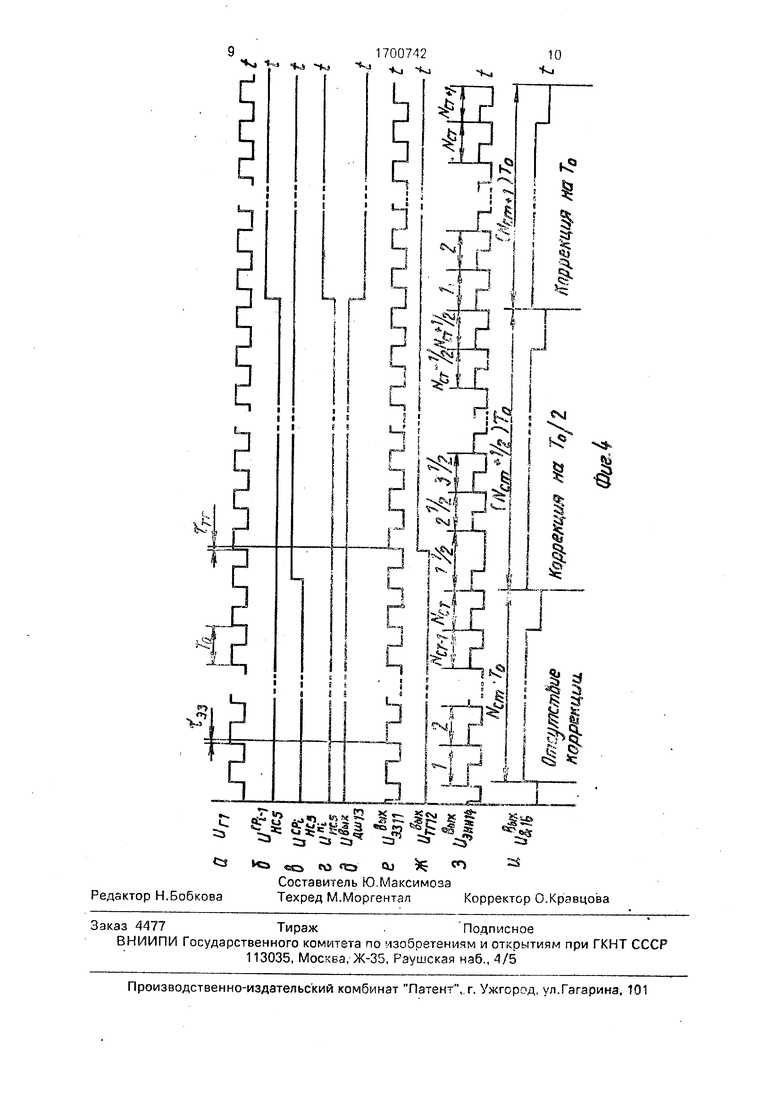

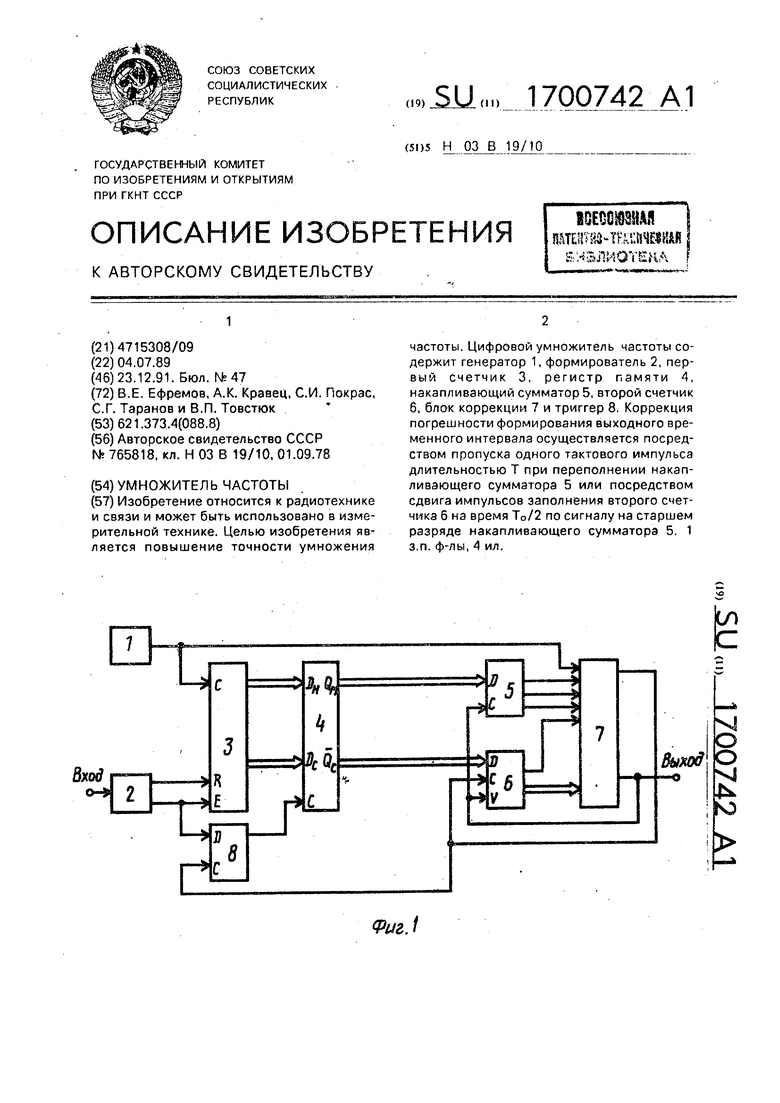

На фиг. 1 представлена структурная электрическая схема умножителя частоты; на фиг. 2 - структурная электрическая схема накапливающего сумматора и блока коррекции; на фиг. 3 - таблица истинности блока коррекции; на фиг. А - временные диаграммы, поясняющие работу умножителя частоты.

Умножитель частоты содержит генератор 1 опорной частоты, формирователь 2 импульсов, первый счетчик 3, регистр 4 памяти, накапливающий сумматор 5, второй счетчик б, блок 7 коррекции и триггер 8. Блок коррекции содержит элемент ИЛИ 9, элемент И 10, элемент 11 задержки, D-триг- гер 12, дешифратор 13 и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 14.

Умножитель частоты работает следующим образом.

При поступлении на вход умножителя частоты сигнала с периодом Твых на выходах формирователя 2 формируются импульсы с тем же периодом следования, при этом импульсы с второго выхода несколько опережают импульсьГс первого выхода. В первом счетчике накапливается кодовый эквивалент N входного временного интервала и

N н

N To

(D

где То - период следования импульсов генератора 1.

Блокировка тактовой частоты в первом счетчике 3 осуществляется по управляющему входу с второго выхода формирователя 2. Перезапись кода N из первого счетчика 3 в регистр 4 памяти производится по сигналу, который поступает с выхода триггера 8 на вход записи регистра 4 памяти.

8 накапливающий сумматор 5 заносятся значения NM/I, а во второй счетчик 6 - NCT.:

NMfl™modnN;

NcT«r а н- 1

п Л n To J ,

где п - коэффициент умножения частоты;

modnN - остаток от деления N на п;

- целая часть числа.

Накапливающий сумматор 5 тактируется выходными импульсами умножителя частоты. Блок 7 коррекции на основе анализа

сигналов старших разрядов и сигнала переноса накапливающего сумматора 5 осуществляет сдвиг тактовой частоты генератора 1 на время То/2 или пропуск одного тактового импульса, что эквивалентно сдвигу тактовой частоты на период Т0. Коррекция производится в соответствии с таблицей (фиг. 3), из левой части которой следует, что з качестве индикатора необходимости введения поправки на Т0/2 можно использовать фронты сигнала на старшем разряде накапливающего сумматора 5. Для индикации состояния коррекции тактовой частоты генератора 1 на время Т0 используется дешифратор 13 блока 7 коррекции, минимальная дизъюнктивная нормальная форма функции тдш которого, в соответствии с правой частью таблицы, определяется из выражения:

20

CPIFli VCPi-rCPini.

На фиг. 4 приведены временные диаграммы всех трех возможных вариантов работы блока 7 коррекции - отсутствие коррекции, коррекции выходного временного интервала на То/2 и коррекции на Т0. В блоке 7 коррекции с помощью сигналов с выхода элемента 11 задержки и с выхода

D-триггера 12 на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14 формируется частота заполнения второго счетчика 6 с учетом коррекции тактовой частоты генератора 1

посредством сдвига на Т0/2 при изменении уровня на выходе старшего разряда накапливающего сумматора 5. Когда нет необходимости в пропуске одного импульса тактовой частоты на выходе дешифратора

13 и, следовательно, на выходе элемента ИЛИ 9 блока 7 коррекции, устанавливается состояние логической единицы. Период следования импульсов на втором выходе блока 7 коррекции в этом случае (если отсутствует

коррекция на Т0/2)

,

В случае коррекции выходных импуль- сов на время Т0 ча выходе дешифратора 13 устанавливается состояние логического нуля, и младший разряд второго счетчика 6 через элемент ИЛИ 9 подключается к входу элемента И 10. При этом выходной импульс умножителя частоты смещается на время То. так как в его формировании учавствуют все разряды второго счетчика 6 (в том числе и младший). В этом случае временной интервал между выходными импульсами

Твых(ст+1) То.

После прихода 1-го импульса с выхода умножителя частоты код, записанный в накапливающем сумматоре 5, определяется из выражения

Мсмг тосЬ Ммл 1,

Количество корректирующих сдвигов импульсов выходной частоты на время Т0/2, произведенной блоком 7 коррекции, к этому

моменту времени равно -- (поправка

на Т0 эквивалентна двум сдвигам на Т0/2), Тогда время ti появления 1-го выходного импульса определяется следующим образом.

1 KI -г i ч То

t| iNCT To + -- } --гр,

Формула изобретения, 1. Умножитель частоты, содержащим последовательно соединенные генератор опорной частоты, первый счетчик, регистр памяти и второй счетчик, формирователь импульсов, триггер и накапливающий сумматор, информационный вход которого сое- дин-ен с выходом младших разрядов регистра памяти, при этом первый выход формирователя импульсов соединен с входом начальной установки первого счетчика, а второй выход формирователя импульсов соединен с управляющим входом первого счетчика и с D-входом триггера, выход которого соединен с входом записи регистра памяти, отл и ч а ю щи и с я тем, что, с целью повышения точности умножения частоты, введен блок коррекции, первый выход которого соединен с синхронизирующими входами второго счетчика и триггера, выход генератора опорной частоты соединен с первым входом блока коррекции, второй, третий и четвертый входы которого соеди- нены соответственно с выходом старшего разряда, выходом переноса и выходом задержанного . разряда накепливаю- щего сумматора, пяшй вход б |ока коррекции соединен с выходом младшего

разряда второго счетчика, выход старших разрядов ксгорсгс соединен с шестым входом блока короеки/ш, при этом второй выход бяокз коррекиии соединен с синхррнизируюшим входом нзкапливающего сумматора с установочным входом вюоого счетчика и являете выходом умножителя астоты.

2. Умножитель поп. 1,отличающи- й с я тем, что блок коррекции содержит

последовательно соединенные элемент задержки и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, последовательно соединенные дешифратор, элемент ИЛИ и элемент И и D-триггер, выход которого соединен с вторым входом

элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, при этом вход элемента задержки соединен с синхронизирующие входом D-триггера и является первым входом блока коррекции, D-вход D- трмггера соединен с первым еходом дешифратора и является вторым входом блока коррекции, второй и третей входы дешифратора являются соответственно третьим и четвертым входами олска коррекции, вто рой вход элемента ИЛИ и второй вход элемента И являются соответственно пятым и шестым входами блока коррекции, выход элемента ИСКЛ ОЧАЮЩЕЕ ИЛИ и выход элемента И ЯВЛЯКУГСЯ соответственно первым и аторым выходами блока коррекции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки данных при формировании диаграммы направленности антенной решетки | 1987 |

|

SU1462351A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Устройство для реализации быстрого преобразования Хартли | 1987 |

|

SU1444815A1 |

| Умножитель частоты следования периодических импульсов | 1980 |

|

SU980094A1 |

| Умножитель частоты | 1990 |

|

SU1797113A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 2013 |

|

RU2534971C1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Устройство для обработки радиосигналов | 1980 |

|

SU955083A1 |

Изобретение относится к радиотехнике и связи и может быть использовано в измерительной технике. Целью изобретения является повышение точности умножения частоты. Цифровой умножитель частоты содержит генератор 1, формирователь 2, первый счетчик 3. регистр памяти 4, накапливающий сумматор 5, второй счетчик 6, блок коррекции 7 и триггер 8. Коррекция погрешности формирования выходного временного интервала осуществляется посредством пропуска одного тактового импульса длительностью Т при переполнении накапливающего сумматора 5 или посредством сдвига импульсов заполнения второго счетчика 6 на время Т0/2 по сигналу на старшем разряде накапливающего сумматора 5. 1 з.п. ф-лы, 4 ил.

Ъ

4ft

9-1

V

Vj

1ч I l-J

и

5ЙЛ

M

JO у

2/

I/

2t iOOil

1 -KJ

1

t i i

t t i t i

к51

JL

г t i

«-а

1700742 -KI

§J f

4 i

| Умножитель частоты | 1978 |

|

SU765818A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-12-23—Публикация

1989-07-04—Подача