1

(21)4813305/24 (22) 10.04.90 (46)15.12.91. Бюл. № 46

(71)Одесский политехнический институт

(72)А.В.Дрозд, Е.Л.Полин,- В.Н.Огинский и Ю.В.Дрозд (53)681.325(088.8)

(56) Авторское свидетельство СССР № 959069, кл. G 06 F 7/50, 1980.

Преснухин Л.Н., Нестеров П.В. Цифровые вычислительные машины. М.: Высшая школа, 1974, с.138, рис.3.33.

-(54) УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ЧИСЕЛ

(57) Изобретение относится к вычислительной технике и может быть использовано при построении арифметических блоков ЭВМ. Целью изобретения является расширение функциональных возможностей устройства путем сложения положительных и отрицательных чисел. Устройство для сложения и вычитания чисел содержит регистр 1, сумматоры 2 и триггеры 3, соединенные между собой функционально. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления модуля комплексного числа | 1990 |

|

SU1753472A1 |

| Устройство для возведения в квадрат | 1988 |

|

SU1534458A2 |

| Накапливающий сумматор | 1990 |

|

SU1829031A1 |

| Устройство для деления чисел на константу 2 @ - 1 | 1990 |

|

SU1741130A1 |

| Устройство для деления чисел на константу 2 @ + 1 | 1990 |

|

SU1746379A1 |

| УСТРОЙСТВО ДЛЯ СВЕРТКИ ПО МОДУЛЮ ТРИ | 1991 |

|

RU2011215C1 |

| Устройство для деления на константу 2 @ - 1 | 1990 |

|

SU1714596A1 |

| Устройство для преобразования двоично-десятичных чисел в двоичные | 1988 |

|

SU1557680A2 |

| Устройство для деления чисел на константу типа 2 @ + 1 | 1990 |

|

SU1791813A1 |

| Устройство для параллельного счета количества единиц в двоичном п-разрядном коде | 1989 |

|

SU1711165A1 |

w

Ј

о ю со

00 00

VJ

Изобретение относится к вычислительной технике и может быть использовано в арифметических блоках ЭВМ.

Известен одноразрядный накапливающий сумматор, содержащий элементы И, схему задержки, элементы ИЛИ и Т-триггер.

Недостатками такого устройства являются ограниченные функциональные возможности вследствие накопления суммы только двух положительных чисел.

Известен комбинационный последовательный сумматор, содержащий первый сумматор группы (сумматор), первый триггер группы (схема П), регистр (регистр 1-го слагаемого), регистр 2-го слагаемого и регистр результата, причем выход регистра подключен к первому входу сумматора группы, второй вход которого соединен с выходом регистра 2-го слагаемого, выход переноса соединен с выходом первого триггера группы, информационный вход которого подключен к выходу переноса первого сумматора группы, выход суммы которого соединен с входом регистра результата, выход которого является выходом устройства.

Недостатками известного устройства являются ограниченные функциональные возможности вследствие получения суммы только двух положительных чисел.

Цель изобретения - расширение функциональных возможностей устройства путем сложения tчисел: m положительных и п отрицательных (т + п « ).

Указанная цель достигается тем, что в устройство, содержащее регистр, первый сумматор группы и первый триггер группы, причем выход регистра соединен с первым входом первого сумматора группы, выход переноса которого соединен с информационным входом первого триггера группы, выход которого соединен с входом переноса первого„сумматора группы, введены с второго по {-и сумматоры группы и с второго по &й триггеры группы, причем вход режима регистра объединен с входами сброса триггеров группы и является входом начальной установки устройства, синхровход регистра объединен с синхровходами триггеров группы и является тактовымвходом устройства, информационные входы регистра являются входами кода п устройства, выходы суммы всех предыдущих сумматоров группы соединены с первыми входами последующих сумматоров группы, вторые входы сумматоров группы являются входами соответствующих слагаемых устройства, выходы переноса сумматоров группы с второго по t-й подключены к информационным входам соответствующих триггеров группы, выходы которых соединены с входами переноса соответствующих сумматоров группы, выход суммы Е-го сумматора группы является выходом устройства.

Предполагаемое изобретение соответствует критерию существенные отличия поскольку содержит по сравнению с известными решениями дополнительно сумматоры группы и триггеры группы, которые в совокупности с введенными связями обес0 печивают сложение m положительных и п отрицательных чисел, что расширяет функциональные возможности устройства.

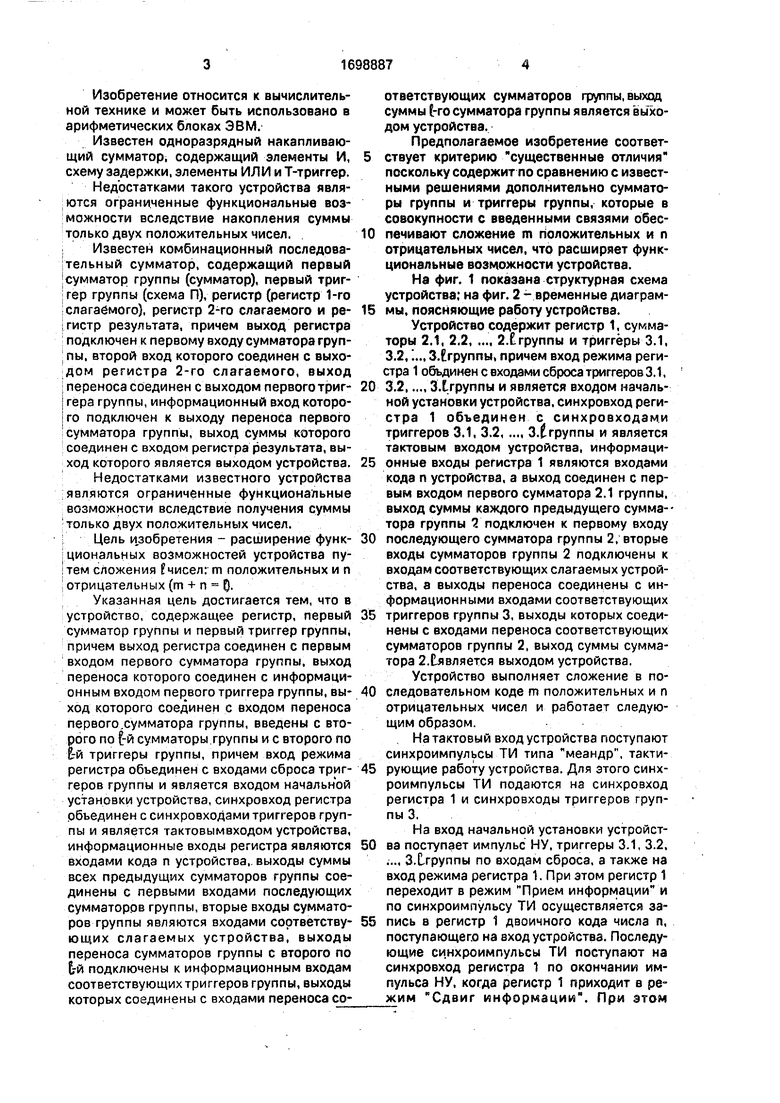

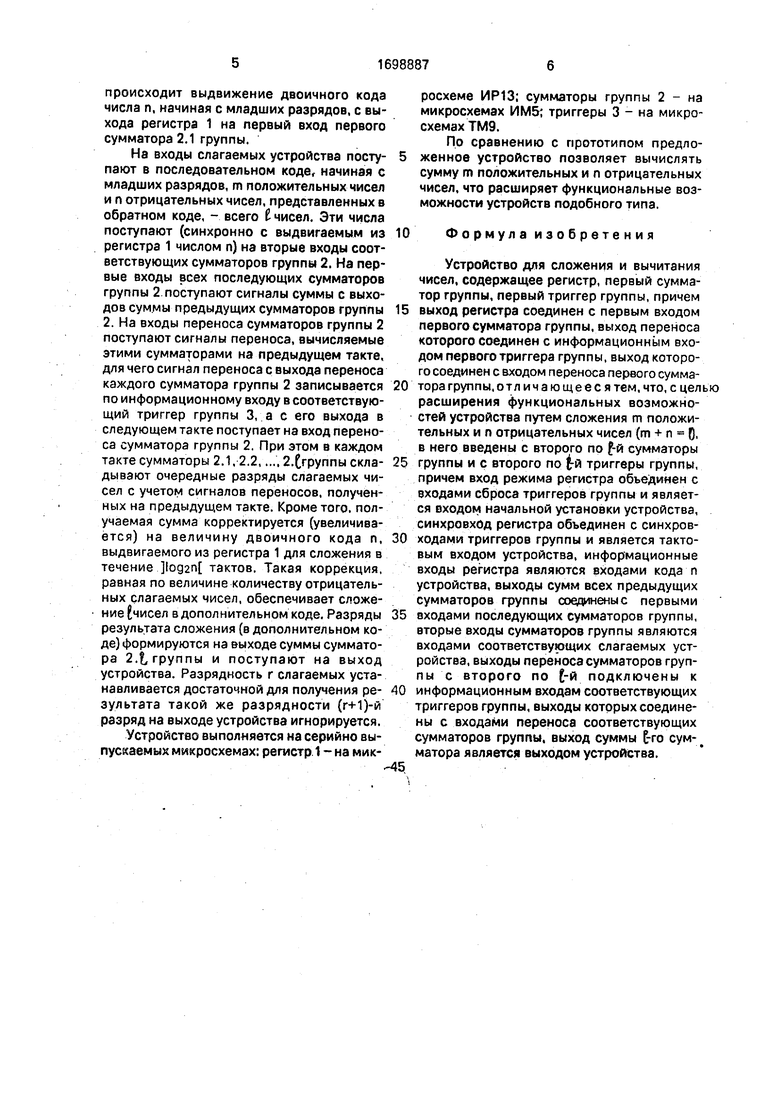

На фиг. 1 показана структурная схема устройства; на фиг. 2 - временные диаграм5 мы, поясняющие работу устройства.

Устройство содержит регистр 1, сумматоры 2.1, 2.22.Ј группы и триггеры 3.1,

0 3.23.1 группы и является входом начальной установки устройства, синхровход регистра 1 объединен с синхровходами

триггеров 3.1, 3.2З.Јгруппы и является

тактовым входом устройства, информаци5 онные входы регистра 1 являются входами кода п устройства, а выход соединен с первым входом первого сумматора 2.1 группы, выход суммы каждого предыдущего сумма-- тора группы 2 подключен к первому входу

0 последующего сумматора группы 2, вторые входы сумматоров группы 2 подключены к входам соответствующих слагаемых устройства, а выходы переноса соединены с информационными входами соответствующих

5 триггеров группы 3, выходы которых соединены с входами переноса соответствующих сумматоров группы 2, выход суммы сумматора 2.Јявляется выходом устройства.

Устройство выполняет сложение в по0 следовательном коде m положительных и п отрицательных чисел и работает следующим образом.

На тактовый вход устройства поступают синхроимпульсы ТИ типа меандр, такти5 рующие работу устройства. Для этого синхроимпульсы ТИ подаются на синхровход регистра 1 и синхровходы триггеров группы 3.

На вход начальной установки устройст0 ва поступает импульс НУ, триггеры 3.1, 3.2, ..., З.Сгруппы по входам сброса, а также на вход режима регистра 1. При этом регистр 1 переходит в режим Прием информации и по синхроимпульсу ТИ осуществляется за5 пись в регистр 1 двоичного кода числа п, поступающего на вход устройства. Последующие синхроимпульсы ТИ поступают на синхровход регистра 1 по окончании импульса НУ, когда регистр 1 приходит в режим Сдвиг информации. При этом

происходит выдвижение двоичного кода числа п, начиная с младших разрядов, с выхода регистра 1 на первый вход первого сумматора 2.1 группы.

На входы слагаемых устройства посту- пают в последовательном коде, начиная с младших разрядов, m положительных чисел и п отрицательных чисел, представленных в обратном коде, - всего I чисел. Эти числа поступают (синхронно с выдвигаемым из регистра 1 числом п) на вторые входы соответствующих сумматоров группы 2. На первые входы всех последующих сумматоров группы 2 поступают сигналы суммы с выходов суммы предыдущих сумматоров группы 2. На входы переноса сумматоров группы 2 поступают сигналы переноса, вычисляемые этими сумматорами на предыдущем такте, для чего сигнал переноса с выхода переноса каждого сумматора группы 2 записывается по информационному входу в соответствующий триггер группы 3, а с его выхода в следующем такте поступает на вход переноса сумматора группы 2. При этом в каждом

такте сумматоры 2.1, 2.22.Сгруппы скла-

дывают очередные разряды слагаемых чисел с учетом сигналов переносов, полученных на предыдущем такте. Кроме того, получаемая сумма корректируется (увеличивается) на величину двоичного кода п, выдвигаемого из регистра 1 для сложения в течение одгп тактов. Такая коррекция, равная по величине количеству отрицательных слагаемых чисел, обеспечивает сложение Јчисел в дополнительном коде. Разряды результата сложения (в дополнительном коде) формируются на выходе суммы сумматора 2.1, группы и поступают на выход устройства. Разрядность г слагаемых устанавливается достаточной для получения ре- зультата такой же разрядности (г+1)-й разряд на выходе устройства игнорируется.

Устройство выполняется на серийно выпускаемых микросхемах: регистр 1 - на мик

росхеме ИР13; сумматоры группы 2 - на микросхемах ИМ5; триггеры 3 - на микросхемах ТМ9.

По сравнению с прототипом предложенное устройство позволяет вычислять сумму m положительных и п отрицательных чисел, что расширяет функциональные возможности устройств подобного типа.

Формула изобретения

Устройство для сложения и вычитания чисел, содержащее регистр, первый сумматор группы, первый триггер группы, причем выход регистра соединен с первым входом первого сумматора группы, выход переноса которого соединен с информационным входом первого триггера группы, выход которого соединен с входом переноса первого сумматора группы, отличающееся тем, что, с цел расширения функциональных возможностей устройства путем сложения m положительных и п отрицательных чисел (т + п 0, в него введены с второго по Јй сумматоры группы и с второго по Јй триггеры группы, причем вход режима регистра объединен с входами сброса триггеров группы и является входом начальной установки устройства, синхровход регистра объединен с синхров- ходами триггеров группы и является тактовым входом устройства, информационные входы регистра являются входами кода п устройства, выходы сумм всех предыдущих сумматоров группы соединены с первыми входами последующих сумматоров группы, вторые входы сумматоров группы являются входами соответствующих слагаемых устройства, выходы переноса сумматоров груп- пы с второго по t-й подключены к информационным входам соответствующих триггеров группы, выходы которых соединены с входами переноса соответствующих сумматоров группы, выход суммы {-то сумматора является выходом устройства.

фиг. 1

Авторы

Даты

1991-12-15—Публикация

1990-04-10—Подача