Изобретение относится к вычислительной технике и может быть использовано в арифметических блоках ЭВМ.

Известно устройство для деления, содержащее сумматор, регистр делимого, регистр делителя и матрицу умножения,

Недостатком устройства является его сложность.

Наиболее близким к поедлагаемому является устройство для деления чисел на константу (2-1), содержащее сумматор, регистр делимого, элемент НЕ, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, две группы элементов И, промежуточный регистр и элемент И, причем входы разрядов делимого устройства соединены с информационными входами соответствующих разрядов регистра делимого, выходы старших разрядов сумматора с (FH)-ro по n-й (где п - разрядность делимого) соединены с первыми входами элементов И первой группы соответственно с первого по (n-Q-й, а выходы разрядов первого сумматора с (Ј+1)-го по (п+1)-й соедине- ны с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы соответственно с первого по (п-(1)-й промежуточного регистра, синхровход которого соединен

с тактовым входом-устройства, а вход сброса - с синхровходом регистра делимого и входом запуска устройства, выходы разрядов регистра делимого и промежуточного регистра соединены с входами соответствующих разрядов первого сумматора, выходы разрядов которого с первого по С-й соединены с первыми входами соответствующих элементов И второй группы и входами элемента И, выход которого подключен к вторым входам первого элемента И первой группы и первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы, а также к входу элемента НЕ, выход которого соединен с вторыми входами элементов И второй группы, выходы которых являются выходами дробной части результата устройства, выход каждого элемента И группы соединен с вторым входом последующего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ являются выходами целой части результата устройства.

Недостатком устройства является его низкое быстродействие, обусловленное большой продолжительностьютакта работы устройства.

(Л

С

2

8

Цель изобретения - повышение быстродействия устройства.

Указанная цель достигается тем, что в устройство, содержащее группу сумматоров, группу триггеров, группу регистров, причем информационный вход первого регистра группы является входом делимого устройства, выход i-ro регистра группы (где ,2г, г-точность вычисления результата) соединен с первым входом 1-го суммато- ра группы, выход переноса которого соединен с информационным входом i-ro триггера группы, выход которого соединен с вторым входом i-ro сумматора группы, вход начальной установки устройства сое- динен с входами сброса всех триггеров группы, синхровходы которых соединены с тактовым входом устройства, введены связи: тактовый вход устройства соединен с синхровходами всех регистров группы, вхо- ды сброса которых соединены с входом начальной установки устройства, выход суммы j-ro сумматора г-1) соединен с информационным входом (j+1)-ro регистра группы и третьим входом (j+1)-ro сумматора группы, третий вход первого сумматора группы соединен с входом делимого устройства, выход суммы r-го сумматора группы соединен с выходом результата устройства.

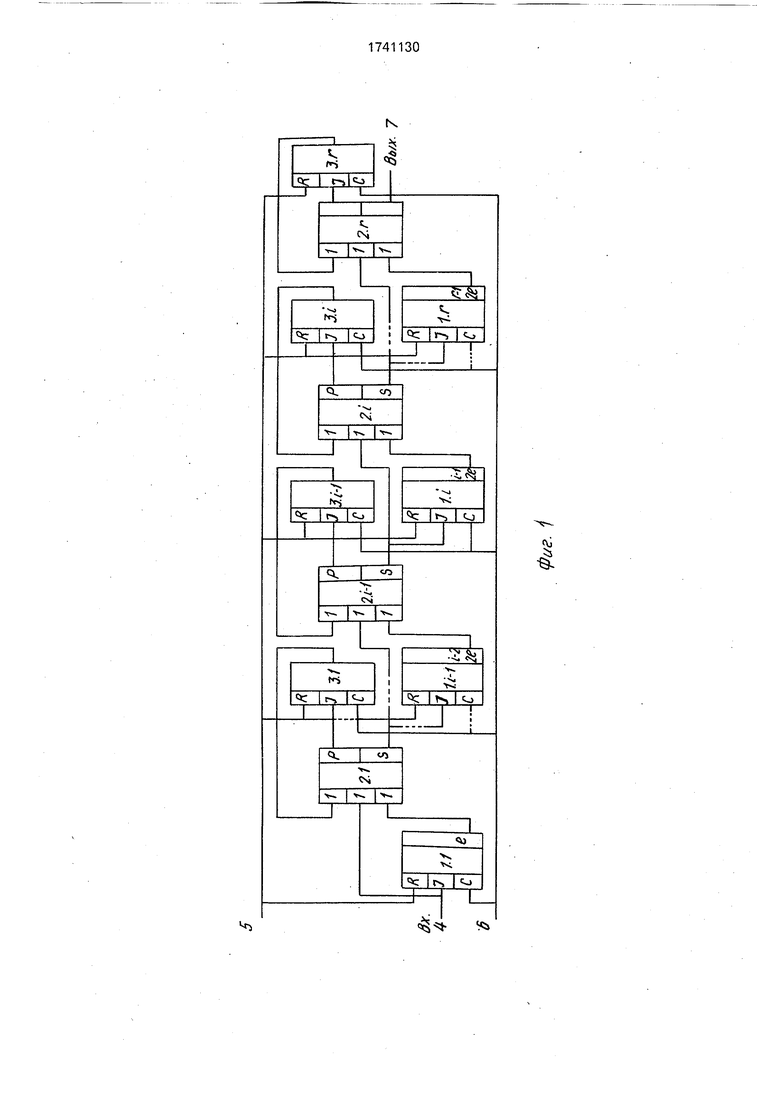

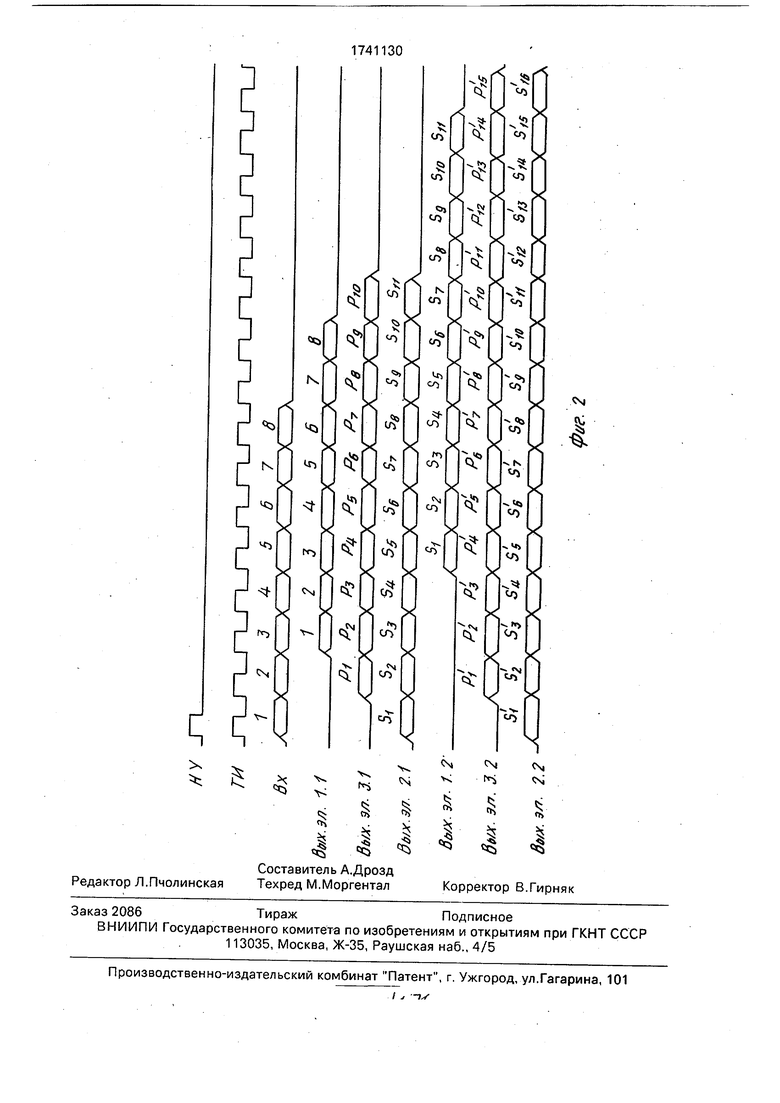

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - временные диаграммы.

Устройство содержит регистры 1.1, ...,

1.г, сумматоры 2,12.г, триггеры 3.1,..., З.г,

вход 4 устройства, вход 5 начальной уста- новки устройства, тактовый вход 6 и выход 7 устройства, причем первый вход сумматора 2.1 и информационный вход регистра 1.1 объединены, образуя вход 4 устройства, первый вход сумматора 2.I объединен с ин- формационным входом регистра 1.1 и под- к выходу суммы сумматора 2.1-1, ,r, выход регистра 1.1 соединен с вторым входом сумматора 2.1, выход переноса которого соединен с информационным входом триггера 3.1, выход которого соединен с третьим входом сумматора 2.i, синхровходы регистра 1.1 и триггера 3.1 объединены, образуя тактовый вход устройства, вход сброса регистра 1.1 и вход сброса триггера 3.1 объединены, образуя вход 5 начальной установки устройства, выход суммы сумматора 2.г является выходом 7 устройства.

Искомое частное X получают из уравнения

А/()Х

или

I A 2VX-X ,

где А - делимое; X - частное;

51015 20 25

30

35 40 4550

55

t - конкретное положительное целое число, (2.

Отсюда следует, что частное X совпадает с делимым, сдвинутым на двоичных разрядов в сторону младших разрядов, при этом имеет место погрешность, которая определяется значением X. Эта погрешность тем меньше, чем больше величина сдвига, т.е. коэффициент при X в формуле (2). Эту величину сдвига можно увеличить, умножая правую и левую части равенства на величину (). Тогда в правой части имеет место выражение (2 М). Дальнейшее увеличение коэффициента достигается умножением правой и левой части на величину (22+1), далее на величину (24L+1), вплоть до умноже7г- (, ния на величину (2 +1),

А()(2а+1)...(22Г 4i)-(22r-1)X (3), где г - количество описанных домножений, дающих в правой части выражения величину (22 -1)Х, что определяет (2rjhn-1) точных разрядов результата.

Устройство вычисляет частное от деления величины А на константу (2-1) путем определения выражения в правой части формулы (3).

В начальный момент времени на вход начальной установки устройства поступает сигнал НУ, сбрасывающий в нулевое состояние регистры 1.11.гитриггеры 3.1З.г.

На тактовый вход устройства поступают синхроимпульсы типа меандр, тактирующие работу устройства. Они подаются на синхровходы регистров 1.11.г и триггеров 3.1З.г.

На вход устройства поступает делимое А в последовательном коде начиная с младших разрядов. Оно подается на первый вход сумматора 2.1 и информационный вход регистра 1.1. Регистр 1.1 является регистром сдвига с разрядностью Ји задерживает делимое А на тактов. С его выхода задержанное делимое А поступает на второй вход сумматора 2.1. Сумматор 2.1 выполняет сложение в последовательном коде делимого А, поданного непосредственно и задержанного на (тактов с учетом переносов, задерживаемых на один такт для учета в следующем такте на триггере 3.1. При этом на выходе суммы сумматора 2.1 формируется величина А(2+1). Полученная величина поступает на следующую часть схемы устройства, составленную, как и предыдущая, из регистра, сумматора и триггера, имеющих номера соответственно 1.2, 2.2, 3.2 и в два раза большую разрядность регистра 1,2, т.е. 2f разрядов.

Таких частей в устройстве г, причем г определяется необходимой точностью вычислений, причем на вход i-й части устройствапоступаетвеличина

()(22f+1)...(22 й+1) с выхода сумматора 2.1-1 (Ы)-й части устройства, 1-я часть устройства составлена из регистра 1.1, сумматора 2.1 и триггера 3.1, причем регистр 1.1 имеет разрядность в два раза большую, чем регистр 1.1-1, т.е. 2 F разрядов.

Величина Т поступает на первый вход сумматора 2.1 непосредственно и на его второй вход через регистр 1 ,i, задерживающий на 2мЈтактов. При этом сумматор 2.i вычисляет их сумму в последовательном коде с учетом переносов, задерживаемых на один такт на триггере 3.1, равную величину

oi-40

Т(-2 +1). Таким образом последняя г-я часть схемы аналогично формирует на выходе суммы сумматора 2.г величину

R {2E+lX22f+1)...(22r П+1)А, равную Х(22 - 1), т.е. искомую величину X, сдвинутую (задержанную) на разрядов с погрешностью в п младших разрядах, равной X. Результатом вычислений принимается (2r-1)t+r старших разрядов из общего количества разрядов получаемой суммы на выходе сумматора 2.г (2r-1)(f+r+n), т.е. п младших разрядов игнорируется.

По сравнению с прототипом предлагаемое устройство обладает более высоким бы- стродействием. Действительно, в прототипе вычисление результата производится нэ п/Јтактов, причем продолжительность каждого такта тп определяется задержкой n-разрядного сумматора, которую можно оценить в задержках одноразрядных сумматоров величиной п. Тогда время Тп получения результата для прототипа определяется как Tn n/t-zh n2/{.

В предлагаемом устройстве вычисляется L(2r-1)(f+r+n) разрядов, на что тратится L тактов. Для получения п точных разрядов величина L должна быть равна 2п (т.к. п

младших разрядов игнорируется). Таким образом результат в предлагаемом устройстве может быть получен за время r , где т - продолжительность такта работы устройства, оцениваемого как время задержки

одного одноразрядного сумматора, т.е. . Из этого следует, чтоТп/Т п/2Ј и при («п значительно повышается быстродействие.

Формула изобретения

Устройство для деления чисел на константу (2-1), содержащее группу сумматоров, группу триггеров, группу регистров, причем информационный вход первого регистра группы является входом делимого устройства, выход 1-го регистра группы (где ,2г, г-точность вычисления результата) соединен с первым входом i-ro сумматора группы, выход переноса которого

соединен с информационным входом i-ro триггера группы, выход которого соединен с вторым входом i-ro сумматора группы, вход начальной установки устройства соединен с входами сброса всех триггеров

группы, синхровходы которых соединены с тактовым входом устройства, отличающееся тем, что, с целью повышения быстродействия устройства, тактовый вход устройства соединен с синхровходами всех

регистров группы, входы сброса которых соединены с входом начальной установки устройства, выход суммы j-ro сумматора

г-1) соединен с информационным

входом (j+1)-ro регистра группы и третьим

входом (j+1)-ro сумматора группы, третий вход первого сумматора группы соединен с входом делимого устройства, выход суммы r-го сумматора группы соединен с выходом результата устройства.

Ц

х Ч

$

CSJ

I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел на константу 2 @ + 1 | 1990 |

|

SU1746379A1 |

| Устройство для деления чисел на константу 2 @ + 1 | 1990 |

|

SU1730624A1 |

| Устройство для деления чисел на константу 2 @ - 1 | 1990 |

|

SU1714594A1 |

| Устройство для сложения и вычитания чисел | 1990 |

|

SU1698887A1 |

| Устройство для деления | 1989 |

|

SU1658149A1 |

| Устройство для деления чисел на константу типа 2 @ + 1 | 1990 |

|

SU1791813A1 |

| Матричное устройство для возведения в квадрат | 1989 |

|

SU1619260A1 |

| Устройство для деления на константу 2 @ -1 | 1987 |

|

SU1490675A1 |

| Устройство для деления на константу 2 @ - 1 | 1990 |

|

SU1714596A1 |

| Устройство для возведения в квадрат | 1988 |

|

SU1534458A2 |

Изобретение относится к вычислительной технике. Устройство позволяет выполнять деление чисел на константу (2М) в последовательном коде с заданной точностью. 2 ил.

| Устройство для деления | 1975 |

|

SU710040A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления на константу 2 @ -1 | 1987 |

|

SU1490675A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-06-15—Публикация

1990-04-17—Подача