сл ю

ON

IS

Изобретение относится к вычислительной технике и может быть использовано в арифметических блоках.

Известно устройство для деления, содержащее сумматор, регистр делимого, регистр (регистр делителя) и матрицу умножения.

Недостатком устройства является его сложность.

Известно устройство для деления на константу типа , выбранное в качестве прототипа и содержащее сумматор, регистр делимого, элемент НЕ, блок сложения с единицей, ключ, промежуточный регистр и элемент И, причем входы разрядов делимого устройства соединены с информационными входами соответствующих разрядов регистра делимого, синхровход которого является входом запуска устройства и обьединен с входом сброса промежуточного регистра, синхровход которого является тактовым входом устройства, выходы разрядов регистра делимого и промежуточного регистра соединены с входами соответствующих разрядов первого и второго слагаемых сумматора, выходы которого с 1-го по 1-й соединены с срответствующими информационными входами ключа и входами элемента И, выход которого подклю1 ен к управляющему входу блока сложения с единицей и входу элемента НЕ, выход которого соединенсуправляющим входом ключа, выходы разрядов сумматора с(+1)-го по (п+1}-й, где п-разрядность делимого, поступают на информационные входы блока сложения с единицей и информационные входы промежуточного регистра с 1-го по (п-1+1)-го их разряды соответственно, входы разрядов с (п-1+1)-го по второго слагаемого сумматора подключены к нулевой шине, выходы блока сложений.с единицей и ключа являются соответственно выходами частного и остатка результата, блок сложения с единицей состоит из п элементов И и (п+1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первые входы элементов И являются первыми информационными входами блока сложения с единицей, выход предыдущего элемента И соединен с вторым входом последуюа его элемента И, первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ являются соответствующими их номеру входами блока сложения с единицей, вторые входы соответствующих элементов И и ИСКЛЮЧАЮЩЕЕ ИЛИ объединены между собой, выход п-го элемента И соединен с вторым входом (п+1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. второй вход первого элемента И является управляющим входом блока сложения с единицей, ключ состоит из I элементов И, первые входы

которых являются информационными входами ключа, вторые входы объединены между собой и являются управляющим входом ключа, а выходы являются выходами ключа.

Недостатком этого устройства являются

ограниченные функциональные возможности, обусловленные невозможностью деления двоично-десятичных чисел на константу /-1.

0 Целью изобретения является расширение области применения устройства за счет выполнения деления двоично-десятичных чисел на константу .

Указанная цель достигается тем, что в

5 устройство для деления на константу , содержащее регистр, промежуточный регистр, сумматор, блок сложения с единицей, элемент И, элемент НЕ и ключ, причем синхровход промежуточного регистра является

0 тактовым входом устройства, вход запуска которого подключен ко входу промежуточного регистра и синхровходу регистра, информационные входы которого являются входами соответствующих разрядов делимого, а выходы соединены с входами соот ветствующих разрядов первого слагаемого сумматора, входы с (n-l -2ihro по п-й разрядов второго слагаемого которого подключены к нулевой шине, а входы с 1-го по{п+1-1)го

0 разрядов второго слагаемого соединены с соответствующим выходами промежуточного регистра, информационные входы которого объединены с соответствуюьщими информационными входами блока сложения с единицей, выходы которого являются выходами частного результата, а управляющий вход объединен с входом элемента НЕ и подключен к выходу элемента И, входы которого объединены с соответствующими

0 информационными входами ключа, управляющий вход которого соединен с выходом элемент Н€, а выходы являются выходами остатка результата, введен делитель на 2, причем входы делителя на 2 соединены с

5 соответствующими выходами сумматора, выходь частного подключены к соответствующим информационным входам промежуточного регистра, а выходы остатка соединены с соответствующими входами

0 элемента И

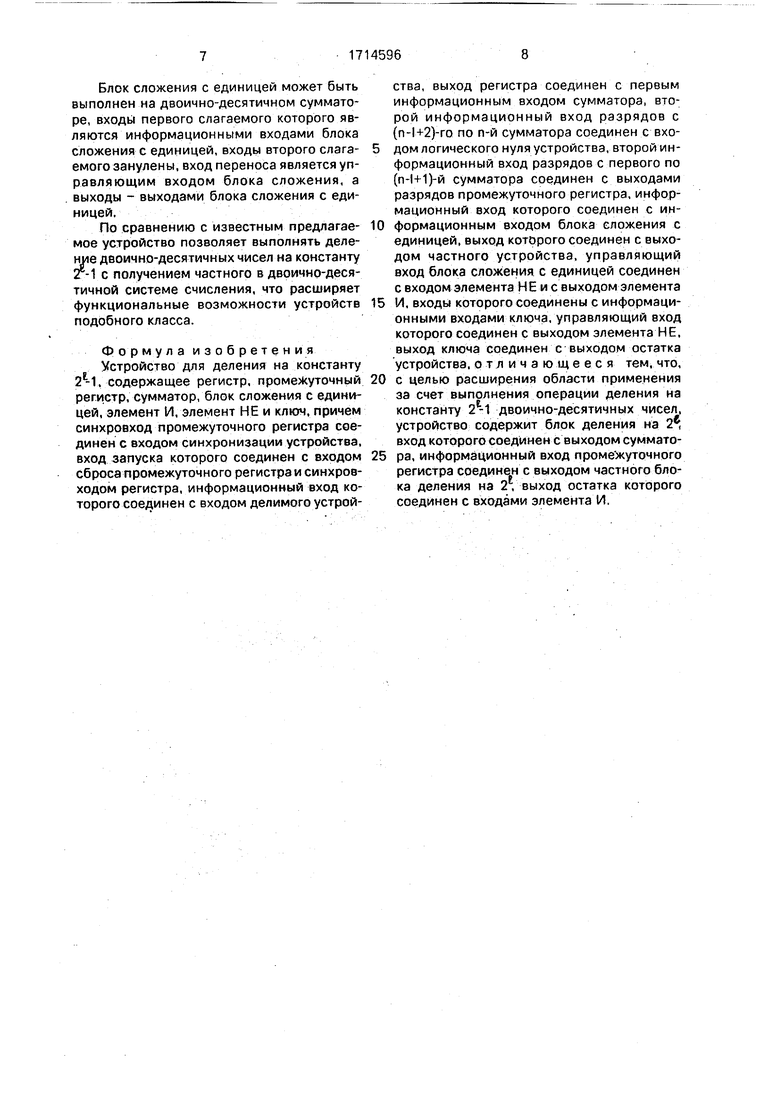

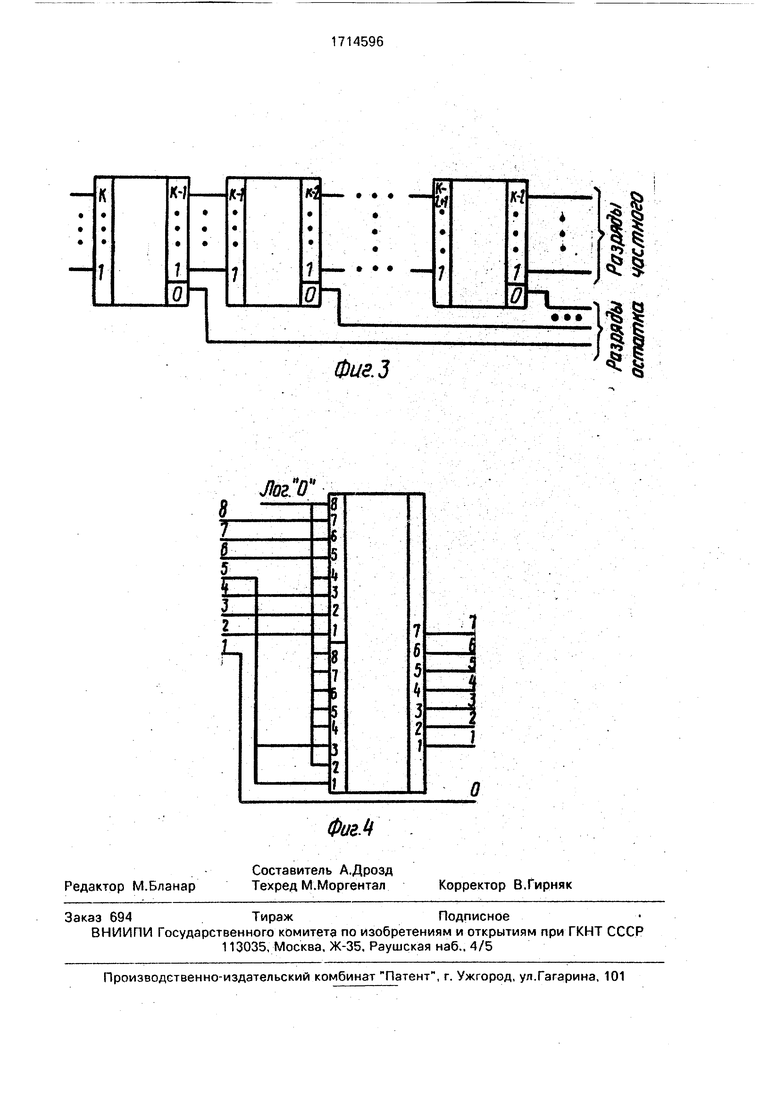

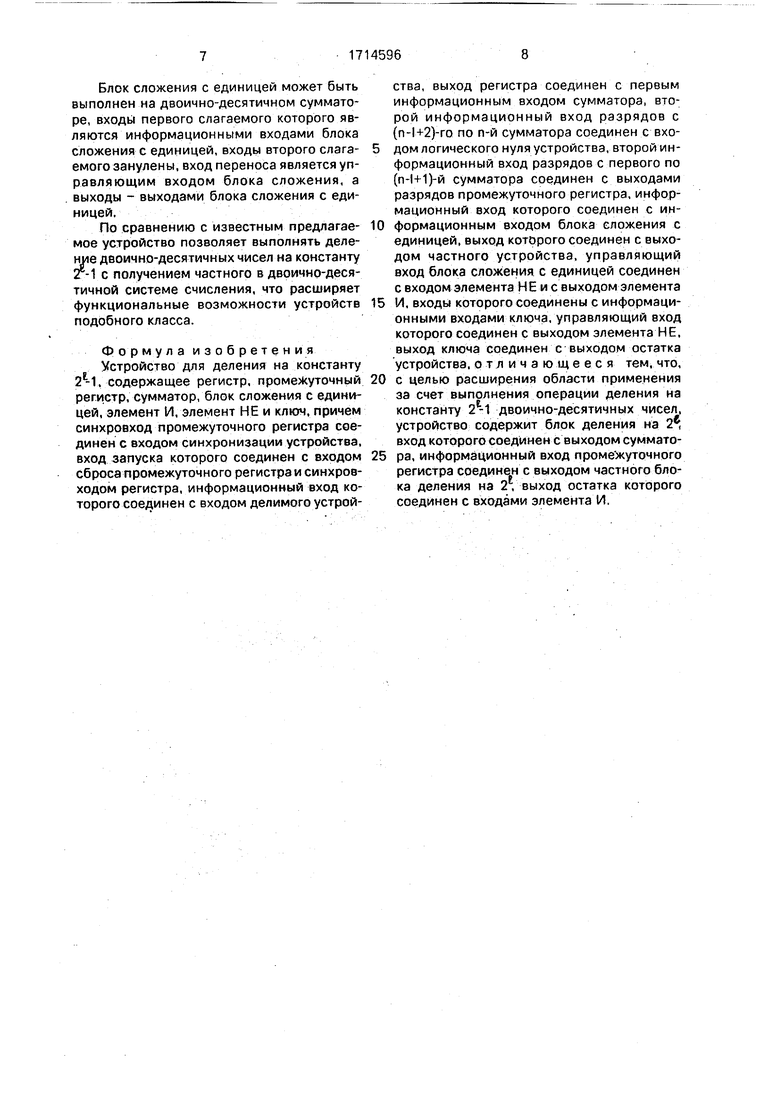

На фиг.1 показана структурная схема устройства; на фиг.2 - временные диаграммы, поясняющие работу устройства: на фиг;3 - делитель на 2 на фиг.4 - схема

5 делителя на 2 трехстрадного двоичного числа.

Устройство содержит регистр 1, промежуточный регистр 2, сумматор 3, делитель на 24, элемент И 5, элемент НЕ 6, ключ 7, блок 8 сложения с единицей, вход 9 синхронизации, вход 10 запуска, выходы 11 делимого, выходы 12 частного результата, выходы 13 остатка результата, причем синхровход 9 промежуточного регистра является тактовым входом устройства, а вход 10 сброса промежуточного регистра 2 обьединен с синхровходом 10 регистра 1 и является входом запуска устройства, входы разрядов с ()-й по п-й второго слагаемого сумматора 3 подключены к нулевой шине, входы 11 разрядов делимого устройства соединены с информационными входами соответствующих разрядов регистра делимого 1, выходы которого соединены с соответствующими входами первого слагаемого сумматора 3, (п-1+1) младших разрядов второго слагаемого которого подключены к соответствующим выходам регистра 2, информационные входы которого соединены с соответствующими входами блока еложения с единицей 8 и с соответствующими выходами частного делителя на 2 4, {п+1)е входы- которого соединены с соответствующими выходами сумматора 3, а выходы остатка соединены с соответствукэщими информационными входами ключа 7 и соответствующими входами элемента И 5, выход которого соединен с управляющим входом блока 8 сложения с единицей и входом элемента НЕ 6, выход которого соединен с управляющим рходом ключа 7, выходы последнего являются выходами 13 остатка результата, а выходы 12 блока 8 сложения с единицей являются выходами частного результата;Устройство работает следующим образом. На входы 11 поступает делимое - двоично -десятичное число, описанное через тетрады п двоичными разрядами. Это число записывается в регистр 1 по сигналу, поступающему на вход 10. Одновременно этот сигнал приходит на вход сброса триггера 2, устанавливая его в нулевое состояние. Получение искомого частного X можно описать уравнением А/() Х v-- Х (А + Х). Отсюда следует возможность вычисления частного посредством деления на конетанту 2 и при этом имеет место погрешность, которая определяется значением X и выражается через делимое А. Погрешность учитывается на сумматоре 3, являющимся двоично-десятичным сумматором, путем сложения делимого А с полученной на делителе на 2 4 величиной А/2 и синхронизации операции сложения с использованием регистра 2. Для этого число А с выходов регистра 1 подается на входы первого слагаемого сумматора 3. Регистр 2осуществляет прием информации по сигналам, поступающим на его синхровход через вход 9. На старшие входы второй группы входов сумматора 3 с (п-1+2) по п-й разряды поступает уровень логического О. Код суммы с выходов сумматора 3 поступает на входы делителя на 2 4, с выхода которого снимается (п-И-1) двоичных разрядов двоично-Десятичного кода XI частного и I разрядов двоичного числа кода Х2 остатка. Код Х1 частного поступает на информационные входы регистра 2 и далее с выходов его разрядов на входы второго слагаемого сумматора 3с 1-го по (п-1+1 )-й разряды. Код Х2 можно рассматривать как остаток от деления на константу 2-1 при целочисленном делении или трактовать как код периода периодической дроби, причем возможен случай, когда все разряды кода Х2 принимают еди ничные значения, т.е. остаток от деления равен делителю или период дроби равен единице, что требует обнуления кода Х2 и увеличения целой части XI частного X на единицу младшего разряда. Указанный случай идентифицируется с использованием элемента И 5, на входы которого поступают значения разрядов кода Х2. Если не все разряды кода Х2 принимают единичное значение, то на выходе элемента 1/1 5 устанавливается нулевое значение, а на выходе следующего за элементом И 5 инвертора 6 формируется единичное значение. Сигнал с выхода элемента И 5 поступает на управляющий вход блока 8 сложения с единицей, а его инверсное значение с выхода элемента НЕ 6- на управляющий вход ключа 7, при этом нулевое значение сигнала обеспечивает передачу кода частного и кода остатка с информационных входов блока 8 сложения с единицей и ключа 7 на их выходы без изменения, а единичное значение сигнала увеличивает двоично-десятичный код частного на единицу и обнуляет двоичный код остатка. Полученные коды являются результатом целочисленного .деления и поступают соответственно на выходы 12 и t3 устройства. Регистры 1 и 2 могут быть выполнены на МС К155ТМ8, двоично-десятичный сумматорЗ можетбытьвыполнен на МСК155ИМ5. Делитель на 1 показан (фиг.З) в виде последовательного соединения делителей на 2. Схема делителя на 2 трехтетрадного двоичного числа (фиг.4) выполняется на МС К155ИШ.

Блок сложения с единицей может быть выполнен на двоично-десятичном сумматоре, входы первого слагаемого которого являются информационными входами блока сложения с единицей, входы второго слагаемого занулены, вход переноса является управляющим входом блока сложения, а выходы - выходами блока сложения с единицей.

По сравнению с известным предлагаемое устройство позволяет выполнять деление двоично-десятичных чисел на константу У-1 с получением частного в двоично-десятичной системе счисления, что расширяет функциональные возможности устройств подобного класса.

Формула изобретения Устройство для деления на константу . содержащее регистр, промежуточный регистр, сумматор, блок сложения с единицей, элемент И, элемент НЕ и ключ, причем синхровход промежуточного регистра соединен с входом синхронизации устройства, вход запуска которого соединен с входом сброса промежуточно го регистра и синхровходом регистра, информационный вход которого с входом делимого устройства, выход регистра соединен с первым информационным входом сумматора, второй информационный вход разрядов с (п-1+2)-го по п-й сумматора соединен с входом логического нуля устройства, второй информационный вход разрядов с первого по (п-1+1)-й сумматора соединен с выходами разрядов промежуточного регистра, информационный вход которого соединен с информационным входом блока сложения с единицей, выход кот эрого соединен с выходом частного устройства, управляющий вход блока сложения с единицей соединен с входом элемента НЕ и с выходом элемента

И, входы которого соединены с информационными входами ключа, управляющий вход которого соединен с выходом элемента НЕ, выход ключа соединен с выходом остатка устройства, о т л и ч а ю щ е е с я тем. что,

с целью расширения области применения за счет выполнения операции деления на константу двоично-десятичных чисел, устройство содержит блок деления на 2. вход которого соединен с выходом сумматора, информационный вход проме куточного регистра соединен с выходом частного блока деления на 2, выход остатка которого соединен с входами элемента И.

5 f

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел на константу типа 2 @ + 1 | 1990 |

|

SU1791813A1 |

| Устройство для деления | 1989 |

|

SU1658149A1 |

| Устройство для деления чисел на константу 2 @ + 1 | 1990 |

|

SU1730624A1 |

| Устройство для деления на константу 2 @ -1 | 1987 |

|

SU1490675A1 |

| Устройство для деления чисел на константу 2 @ + 1 | 1990 |

|

SU1746379A1 |

| Устройство для деления чисел | 1989 |

|

SU1711151A1 |

| Устройство для деления чисел на константу 2 @ - 1 | 1990 |

|

SU1714594A1 |

| Устройство для деления чисел на константу 2 @ - 1 | 1990 |

|

SU1741130A1 |

| Устройство для преобразования двоично-десятичных чисел в двоичные | 1988 |

|

SU1557680A2 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

Изобретение относится к вычислитель- ной технике и может быть использовано варифметических блоках. Цель изобретения - расширение области применения замечет выполнения операции деления на-константу 2^-1 двоично-десятичных чисел. Устройство содержит регистр 1, принимающий дели-^ мое, сумматор 3. выполняющий сложение делимого с результ^атом его деления на 2f который вычисляется в блоке деления 4 и задерживается на промежуточном регистре 2. Элемент И 5 идентифицирует остаток, равный 2^-1, при котором блок 8 сложения с единицей увеличивает частное, снимаемое с выходов блока 4 на единицу, а ключ 7, управляемый черезинвертор 6, обнуляет остаток. 4 ил. •: У •^

g

CM «O «raC.OQ

o. J ц

- «i3

S «S«i « «VJ

5

b

Ш

| Устройство для деления | 1975 |

|

SU710040A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-02-23—Публикация

1990-07-25—Подача