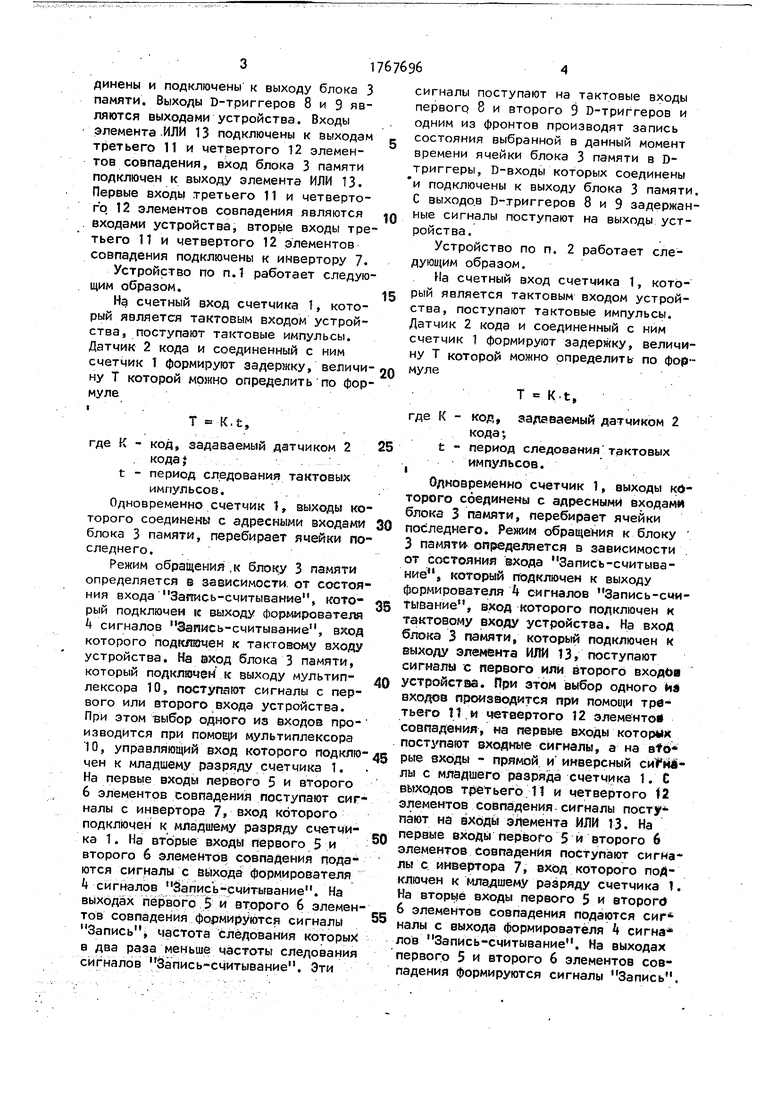

динены и подключены к выходу блока 3 памяти. Выходы D-триггеров 8 и 9 являются выходами устройства. Входы элемента ИЛИ 13 подключены к выходам третьего 11 и четвертого 12 элементов совпадения, вход блока 3 памяти подключен к выходу элемента ИЛИ 13. Первые входы третьего 11 и четвертого 12 элементов совпадения являются входами устройства, вторые входы третьего 11 и четвертого 12 элементов совпадения подключены к инвертору 7.

Устройство по п.1 работает следующим образом.

На счетный вход счетчика 1, который является тактовым входом устройства, поступают тактовые импульсы. Датчик 2 кода и соединенный с ним счетчик 1 формируют задержку, величину Т которой можно определить по формуле

Т « K.t,

где К - код, задаваемый датчиком 2

кода t - период следования тактовых

импульсов.

Одновременно счетчик 1, выходы которого соединены с адресными входами блока 3 памяти, перебирает ячейки последнего.

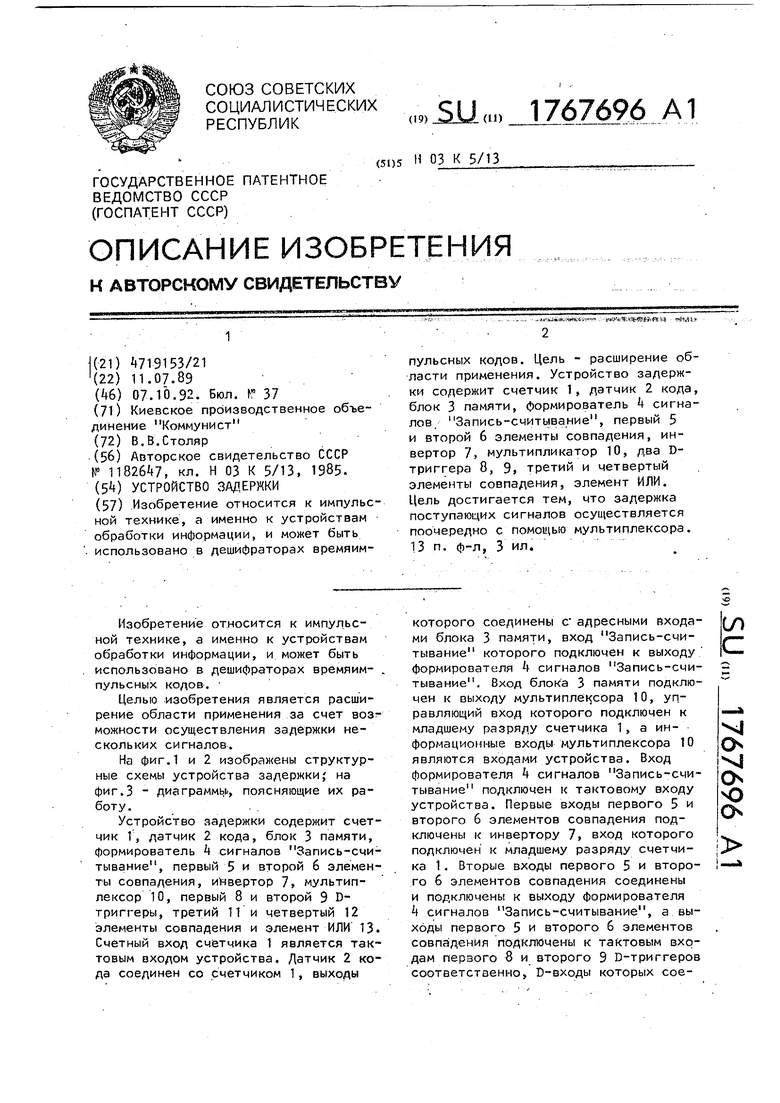

Режим обращения ,к блоку 3 памяти определяется в зависимости от состояния входа Запись-считывание1, который подключен к выходу формирователя I сигналов Запись-считывание, вход которого подключен к тактовому входу устройства. На аход блока 3 памяти, который подключен к выходу мультиплексора 10, поступают сигналы с первого или второго входа устройства. При этом выбор одного из входов производится при помощи мультиплексора 10, управляющий вход которого подключен к младшему разряду счетчика 1. На первые входы первого 5 и второго 6 элементов совпадения поступают сигналы с инвертора 7, вход которого подключен к младшему разряду счетчика 1. На вторые входы первого 5 и второго 6 элементов совпадения подаются сигналы с выхода формирователя сигналов Запись-считывание. На выходах первого 5 и второго 6 элементов совпадения формируются сигналы Запись, частота следования которых в два раза меньше частоты следования сигналов Запись-считывание. Эти

сигналы поступают на тактовые входы первого 8 и второго 9 D-триггеров и одним из фронтов производят запись

состояния выбранной в данный момент времени ячейки блока 3 памяти в D- триггеры, D-входы которых соединены и подключены к выходу блока 3 памяти. С выходов D-триггеров 8 и 9 задержанные сигналы поступают на выходы устройства.

Устройство по п. 2 работает следующим образом.

На счетный вход счетчика 1, кото5 рый является тактовым входом устройства, поступают тактовые импульсы. Датчик 2 кода и соединенный с ним счетчик 1 формируют задержку, величину Т которой можно определить по фор™

0 муле

Т « K.t,

где К - код, задаваемый датчиком 2

кода;

5 fc - период следования тактовых импульсов.

Одновременно счетчик 1, выходы которого соединены с адресными входами блока 3 памяти, перебирает ячейки

0 последнего. Режим обращения к блоку 3 памят определяется в зависимости от состояния входа Запись-считывание 1, который подключен к выходу формирователя 4 сигналов Запись-счи5 тьшание, вход которого подключен к тактовому входу устройства. На вход блока 3 памяти, который подключен к выходу элемента ИЛИ 13, поступают сигналы с первого или второго входов

0 устройства. При этом выбор одного йа входов производится при помощи третьего It и четвертого 12 элементе совпадения, на первые входы которых поступают входные сигналы, а на efo

5 рые входы - прямой и инверсный сиРна- лы с младшего разряда счетчика 1. С выходов третьего 11 и четвертого J2 элементов совпадения сигналы посту пают на входы элемента ИЛИ 13. На

.Q первые входы первого 5 и второго 6 элементов совпадения поступают сигналы с инвертора 7, вход которого подключен к младшему разряду счетчика 1. На вторые входы первого 5 и второгд 6 элементов совпадения подаются сигь

5 налы с выхода формирователя 4 сигна лов Запись-считывание. На выходах первого 5 и второго 6 элементов совпадения формируются сигналы Запись.

частота следования которых в два ра-Л за меньше частоты следования сигналов Запись-считывание. Эти сигналы поступают на тактовые входы первого , 8 и второго 9 D-триггеров и одним из фронтов производят запись состояния выбранной в данный момент времени ячейки блока 3 памяти в D-триггеры, D-входы которых соединены и подключены к выходу блока 3 памяти. С выходов D-триггеров 8 и 9 задержанные сигналы поступают на выходы устройства.

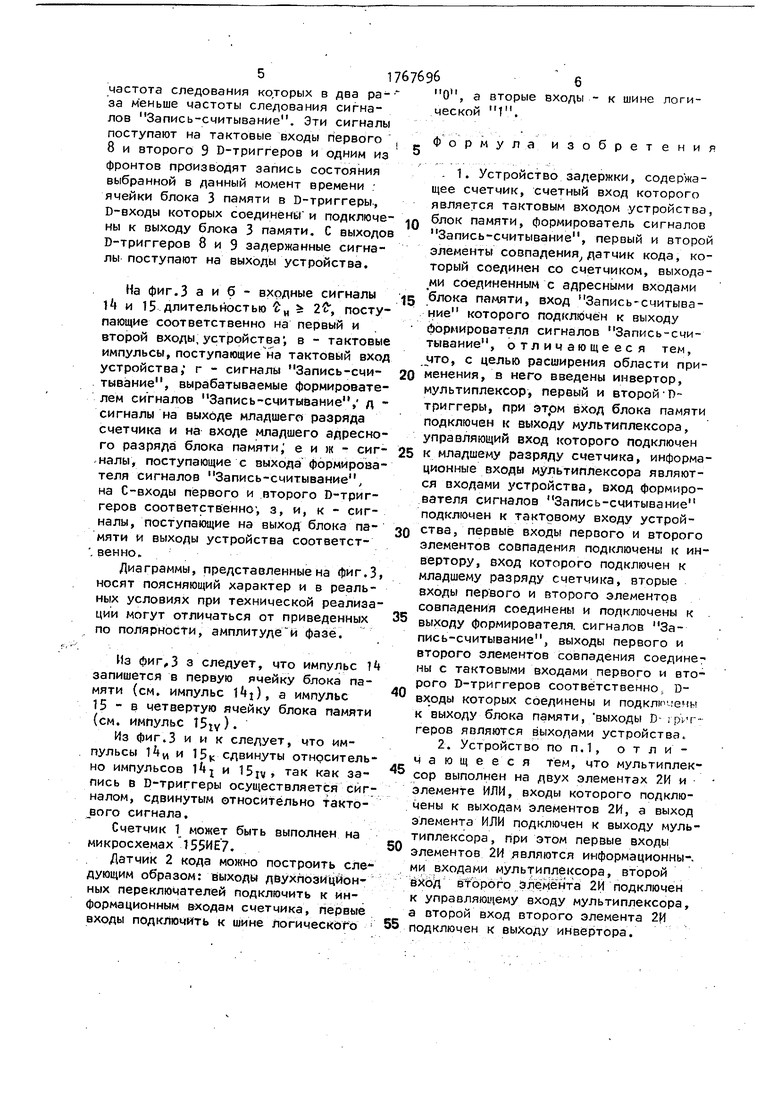

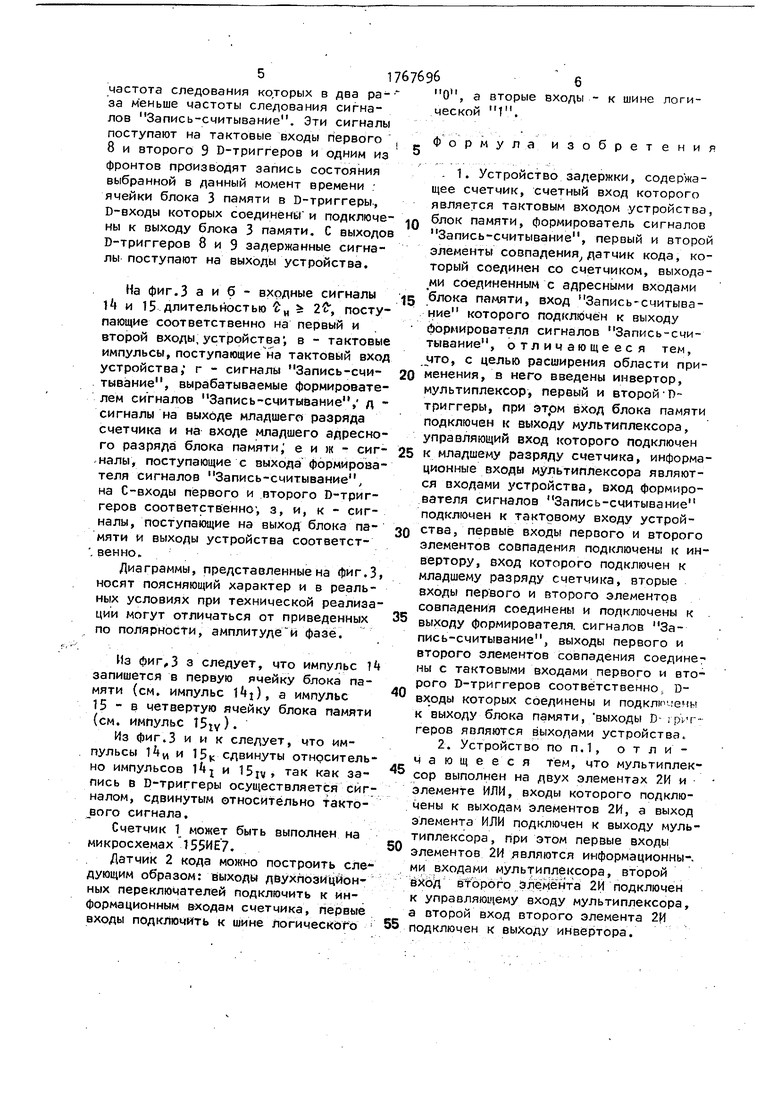

На фиг.З а и б - входные сигналы И и 15 длительностью Ј„ 2, поступающие соответственно на первый и второй входы, устройства , в - тактовые импульсы, поступающие на тактовый вход устройства; г - сигналы Запись-считывание, вырабатываемые формирователем сигналов Запись-считывание, д - сигналы на выходе младшего разряда счетчика и на входе младшего адресного разряда блока памяти, е и ж - сигналы, поступающие с выхода формирователя сигналов Запись-считывание, на С-входы первого и второго D-триггеров соответственно , з, и, к - сигналы, поступающие на выход блока памяти и выходы устройства соответст- вен но.

Диаграммы, представленные на фиг.З, носят поясняющий характер и в реальных условиях при технической реализации могут отличаться от приведенных по полярности, амплитуде и фазе.

Из фиг,3 з следует, что импульс Ik запишется в первую ячейку блока памяти (см. импульс ), а импульс 15 - в четвертую ячейку блока памяти (см. импульс Т5iv)

Из фиг.З и и к следует, что импульсы И ц и 15ц сдвинуты относительно импульсов и 15tv так как заись в D-триггеры осуществляется сигналом, сдвинутым относительно такто- вого сигнала.

Счетчик 1 может быть выполнен на икросхемах 755ИЕ7.

Датчик 2 кода можно построить слеующим образом: выходы двухпозицион- ых переключателей подключить к инормационным входам счетчика, первые входы подключить к шине логического

7696

О, а вторые ческой 1.

6

входы к шине логи10

5

0

5

Формула изобретения

. 1. Устройство задержки, содержащее счетчик, счетный вход которого является тактовым входом устройства, блок памяти, формирователь сигналов Запись-считывание, первый и второй элементы совпадения, датчик кода, который соединен со счетчиком, выходами соединенным с адресными входами блока памяти, вход Запись-считывание которого подключен к выходу Формирователя сигналов Запись-считывание, отличающееся тем, ..что, с целью расширения области применения, в него введены инвертор, мультиплексор, первый и второй 0- триггеры, при этрм вход блока памяти подключен к выходу мультиплексора, управляющий вход которого подключен к младшему разряду счетчика, информационные входы мультиплексора являются входами устройства, вход формирователя сигналов Запись-считывание подключен к тактовому входу устройства, первые входы первого и второго элементов совпадения подключены к инвертору, вход которого подключен к младшему разряду счетчика, вторые входы первого и второго элементов совпадения соединены и подключены к выходу формирователя, сигналов Запись-считывание, выходы первого и второго элементов совпадения соединены с тактовыми входами первого и второго D-триггеров соответственно D- входы которых соединены и подключены к выходу блока памяти, выходы D . риг- геров являются выходами устройства, 2. Устройство по п.1, отличающееся тем, что мультиплексор выполнен на двух элементах 2И и элементе ИЛИ, входы которого подключены к выходам элементов 2И, а выход элемента ИЛИ подключен к выходу мультиплексора , при этом первые входы элементов 2И являются информационны-, ми входами мультиплексора, второй вход второго элемента 2И подключен к управляющему входу мультиплексора, а второй вход второго элемента 2И подключен к выходу инвертора.

0

5

0

5

5

№2

JtuWX.

- t

.

Ettunj JiEL,

JT f J I iv E I JT )

№2

- t

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство задержки | 1989 |

|

SU1698966A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Запоминающее устройство | 1977 |

|

SU691925A1 |

| Устройство для преобразования последовательного кода | 1988 |

|

SU1640827A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| УНИВЕРСАЛЬНОЕ УСТРОЙСТВО КОДИРОВАНИЯ СИГНАЛОВ | 1993 |

|

RU2037270C1 |

LT

u

LJ

%{ 1 /vgl

I /3t/

. : -. .

и

- 6

IT,

.

I I .t-t-T

Авторы

Даты

1992-10-07—Публикация

1989-07-11—Подача