Изобретение относится к электротехнике, в частности к преобразовательной технике, и может быть использовано при построении цифровых систем управления преобразователями в электроприводе.

Целью изобретения является упрощение устройства и улучшение динамических характеристик.

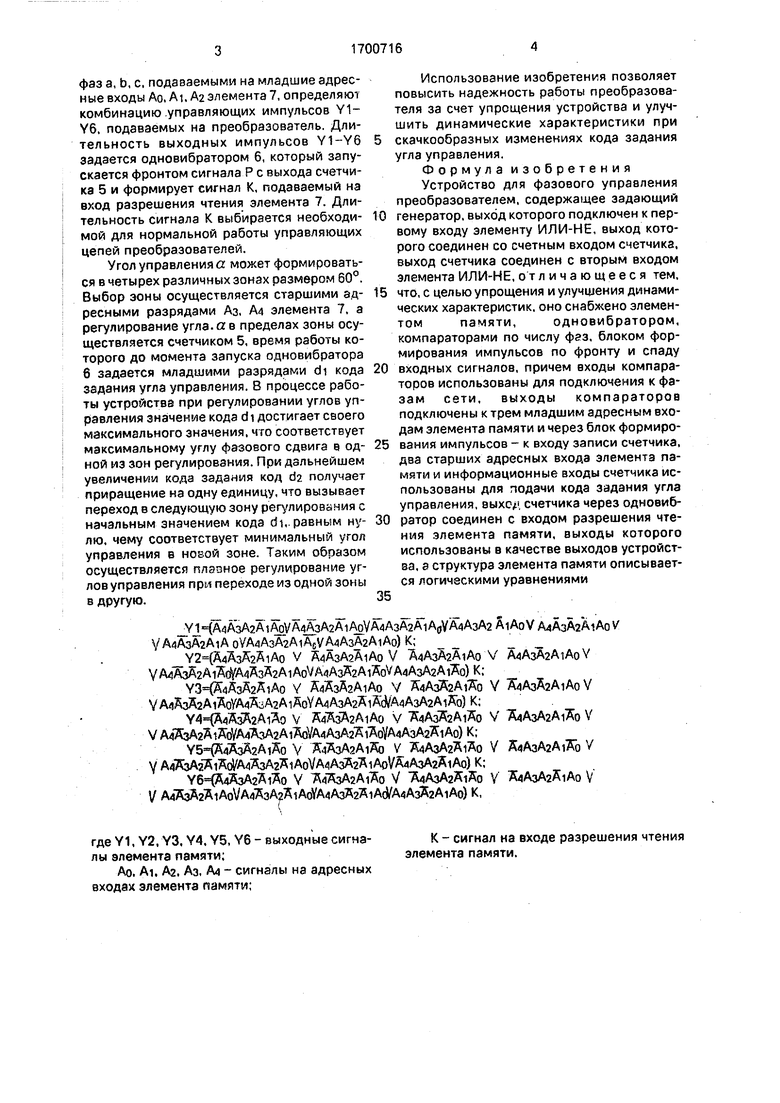

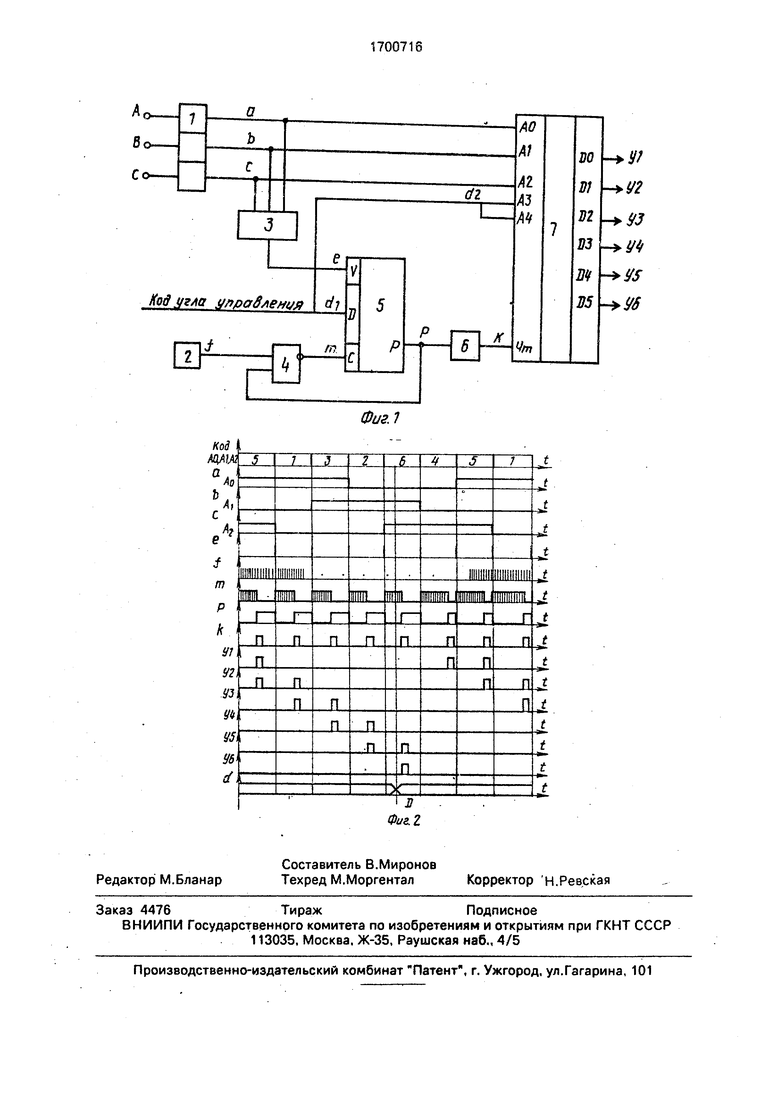

На фиг. 1 представлена схема устройства; на фиг. 2 -диаграммы, иллюстрирующие его работу.

Устройство содержит компараторы 1, задающий генератор 2. блок 3 формирования импульсов по фронту и спаду входных сигналов, элемент ИЛИ-НЕ 4, счетчик 5, од- новибратор 6, элемент 7 памяти.

Устройство работает следующим образом.

Из фазных напряжений сети А, В, С компараторы 1 формируют последовательность кодов фаз а, Ь, с (фиг. 2), которая подается на входы блока 3. На выходе последнего формируется сигнал е в моменты изменения кода фаз а, Ь. с. Сигнал е подается на вход

записи счетчика 5. Импульсы частотой f генератора 2 через элемент 4 подаются на счетный вход счетчика 5, если на второй. вход элемента 4 подается низкий уровень сигнала с выхода счетчика 5. В начале цикла работы устройства по сигналу е с выхода блока 3 младшие разряды кода задания угла управления di записываются в счетчик 5, на выходе которого при этом устанавливается логический О, разрешая прохождения импульсов генератора 2 через элемент 4 на счетный вход счетчика 5 до тех пор, пока последний не заполнится после чего его выходной сигнал устанавливается в состояние логической 1 и запрещает дальнейшее прохождение импульсов на счетный вход счетчика 5.

Длительность работы счетчика 5 при неизменной частоте f задающего генератора 2 определяется значением кода младших разрядов задания угла управления di. Старшие разряды d2 кода задания угла управления подаются на старшие адресные входы Аз. А элемента 7, которые совместно с кодами

V|

О,

фаз а, Ь, с, подаваемыми на младшие адрес- ные входы АО, AT, A2 элемента 7, определяют комбинацию управляющих импульсов Y1- Y6, подаваемых на преобразователь. Длительность выходных импульсов Y1-Y6 задается одновибратором 6, который запускается фронтом сигнала Р с выхода счетчика 5 и формирует сигнал К, подаваемый на вход разрешения чтения элемента 7. Длительность сигнала К выбирается необходи- мой для нормальной работы управляющих цепей преобразователей.

Угол управления а может формироваться в четырех различных зонах размером 60°. Выбор зоны осуществляется старшими ад- ресными разрядами Аз, Аз элемента 7, а регулирование угла, а в пределах зоны осуществляется счетчиком 5, время работы которого до момента запуска одновибратора 6 задается младшими разрядами сН кода задания угла управления. В процессе работы устройства при регулировании углов управления значение кода di достигает своего максимального значения, что соответствует максимальному углу фазового сдвига g од- ной из зон регулирования. При дальнейшем увеличении кода задания код da получает приращение на одну единицу, что вызывает переход в следующую зону регулирования с начальным значением кода di..равным ну- лю, чему соответствует минимальный угол управления в новой зоне. Таким образом осуществляется плавное регулирование углов управления при переходе из одной зоны в другую.

Использование изобретения позволяет повысить надежность работы преобразователя за счет упрощения устройства и улучшить динамические характеристики при скачкообразных изменениях кода задания угла управления.

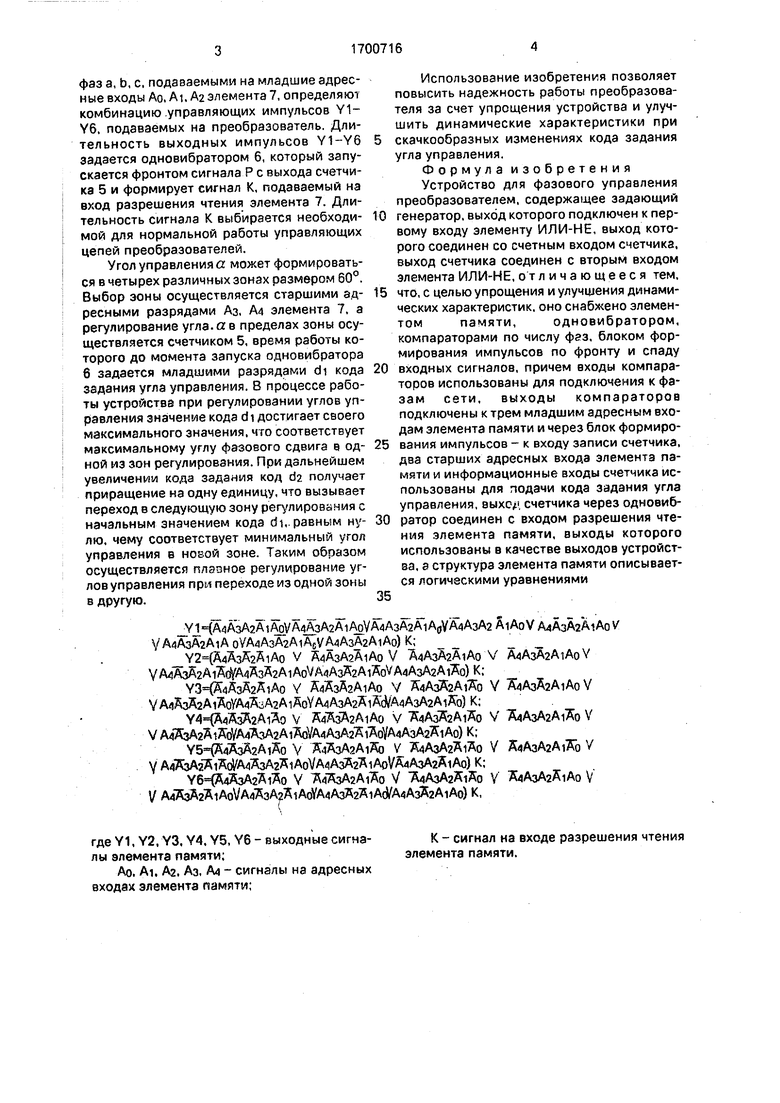

Формула изобретения Устройство для фазового управления преобразователем, содержащее задающий генератор, выход которого подключен к первому входу элементу ИЛИ-НЕ, выход которого соединен со счетным входом счетчика, выход счетчика соединен с вторым входом элемента ИЛИ-НЕ, отличающееся тем, что, с целью упрощения и улучшения динамических характеристик, оно снабжено элементом памяти, одновибратором, компараторами по числу фаз, блоком формирования импульсов по фронту и спаду входных сигналов, причем входы компараторов использованы для подключения к фазам сети, выходы компараторов подключены к трем младшим адресным входам элемента памяти и через блок формирования импульсов - к входу записи счетчика, два старших адресных входа элемента памяти и информационные входы счетчика использованы для подачи кода задания угла управления, выход счетчика через одновиб- ратор соединен с входом разрешения чтения элемента памяти, выходы которого использованы в качестве выходов устройства, а структура элемента памяти описывается логическими уравнениями

| название | год | авторы | номер документа |

|---|---|---|---|

| Вероятностный преобразователь аналог-код | 1986 |

|

SU1363461A1 |

| Сигнализатор совпадения фаз | 1990 |

|

SU1824595A1 |

| УСТРОЙСТВО ДЛЯ ОРТОГОНАЛЬНОГО ПРЕОБРАЗОВАНИЯ ЦИФРОВЫХ СИГНАЛОВ ПО УОЛШУ-АДАМАРУ | 1989 |

|

RU2012047C1 |

| Цифровой фильтр | 1988 |

|

SU1566469A1 |

| Устройство для управления инвертором | 1987 |

|

SU1617584A1 |

| Устройство для ввода информации | 1988 |

|

SU1580340A1 |

| Устройство для цифровой обработки сигналов | 1988 |

|

SU1575203A1 |

| Статистический анализатор выбросов и провалов напряжения | 1990 |

|

SU1837325A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Корреляционный измеритель фазовых соотношений узкополосных случайных процессов | 1990 |

|

SU1714616A1 |

Изобретение относится к электротехнике и может быть использовано при построении цифровых систем управления электроприводами. Цель изобретения - упрощение устройства и улучшение его динамических характеристик. Устройство содержит нуль- орган, задающий генератор, блок формирования импульсов по фронту и спаду входных сигналов, элемент ИЛИ-НЕ, счетчик, имеющий информационные входы, вход записи и счетный вход, выход счетчика через одно- вибратор управляет элементом памяти, который формирует выходные сигналы в зависимости от кода задания угла управления и сигналов на выходах компараторов. 2 ил.

YJ.-(A4A3A2Ai AoVA4A3A2AiAgVA4A3A2Ai А„УА4АзА2 AiAo V А АзАг/Ч АО V YAaA3A2AiA oVA4A3A2AiAcVA4A3A2AiAo) К;

Y2(A 4U3A 2AiAo V A AVVzAiAo V A AaAaA Ao V A/iAaAaAiAoV V A«AaAzАОДА ДзА2A1 AoVA«АзА2A1 AoV АлАзА2A ) K;

Y3(A 4A3A2AiAo Y A4AaA2AiAo V V V V А УА4АоА2А1 AoY A4A3A2AiA oVA/)A3A2AiAo) К;

Y4(A4A3A2AiAo V V TfyAaAbAiAo V 7WV3A2AiA o V V A4A A2AiAcf/A4A3A2AiAoVA4A3A2AiAoVA4A3A2Ai АО) К;

Y5(A4A3A2AiAo V A AaAaAiAo V A 4A3A2AiAo V AuAsAaAiAo V Y A4A3A2 AiAoVA4A3A2AiAoVA4A3A2AiAoVA4A3A2AiAo) K;

Y6(A4A3A2AiAo V 4A3A2AiAo V 7UA3A2AiAo V А 4АзА2А 1Ао V V A47 2AiAoVA4A 2AiAoYA4A3A2 iAoYA4A3A 2AiAo) K,

где Y1. Y2, Y3. Y4. Y5, Y6 - выходные сигналы элемента памяти;

АО, At, А2, Аз. Аз - сигналы на адресных входах элемента памяти:

К - сигнал на входе разрешения чтения элемента памяти.

| Устройство для фазового управления преобразователем | 1982 |

|

SU1083323A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1991-12-23—Публикация

1988-05-17—Подача