. (St) УСТРОЙСТВО для КОНТРОЛЯ ОПЕРАТИВНОЙ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления режимамиОбМЕНА РЕзЕРВиРОВАННОй СиСТЕМы | 1979 |

|

SU849216A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Устройство для управления оперативной памятью | 1985 |

|

SU1291992A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1010660A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Микропрограммное устройство управления | 1981 |

|

SU987623A1 |

| Устройство для отладки программно-аппаратных блоков | 1983 |

|

SU1242965A1 |

| Устройство для контроля полупроводниковой памяти | 1982 |

|

SU1051585A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

1

Изобретение относится к запоми.нающим устройствам, в частности к устройствам для контроля оперативных запоминающих устройств (ОЗУ) с произвольной выборкой.

Известно устройство для контроля оперативного накопителя информации, содержащее схему пуска, выход которой подключен к регистру числа, счетчику адресов и счетчику циклов схему сравнения, выход которой соединен с блоком регистрации, подключенного к схеме останова, элемент И, коммутатор разрядов, вход которого подключен к входной шине устройства, а выход - к одному входу элемента И, дешифратор цикла, вход которого подключен к первому выходу счетчика циклов, а выход - к другому входу элемента И, дополнительные счетчики, входы которых подключены к второму выходу счетчика циклов и выходу элемента И соответственно, а выходы к входам схемы сравнения l .

Недостатком этого устройства являются большие аппаратурные затраты.

Наиболее близким техническим решением к предлагаемому является устройство для контроля памяти, содержащее блок памяти, блок управления, блок сравнения, формирователь кодов, причем вход блока управления соединен с выходом блока сравнения, одна

10 группа входов которого соединена с выходными шинами блока памяти, а вто рая группа - с выходами формирователя кодов, входы которого соединены с адресными шинами блока памяти,

5 счетчик числа обращений, счетчик математических ожиданий, генератор случайных чисел и сумматор, причем вход счетчика числа обращений соединен с выходом блока управления, а выход - с

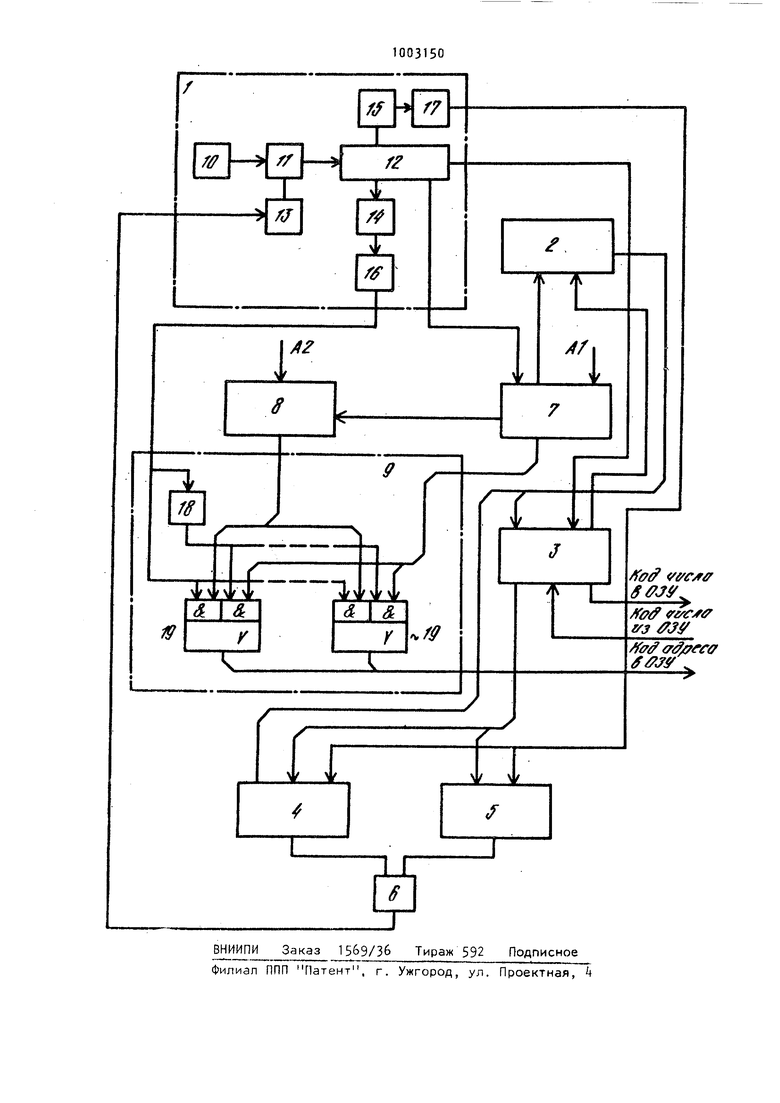

20 входом счетчика математических ожиданий , выходы которого и выходы генераторов случайных чисел подключены к соответствующим входам сумматора, 3 виходы сумматорсЧ соединены с адресными шинами Плока памяти 23. ИедостотK(jH этого устройства является го, что контролируется или только одно последовательное направ ление обхода адресов, или последова тельность адресов, полученная случа ным образом, а также то, что производится сравнение или только статического распределения считанной информации или сравнение динамического распределения информации сложением по модулю два. Это снижает надежность устройства. Цель изобретения - повышение надежности устройства. Поставленная цель достигается те что в устройство для контроля операти ной памяти, содержащее блок управле ния, первый выход которого соединен входом первого счетчика адреса, второй выход - с первым входом регистра числа, второй вход и первый выход ко торого подключены соответственно к . выходу и первому входу формирователя информационных сигналов, второй вход которого соединен с первым выходом первого счетчика адреса, выход - с первым входом первой схемы сравнения второй вход которой соединен с треть им выходом блока управления, а третий вход - с вторым выходом регистра числа, введены второй счетчик адреса вход которого соединен с вторым выходом первого счетчика адреса, формирователь адресных сигналов, первый вход которого соединен с четвертым выходом блока управления, второй вход подключен к третьему выходу пер вого сметчика адреса, третий вход к выходу второго счетчика адреса, а выход является одним из выходов устройства, вторая схема сравнения, первый вход которой соединен с третьим выходом блока управления, а вто рой вход - с вторым выходом регистра числа, и элемент ИЛИ, входы которого подключены к выходам схем сравМ1:ния, а выход соединен с входом бло ка управления. Формирователь адресных сигналов содержит элемент НЕ и элементы 2 И-ИЛИ-НЕ, первые входы которых подключены к выходу элемента НЕ, вторые входы объединены с входом элемента НЕ и являются первым входом формирователя, третьи и четвертые входы являются соответственно вторым и третьим входами форми504рователя, выходом которого являются выходы элементов 2И-ИЛИ-НЕ. На чертеже изображена структурная схема предлагаемого устройства. Устройство для контроля оперативной памяти содержит блок 1 управления, формирователь 2 информационных сигналов, регистр 3 мисла, первую и вторую 5 схемы сравнения, элемент ИЛИ 6, первый 7 и второй 8 счетчики адреса и формирователь 9 адресных сигналов. Блок 1 управления содержит генератор 10 импульсов, элемент И 11, элемент 12 задержки, первый триггер 13) первый 1 и второй 15 переключатели, второй 16 и третий 17 триггеры. Формирователь 9 адресных сигналов содержит элемент НЕ 18 и элементы 2И-ИЛИ-НЕ 19. Устройство для контроля оперативных запоминающих устройств .работает следующим образом. Работа устройства начинается с начальных установок. S блоке 1 с помощью переключателя 15 и триггера 17 устанавливается начальный режим проверки ОЗУ (запись или считывание) а с помощью переключателя И и триггера 16 устанавливается режим переадресации последовательный прямо1 или реверсивнь1Й галоп, обращение к одной или произвольной паре ячеен. На счетчике адреса 7 формиируется начальный адрес проверяемой ячейки памяти, который поступает на вход формирователя 9. 8 формирователе 2 формируется код числа для записи в ОЗУ. В этот начальный момент работы устройства сигналы с генератора 10 импульсов не проходят через элемент И 11 на элемент 12 задержки, так как триггер 13 находится в нулевом состоянии. После начальных установок триггер 13 переводится в единичное состояние-. На вход элемента И 11 с триггера 13 подается разрешающий потенциал и сигналы с генератора 10 импульсов через элемент И 11 поступают на элемент 12 задержки. Здесь они- формируются, задерживаются на необходимое время и поступают на формирователь 9, разрешая выдачу адреса в ОЗУ, на схемы и S сравнения подготавливая одну из них к сравнению считанного из ОЗУ и записанного в ОЗУ чисел, регистр 3 мисла, записывая на него сформулированный на формирователе 2 код fe режиме За5 . 10 пись и выдавая его в ОЗУ, или принимая считанное из ОЗУ число (в режиме Считывание), первый счетчик 7 адреса, устанавливая новый адрес ОЗУ. В режиме Считывание при статическом распределении .информации считанное из ОЗУ слово поразрядно сравг нивается на схеме t сравнения с кодом числа, сформулированным на формирователе 2. При динамическом распределении информации считанное из ОЗУ слово контролируется на схеме 5 сравнения методом двухкратного поразрядного сравнения. Результат несравнения через элемент ИЛИ 6 подается со схем и 5 сравнения в блок 1 на триггер 13, который перебрасывается в нулевое состояние, происходит останов ра боты устройства. Для приближения условий проверки к реальным условиям работы ОЗУ применен режим переадреса ции Галоп. В этом режиме переадресации производится занесение начального адреса проверямого массива на счетчик 7 адреса. Счетчик 8 адреса в этом режиме работает как старшие разряды первого счетчика 7 адреса. В дача адреса в проверяемое ОЗУ производится поочередно, то с первого 7, то со второго 8 счетчиков адреса. Уп равляет выдачей адресов триггер 1б блока 1. Управляющий потенциал с Триггера 16 поступает непосредственно или через элемент НЕ 18 на элемен ты 2И-ИЛИ-НЕ 19 формирователя 9 и pa решает выдачу адреса со счетчиков 7 и 8 адреса соответственно поочередно. В режиме переадресации Галоп происходит перебор всевозможных комбинаций адресов. Для организации мно гократной выборки последовательно пр извольной пары ячеек ОЗУ адрес первой произвольной ячейки ОЗУ заносится на счетчик 7 адреса. Адрес второй произвольной ячейки - на счетчик 8 адреса. Производится выборка адресоп попеременно, то с первого 7, то со второго 8 счетчиков, также как в режиме переадресации Галоп только бе наращивания адреса. . Технико-экономическое преимуществ предлагаемого устройства перед прото типом заключается в том, что в нем реализован (кроме прямой и реверсивн переадресации) режим переадресации Галоп, позволяющий производить nep адресацию во всех возможных сочетаниях ячеек памяти, применена схема сравнения, позволяющая находить нес506равнение как статического, так и динамического распределения считанной и записанной информации, организована многократная выборка произвольной пары ячеек памяти. Формула изобретения 1. Устройство для контроля оперативной памяти, содержащее блок управления, первый выход которого соединен с входом первого счетчика адреса, второй выход - с первым входом регистра числа, второй вход и первый выход которого подключены соответственно к выходу и первому входу формирователя информационных сигналов, второй вход которого соединен с первым выходом первого счетчика адреса, выход - с первым входом пер; вой схемы сравнения, второй вход которой соединен с третьим выходом блока управления, а третий вход с вторым выходом регистра числа, отличающееся тем, что, с целью повышения надежности устройства, в него введены второй счетчик адреса, вход которого соединен с вторым выходом первого счетчика адреса, Фоомирователь адресных сигналов, первыйвход которого соединен с четвертым выходом блока управления, второй вход подключен к третьему выходу первого счетчика адреса, третий вход - к выходу второго счетчика адреса, а выход является одним из выходов устройства, вторая схема сравнения, первый вход которой соединен с третьим выходом блока управления, а второй вход - с вторым выходом регистра числа, и элемент ИЛ, входы которого подключены к выходам схем сравнения, а выход соединен с входом блока управления. 2. Устройство по п.1, о т л и чающееся тем, что Форми эователь адресных сигналов содержит элемент НЕ и элементы 2И-ИЛИ-НЕ, пер вые входы которых подключены к выходу элемента НЕ, вторые входы объединены с Входом элемента НЕ и являются первым входом Формирователя, третьи и четвертые входы являются соответственно вторь1м и третьим входами формирователя, выходом которого являются выходы элементов 2К-ИЛН-НЕ. Источники информации принятые во внимание при экспертизе 1.Авторское свидетельство СССР N kk3, кл. П 11 С 29/00, 1972. 2. Авторское свидетельство СССР № 526962,кл.С 1 1 С 29/00,197 (прототип).

- /7

/

i i

i

A2

fff

y N N i lY

19

///

/fff

SffJ

ff «гг/еУЗ ff

ffJff

N

Авторы

Даты

1983-03-07—Публикация

1981-10-09—Подача