г Ю

С

3 , 171 Изобретение относится к радиотех- нике, электросвязи и может использо- i ваться в системах синхронизации для построения генераторов многофазных сигналов.

Известно устройство для формирования М-ично кодируемых последовательностей импульсов, недостатком которого является низкое качество корреляционных свойств формиру- .емых последовательностей импульсов. Наиболее близким по технической . сущности к предлагаемому устройству является устройство для формирования М-ично кодированных последовательностей импульсов, недостатком которого является низкая помехоустойчивость вследствие значительных по ве

личине всплесков корреляционных функ- JQ мент ИЛИ-НЕ 3, делитель k частоты,

25

ций (Кф) формируемых последовательностей импульсов.

Цель изобретения - повышение помехоустойчивости устройств.

Поставленная цель достигается тем,/ что в устройство для формирования . многофазных сигналов, содержащее генератор импульсов, выход которого соединен с тактовым входом триггера, вход установки в единицу которого яв- зо ляется входом пуск устройства, выход триггера соединен с первым входом элемента ИЛИ-НЕ, выход которого соединен с входом установки в ноль счетчика и управляющими входами модулятора и первого регистра, информационные входы которого являются информационными входами устройства, вход последнего разряда счетчика соединен с ; входом установки в ноль триггера и вторым входом элемента ИЛИ-НЕ, выход модулятора является выходом устройства, отличающееся тем, что, с це- лью повышения помехоустойчивости уст-1

35

40

счетчик 5, первый регистр 6, первы сумматор 7, первый преобразователь кода, второй сумматор 9, второй пр образователь 10 кода, второй регис 11 и модулятор 12.

Модулятор содержит блок 13 пост ного запоминающего устройства, ген ратор 1 импульсов, счетчик 15, ци роаналоговый преобразователь 16.

Устройство работает следующим о разом.

В исходном состоянии на выходе триггера 2 зафиксирован низкий лог ческий уровень, на выходе элемента ИЛИ-НЕ 3 уровень логической единиц на всех выходах счетчиков 5 и 11 з фиксирован уровень логического нул на выходах первого регистра 6, пер вого сумматора 7, первого преобраз вателя 8 кода, второго сумматора 9 второго преобразователя 10 кода за фиксированы логические уровни, зап санные случайным образом в первый ре гистр 6 сдвига при включении питания

333

рого соединены с одноименными входами второго преобразователя кода, выходы которого соединены с одноименными информационными входами второго регистра, выходы которого соединены с одноименными информационными входами модулятора и вторыми входами второго сумматора, управляющий вход второго регистра объединен с входом делителя частоты и подключен к выходу генератора импульсов.

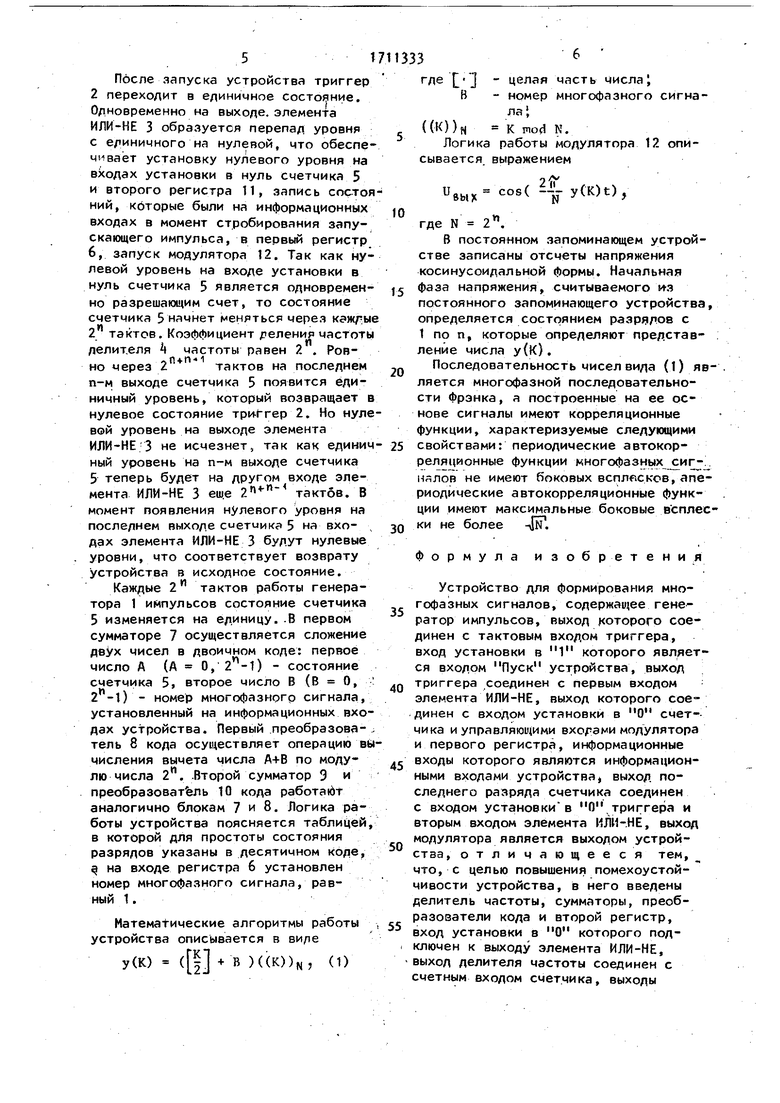

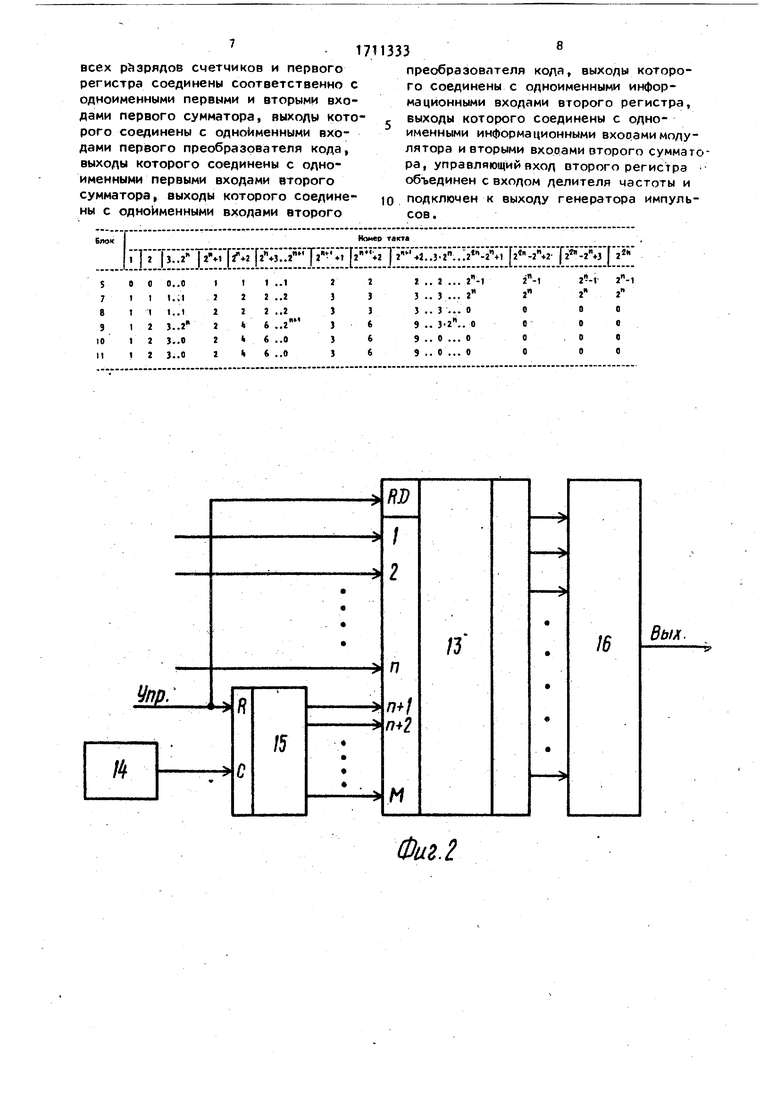

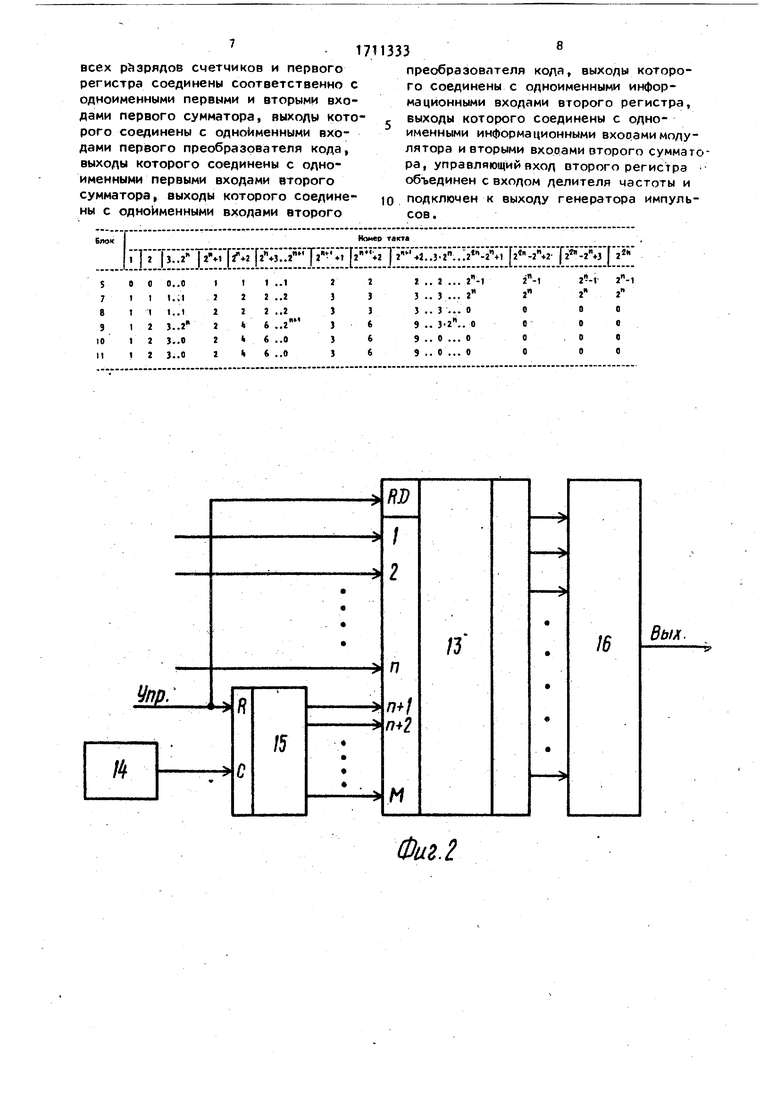

На фиг.1 представлена функциональная схема устройстваJ на фиг.2 - 5 функциональная схема модулятора; на фиг.З - временные диаграммы сигналов.

Устройство для формирования многофазных последовательностей содержит генератор 1 импульсов, триггер 2, эле

мент ИЛИ-НЕ 3, делитель k частоты,

счетчик 5, первый регистр 6, первый сумматор 7, первый преобразователь, 8 кода, второй сумматор 9, второй преобразователь 10 кода, второй регистр 11 и модулятор 12.

Модулятор содержит блок 13 постоянного запоминающего устройства, генератор 1 импульсов, счетчик 15, циф- роаналоговый преобразователь 16.

Устройство работает следующим образом.

В исходном состоянии на выходе триггера 2 зафиксирован низкий логический уровень, на выходе элемента ИЛИ-НЕ 3 уровень логической единицы, на всех выходах счетчиков 5 и 11 зафиксирован уровень логического нуля, на выходах первого регистра 6, первого сумматора 7, первого преобразователя 8 кода, второго сумматора 9, второго преобразователя 10 кода зафиксированы логические уровни, записанные случайным образом в первый регистр 6 сдвига при включении питания или

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство бесконтактного измерения излучательной способности объектов | 1991 |

|

SU1824527A1 |

| Устройство для контроля средств числового программного управления | 1988 |

|

SU1675852A1 |

| Устройство фазовой автоподстройки частоты | 1990 |

|

SU1829115A1 |

| Преобразователь кода во временной интервал | 1985 |

|

SU1300637A1 |

| Устройство для вычисления параметров нелинейных колебательных систем | 1985 |

|

SU1302243A1 |

| Способ цифрового управления многофазным инвертором | 1989 |

|

SU1683154A1 |

| Формирователь импульсов | 1986 |

|

SU1383468A1 |

| Синтезатор частот | 1985 |

|

SU1363457A1 |

| Программируемый многофазный тактовый генератор | 1990 |

|

SU1785069A1 |

| Интегрирующий аналого-цифровой преобразователь | 1989 |

|

SU1633493A1 |

роиства, в него введены делитель час- логические уровни, соответствующие нототы, сумматоры, преобразователи кода и второй регистр, вход установи ки в ноль которого подключен к выходу элемента ИЛИ-НЕ, выход делителя частоты соединен со счетным входом счетчика, выходы всех разрядов счетчика и первого регистра соединены соответственно с одноименными первыми и вторыми входами первого сумматора, выходы которого соединены с одноименными входами первого преобразователя кода, выходы которого соединены с одноименными первыми входами второго сумматора, выходы котомеру выбранной многофазной последовательности в двоичном коде в момент поступления последнего сигнала на входе Пуск устройства , на

0 всех выходах счетчика 15 зафиксированы уровни логического нуля, на выходах блока 13 постоянного запоминающего устройства зафиксированы уровни логической единицы, соответ55 ствующиесостоянию запрета считывания информации из постоянного запоминающего устройства{ на выходе циф- роаналогового преобразователя напря- ; жение равно нулю.. I

логические уровни, соответствующие номеру выбранной многофазной последовательности в двоичном коде в момент поступления последнего сигнала на входе Пуск устройства , на

всех выходах счетчика 15 зафиксированы уровни логического нуля, на выходах блока 13 постоянного запоминающего устройства зафиксированы уровни логической единицы, соответствующиесостоянию запрета считывания информации из постоянного запоминающего устройства{ на выходе циф- роаналогового преобразователя напря- ; жение равно нулю.. I

мента ИЛИ-НЕ 3 еще 2

гл-п-

тактов. В

После запуска устройства триггер 2 переходит в единичное состояние. Одновременно на выходе, элемента ИЛИ-НЕ 3 обрадуется перепад уровня с единичного на нулевой, что обеспечивает установку нулевого уровня на входах установки в нуль счетчика 5 и второго регистра 11, запись состояний, которые были на информационных входах в момент стробирования запускающего импульса, в первый регистр 6, запуск модулятора 12. Так как нулевой уровень на входе установки в нуль счетчика 5 является одновременно разрешающим счет, то состояние счетчика 5 начнет меняться через каж/тые 2 тактов. Коэффициент деления частоты делителя частоты равен 2 . Ровно через тактов на последнем п-м выходе счетчика 5 появится единичный уровень, который возвращает в нулевое состояние триггер 2. Но нулевой уровень на выходе элемента ИЛИ-НЕ 3 не исчезнет, так как единич ный уровень на n-м выходе счетчика 5 теперь будет на другом входе эле

момент появления нулевого уровня на последнем выходе сметчика 5 на вхо- ч дах элемента ИЛИ-НЕ 3 будут нулевые уровни, что соответствует возврату устройства в исходное состояние.

Каждые 2й тактов работы генератора 1 импульсов состояние счетчика 5 изменяется на единицу. .В первом сумматоре 7 осуществляется сложение деУх чисел в двоичном коде: первое число А (А 0, ) - состояние счетчика 5, второе число В (В 0, ; . 2м-1) - номер многофазного сигнала, установленный на информационных входах устройства. Первый преобразова-; тель 8 кода осуществляет операцию вычисления вычета числа А+В по модулю числа 2П. .Второй сумматор 9 и преобразователь 10 кода работают аналогично блокам 7 и 8. Логика работы устройства поясняется таблицей, в которой для простоты состояния разрядов указаны в десятичном коде, 3 на входе регистра 6 установлен номер многофазного сигнала, равный 1.

Математические алгоритмы работы устройства описывается в виле

у(К) (| + В )(, (1)

где Ј - целая часть числа ,

((Ю)

N

- номер многофазного сигнала , К mod N..

Логика работы модулятора 12 описывается, выражением

21

Ј

cos( y(K)t),

где N 2 .

В постоянном запоминающем устройстве записаны отсчеты напряжения косинусоидальной формы. Начальная фаза напряжения, считываемого и-з постоянного запоминающего устройства, определяется состоянием разрядов с 1 по п, которые определяют представление числа у(К).

Последовательность чисел вида (1) яв- . ляется многофазной последовательности Фрэнка, а построенные на ее основе сигналы имеют корреляционные функции, характеризуемые следующими свойствами: периодические автокорреляционные функции многофазных сиг-: налов не имеют боковых всплесков, апериодические автокорреляционные функ- . ции имеют максимальные боковые всплески не более -jNi.

Формула изобретения

5

0

5

0

Устройство для формирования многофазных сигналов, содержащее генератор импульсов, выход которого соединен с тактовым входом триггера, вход установки в 1м которого является входом Пуск устройства, выход триггера соединен с первым входом элемента ИЛИ-НЕ, выход которого соединен с входом установки в 0й счет-- чика и управляющими входами модулятора и первого регистра, информационные входы которого являются информационными входами устройстваj выход последнего разряда счетчика соединен с входом установки в О триггера и вторым входом элемента ИЛИ-НЕ, выход модулятора является выходом устройства, отли чающее ся тем, что, с целью повышения помехоустойчивости устройства, в него введены делитель частоты, сумматоры, преобразователи кода и второй регистр, вход установки в О которого под- ключей к выходу элемента ИЛИ-НЕ, выход делителя частоты соединен с счетным входом счетчика, выходы

всех разрядов счетчиков и первого регистра соединены соответственно с одноименными первыми и вторыми входами первого сумматора, выходы которого соединены с одноименными входами первого преобразователя кода, выходы которого соединены с одноименными первыми входами второго сумматора, выходы которого соединены с одноименными входами второго

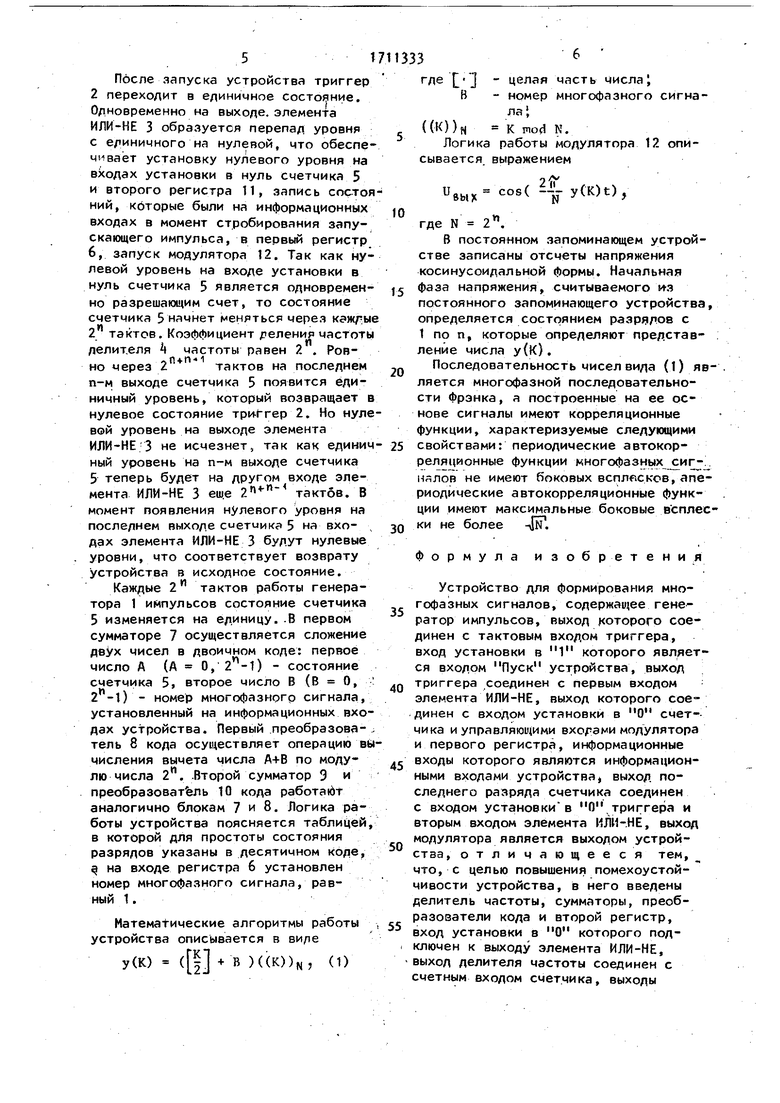

Блок

Номер такта

уг | лГр+Гр+ГГ JJ % Г Г JЛ ; Г г Л2i;-лi --2 2 Jj Ч з 2 2;

преобразователя кода, выходы которого соединены с одноименными информационными входами второго регистра, выходы которого соединены с одноименными информационными вхооами модулятора и вторыми входами второго сумматора, управляющий вход второго регистра объединен с входом делителя частоты и подключен к выходу генератора импульсов.

Номер такта

Фиг. 2

а 6

8

о|-Л

oUTJTJTJTJHLTlJTJlJTXlJ oU-J-1.,.

и - ... ..J

rLTLFL

ж

0

Номер такта

J

.ГЪП

..

22/7-/

ft/г З

22

| Деревянный коленчатый рычаг | 1919 |

|

SU150A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для формирования М-ично кодированных последовательностей импульсов | 1986 |

|

SU1392620A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-02-07—Публикация

1990-01-18—Подача