Изобретение относится к вычислительной технике и может быть использовано при тестировании элементов вычислительной техники.

Цель изобретения - расширение функциональных возможностей за счет проверки устройств с двунаправленными шинами в реальном времени.

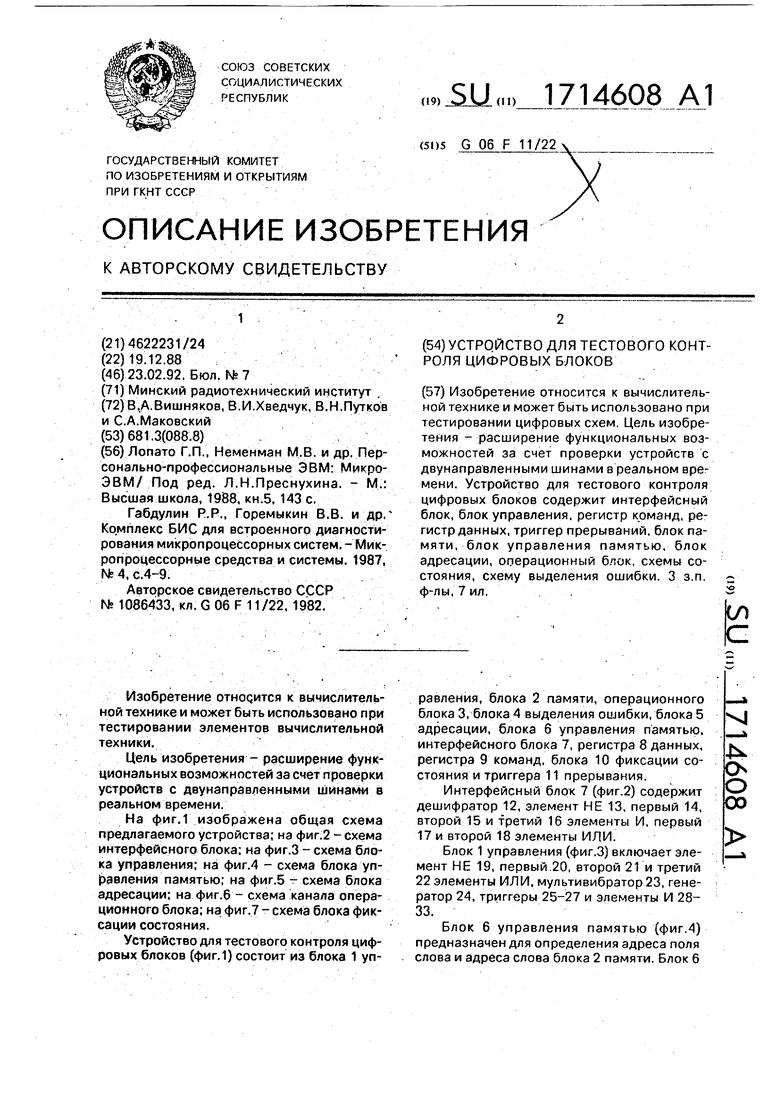

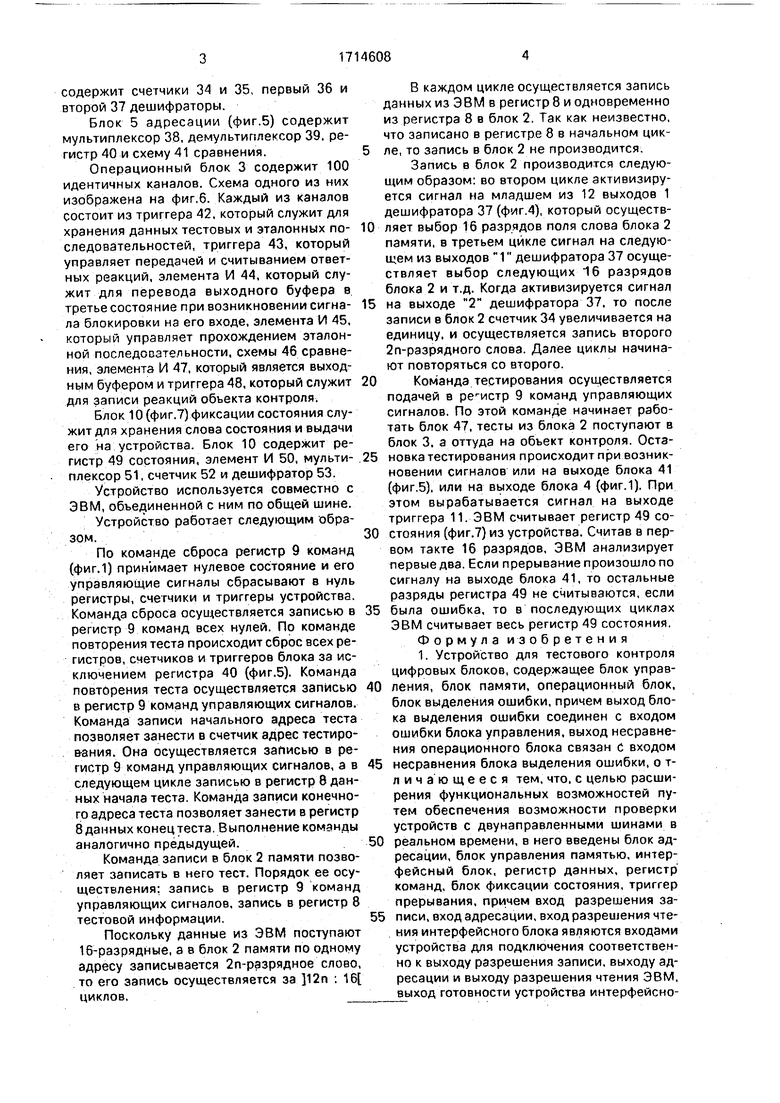

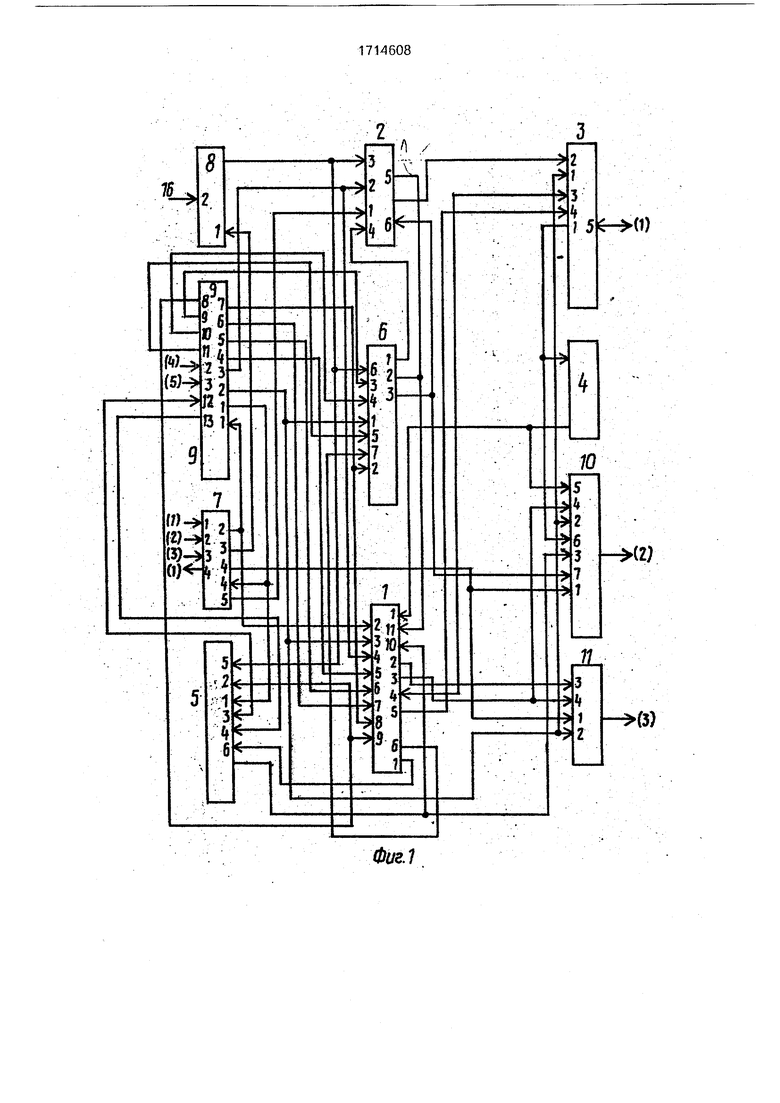

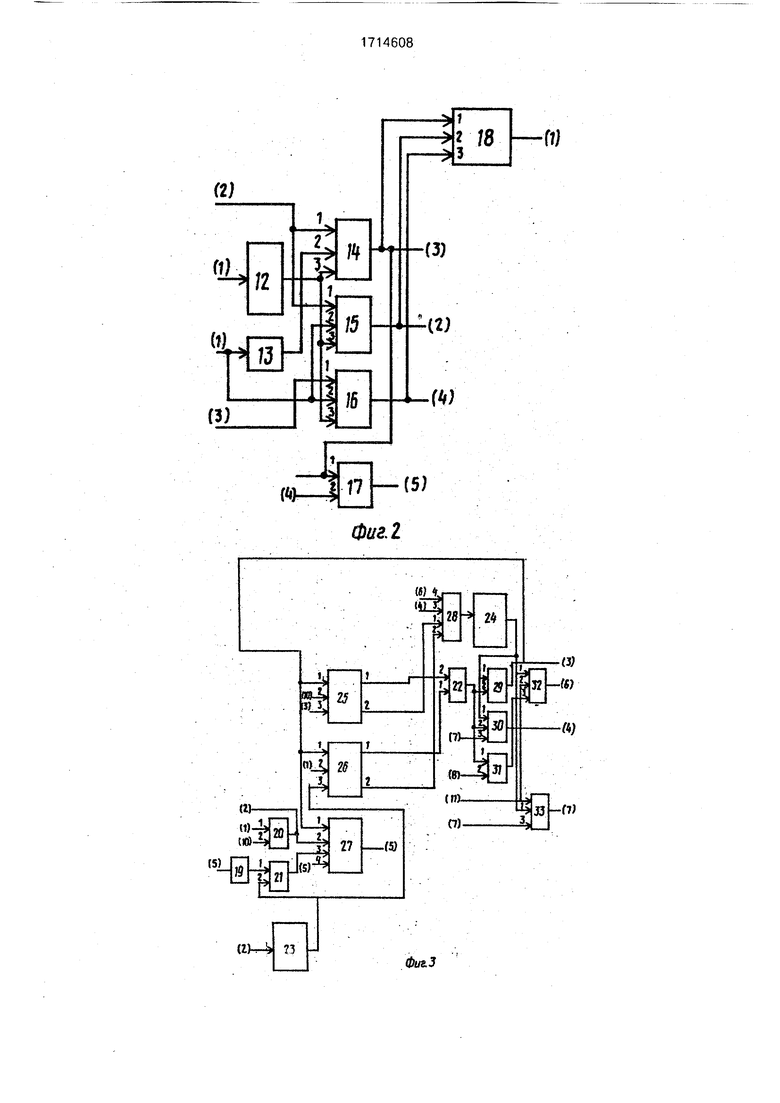

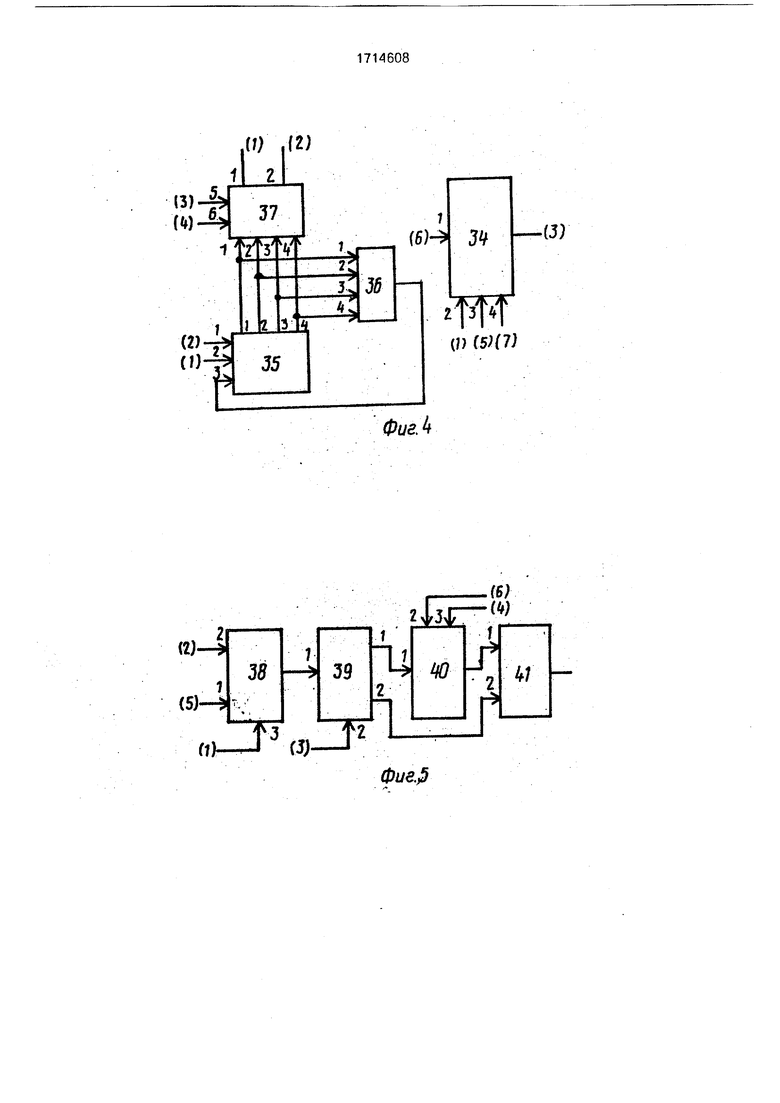

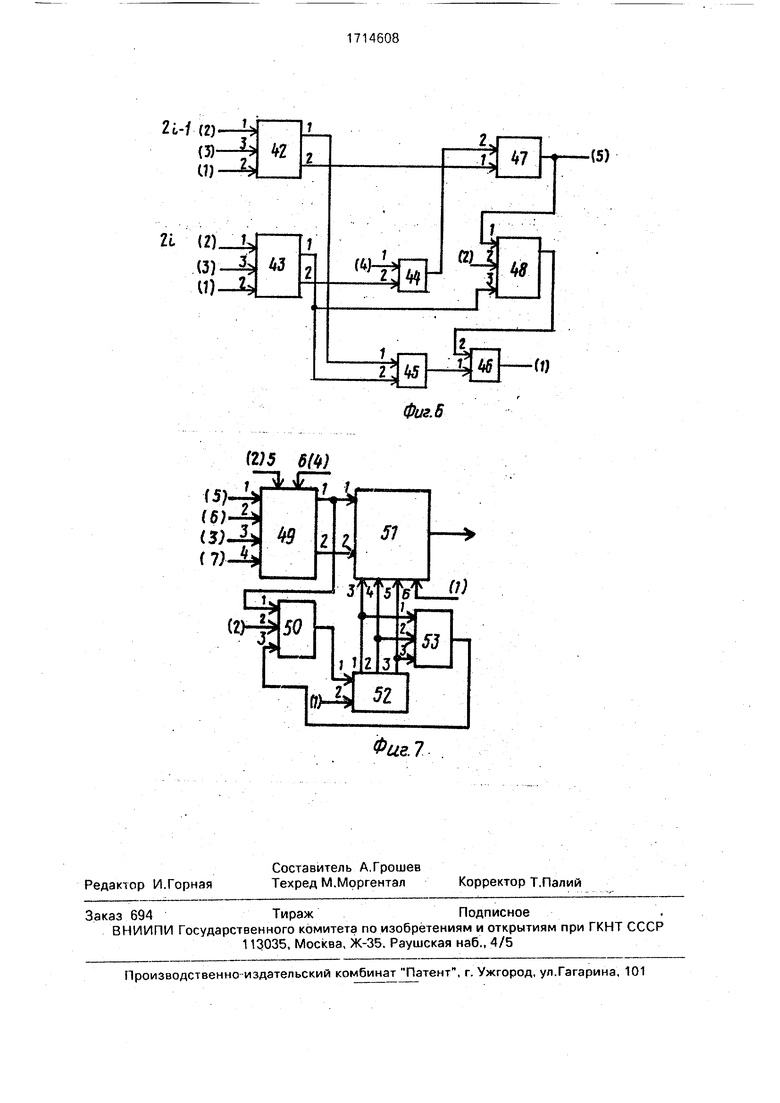

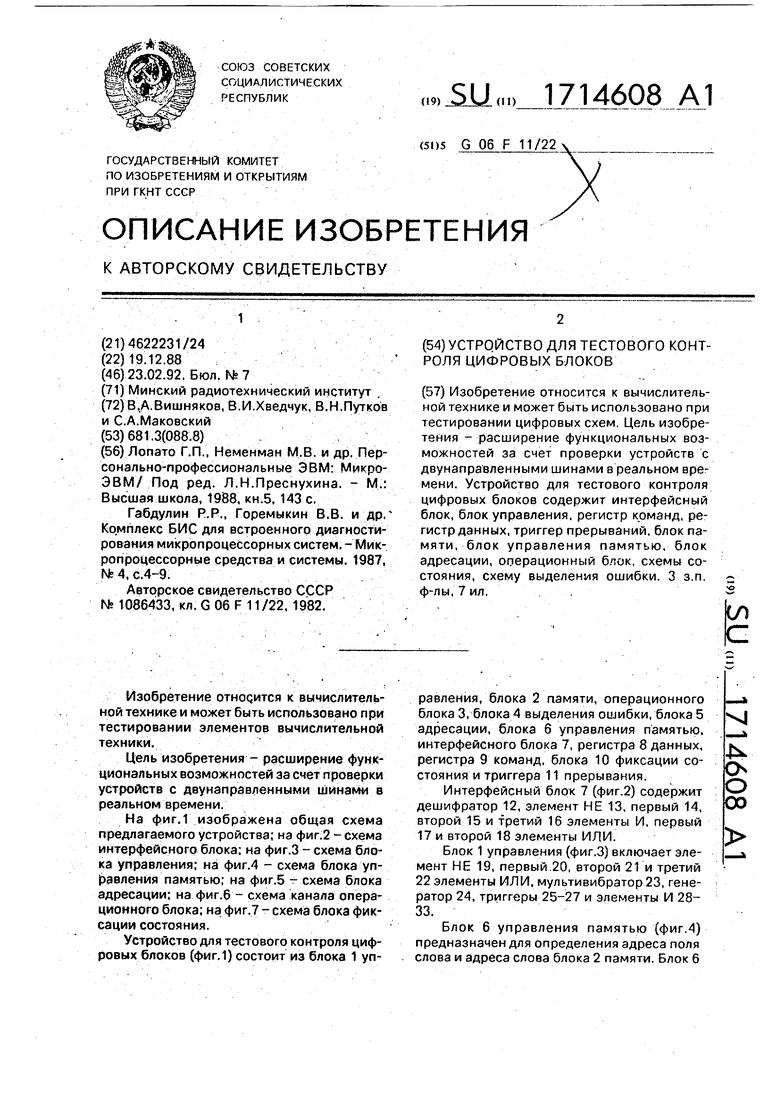

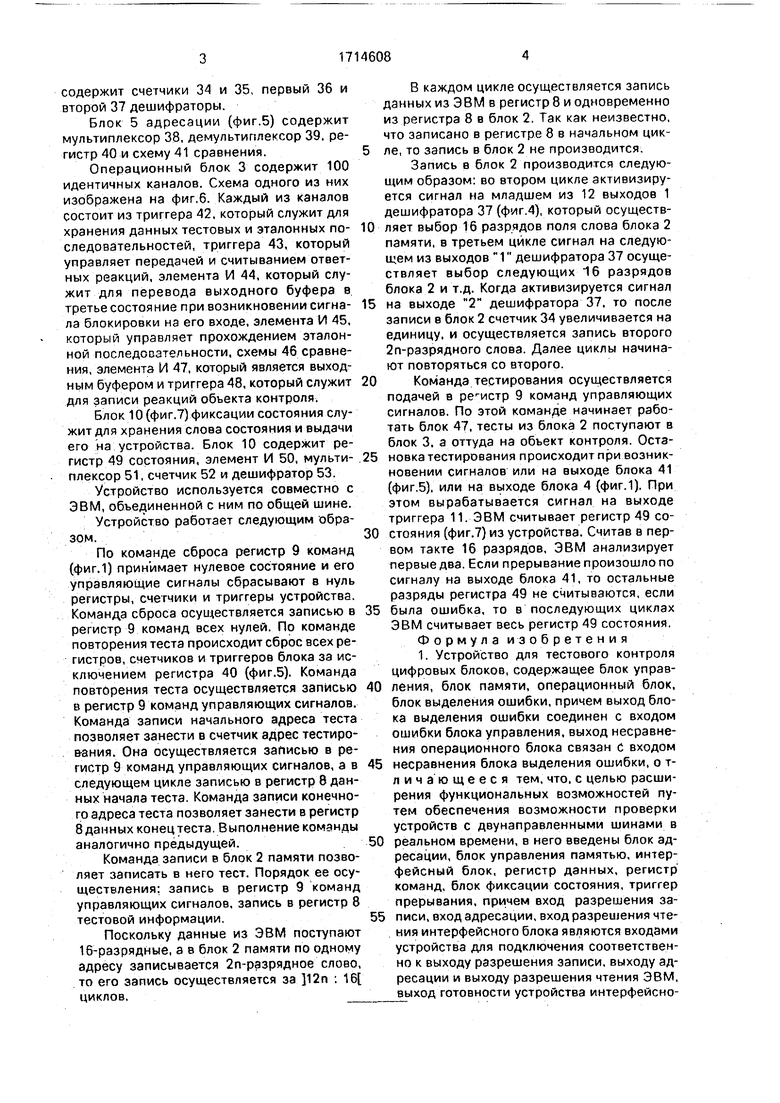

На фиг, 1 изображена общая схема предлагаемого устройства: на фиг.2 - схема интерфейсного блока; на фиг.З - схема блока управления; на фиг.4 - схема блока уп|:)авленйя памятью; на фиг.5 - схема блока адресации; на фиг.6 - схема канала операционного блока; на фиг.7 - схема блока фиксации состояния.

Устройство для тестового контроля цифровых блоков (фиг. 1) состоит из блока 1 управления, блока 2 памяти, операционного блока 3, блока 4 выделения ошибки, блока 5 адресации, блока б управления памятью, интерфейсного блока 7, регистра 8 данных, регистра 9 команд, блока 10 фиксации состояния и триггера 11 прерывания.

Интерфейсный блох 7 (фиг.2) содержит дешифратор 12, элемент НЕ 13, первый 14, второй 15 и третий 16 элементы И. первый 17 и второй 18 элементы ИЛИ.

Блок 1 управления (фиг.З) включает элемент НЕ 19, первый.20, второй 21 и третий 22 элементы ИЛИ, мультивибратор 23, генератор 24, триггеры 25-27 и элементы И 2833.

Блок 6 управления памятью (фиг.4) предназначен для определения адреса поля слова и адреса слова блока 2 памяти. Блок 6

содержит счетчики 34 и 35. первый 36 и второй 37 дешифраторы.

Блок 5 адресации (фиг.5) содержит мультиплексор 38, демультиплексор 39, регистр 40 и схему 41 сравнения.

Операционный блок 3 содержит 100 идентичных каналов. Схема одного из них изображена на фиг.б. Каждый из каналов состоит из триггера 42, который служит для хранения данных тестовых и эталонных последовательностей, триггера 43, который управляет передачей и считыванием ответных реакций, элемента И 44, который служит для перевода выходного буфера в третье состояние при возникновении сигнала блокировки на его входе, элемента И 45, который управляет прохождением эталонной последовательности, схемы 46 сравнения, элемента И 47, который является выходным буфером и триггера 48, который служит для записи реакций объекта контроля.

Блок 10 (фиг.7) фиксации состояния служит для хранения слова состояния и выдачи его на устройства. Блок 10 содержит регистр 49 состояния, элемент И 50, мультиплексор 51, счетчик 52 и дешифратор 53.

Устройство используется совместно с ЭВМ, объединенной с ним по общей шине. Устройство работает следующим образом.

По команде сброса регистр 9 команд (фиг.1) принимает нулевое состояние и его управляющие сигналы сбрасывают в нуль регистры, счетчики и триггеры устройства. Команда сброса осуществляется записью в регистр 9 команд всех нулей. По команде повторения теста происходит сброс всех регистров, счетчиков и триггеров блока за исключением регистра 40 (фиг.5). Команда повторения теста осуществляется записью в регистр 9 команд управляющих сигналов. Команда записи начального адреса теста позволяет занести в счетчик адрес тестиров ания. Она осуществляется записью в регистр 9 команд управляющих сигналов, а в следующем цикле записью в регистр 8 данных начала теста. Команда записи конечного адреса теста позволяет занести в регистр 8 данных конец теста. Выполнение команды аналогично предыдущей.

Команда записи в блок 2 памяти позволяет записать в него тест. Порядок ее осуществления: запись в регистр 9 команд управляющих сигналов, запись в регистр В тестовой информации.

Поскольку данные из ЭВМ поступают 16-разрядные, а в блок 2 памяти по одному адресу записывается 2п-разрядное слово, то его запись осуществляется за 12п ; 16 циклов.

В каждом цикле осуществляется запись данных из ЭВМ в регистр 8 и одновременно из регистра 8 в блок 2. Так как неизвестно, что записано в регистре 8 в начальном цикле, то запись в блок 2 не производится.

Запись в блок 2 производится следующим образом: во втором цикле активизируется сигнал на младшем из 12 выходов 1 дешифратора 37 (фиг.4), который осуществляет выбор 16 разрядов поля слова блока 2 памяти, в третьем цикле сигнал на следующем из выходов 1 дешифратора 37 осуществляет выбор следующих 16 разрядов блока 2 и т.д. Когда активизируется сигнал на выходе 2 дешифратора 37, то после записи в блок 2 счетчик 34 увеличивается на единицу, и осуществляется запись второго 2п-разрядного слова. Далее циклы начинают повторяться со второго.

Команда тестирования осуществляется подачей в реистр 9 команд управляющих сигналов. По этой команде начинает работать блок 47, тесты из блока 2 поступают в блок 3, а оттуда на объект контроля. Остановка тестирования происходит при возникновении сигналов или на выходе блока 41 (фиг.5). или на выходе блока 4 (фиг.1). При этом вырабатывается сигнал на выходе триггера 11. ЭВМ считывает регистр 49 состояния (фиг.7) из устройства. Считав в первом такте 16 разрядов, ЭВМ анализирует первые два. Если прерывание произошло по сигналу на выходе блока 41, то остальные разряды регистра 49 не считываются, если была ошибка, то в последующих циклах ЭВМ считывает весь регистр 49 состояния.

Формула изобретения

1. Устройство для тестового контроля цифровых блоков, содержащее блок управления, блок памяти, операционный блок, блок выделения ошибки, причем выход блока выделения ошибки соединен с входом ошибки блока управления, выход несравнения операционного блока связан с входом несравнения блока выделения ошибки, о тличающееся тем. что, с целью расширения функциональных возможностей путем обеспечения возможности проверки устройств с двунаправленными шинами в реальном времени, в него введены блок адресации, блок управления памятью, интерфейсный блок, регистр данных, регистр команд, блок фиксации состояния, триггер прерывания, причем вход разрешения записи, вход адресации, вход разрешения чтения интерфейсного блока являются входами устройства для подключения соответственно к выходу разрешения записи, выходу адресации и выходу разрешения чтения ЭВМ, выход готовности устройства интерфейсного блока является выходом устройства для подключения к входу готовности ЭВМ, первый выход интерфейсного блока соединен с входами разрешения записи регистра команд и блока управления, второй выход интерфейсного блока соединен с входом записи регистра данных, третий выход интерфейсного блока соединен с входом чтений блока фиксации состояния и триггера прерывания, четвертый выход интерфейсного блока соединен с входом записи блока памяти, вход сброса регистра команд является входом устройства для подключения к выходу сброса ЭВМ, информационный вход регистра команд является входом устройства для подключения к информационному выходу ЭВМ, с первого по тринадцатый выходы регистра команд соединены соответственно с управляющим входом интерфейсного блока и первым управляющим входом блока адресации, с первым управляющим входом блока управления, памятью и первым управляющим входом блока управления, первым управляющим входом блока выделения ошибки, первым управляющим входом операционного блока и первым управляющим входом триггера прерывания, с управляющим входом блока памяти, вторым управляющим входом блока управления, с входом установки блока управления, с третьим управляющим входом блока управления, четвертым управляющим входом блока управления, с вторым управляющим входом блока управления памятью и пятым управляющим входом блока управления, с информационным входом блока уп равления и первым информационным входом блока адресации,.с третьим управляющим входом блока управления памятью, с четвертым управляющим в)одом-блока управления памятью, с пятым управляющим входом блока управления памятью, с вторым управляющим входом блока адресации, с третьим управляющим входом блока адресации, информационный вход регистра данных является входом устройства для подключения к информационному выходу ЭВМ, выход регистра данных соединен с информационным входом блока памяти, первый, второй, третий входы адресации которого соединены соответственно с первым, вторым и третьим выходами блока управления памятью, выход блока памяти соединен с информационным входом опе рационного блока, информационный выход регистра данных соединен с входом адресации блока управления памятью и вторым информационным входом блока адресации, четвертый управляющий вход которого соединен с первым выходом блока управления.

выход Конец теста блока адресации соединен с входами Конец теста блока управления и блока фиксации состояния, шестой управляющий вход блока управления соеди5 ней с вторым выходом блока управления памятью, второй выход блока управления соединен с входом установки признака триггера прерывания, третий, четвертый, пятый выходы блока управления соединены

10 соответственно с входами синхронизации триггера прерывания и блока фиксации состояния, с вторым управляющим входом операционного блока, с входом блокировки операционного блока, информационный

15 вход-выход операционного блока является информационным входом-выходом устройства для подключения к контролируемому объекту, выход блока выделения ошибки соединен с входом ошибки блока фиксации

0 состояния, выход несравнения операционного блока соединен с входом несравнения блока фиксации состояния, вход адреса останова блока фиксации состояния соединен с третьим выходом блока управления памятью, выход блока фиксации состояния является выходом устройства для подключения к входу конца работы ЭВМ, выход триггера прерывания является выходом устройства для подключения к входу

0 запроса прерывания ЭВМ, шестой выход блока управления соединен с шестым входом блока управления памятью.

2. Устройство по П.1, о т л и ч а ю щ е ес я тем, что блок управления содержит эле5 мент НЕ, три элемента ИЛИ. мультивибра. тор, генератор, три триггера, шесть

элементов И, причем первый вход первого

элемента ИЛИ соединен с входом ошибки

блока управления, второй вход первого элемента ИЛИ соединен с входом конца теста блока управления, выход первого элемента ИЛИ соединен с вторым выходом блока управления и с входом установки первого триггера, выход которого является пятым

5 выходом блока управления, вход элемента НЕ соединен с входом установки блока управления, а выход соединен с первым входом второго элемента ИЛИ, выход которого соединен с в)«эдом сброса первого триггера,

0 вход управления которого соединен с входом установки блока управления, вход мультивибратора соединен с входом разрешения записи блока управления, выход мультивибратора соединен с вторым входом второго элемента ИЛИ и с входом сброса второго триггера, вход установки которого соединен с входом ошибки блока управления, прямой выход второго триггера соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с прямым выходом третьего триггера, инверсный выход которого соединен с первым входом первого элемента И, инверсный выход второго триггера соединен с вторым входом первого элемента И. вход установки третьего триггера соединен с входом конца теста блока управления, вход управления третьего триггера соединен с первым управляющим входом блока управления, третий вход первого элемента И соединен с вторым управляющим входом блока управления, четвертый вход первого элемента И соединен с третьим управляющим входом блока управления, выход первого элемента И соединен с входом генератора, выход которого соединен с первыми входами второго, третьего, четвертого и пятого элементов И, второй вход второго элемента И соединен с вторым входом третьего элемента И, с первым входом шестого элемента И и с выходом третьего элемента ИЛИ, второй вход шестого элемента И соединен с пятым управляющим входом блока управления, третий вход третьего элемента И соединен с четвертым управляющим входом блока управления, второй вход пятого элемента И и второй вход четвертого элемента И соединены с седьмым управляющим входом блока управления, третий вход пятого элемента И соединен с информационным входом блока управления, выход второго элеме 1та И соединен с входами синхронизации перво-. го. второго, третьего триггеров и является третьим выходом блока управления, выход третьего элемента И соединен с четвертым выходом блока управления, выход шестого элемента И соединен с третьим входом четвертого элемента И, выход четвертого элемента И соединен с шестым выходом блока управления, выход пятого элемента И соединён с первым выходом блока управления, 3, Устройство по п; t, о т л и ч а ю щ е ес я тем, что блок.управления памятью состоит из двух дешифраторов и Двух счетчиков, причем первый управляющий вход первого счетчика соединён с вторым управляющим входом блока управления памятью, второй управляющий вход первого счетчика соединен с первым управляющим входом блока управленЙ1я памятью, третий управляющий вход первого счетчика соединен с выходом первого дешифратора, первый, второй, третий, четвертый выходы первого счетчика соединены cootBeTCTBeHHO с первыми, вторыми, третьими, четвертыми информационными входами первого и второго дешифраторов, первый и второй управляющие входы второго дешифратора соединены соответственно с третьим и четвертым

управляющими входами блока управления памятью, первый и второй выходы второго дешифратора являются первым и вторым выходами блока управления памятью, информационный вход второго счетчика соединен с входом адресации блока управления памятью, первый, второй, третий управляющие входы второго счетчика соединены соответственно с первым, пятым и шестым управляющими входами блокаулравления памятью, выход второго счетчика является третьим выходом блока управления памятью,

4. Устройство по П.1, 6 т л и ч а ю щ е ег с я тем, что операционный блок имеет п

каналов, каждый из которых состоит из трех триггеров трех элементов И, схемы сравнения, причем информационный вход первого триггера соединен с информационным входом операционного блока, инфррмационный вход второго триггера соединен с информационным входом операционного блока, первый и второй управляющие входы первого и второго триггеров соединены соответственно с первым и вторым управляющими входами операционного блока, прямой выход первого триггера соединен с первым входом первого элемента И, инверсный выход первого триггера соединен с первым входом второго элемента И, второй

вход которого соединен с выходом третьего элемента И, выход второго элемента И является информационным входом-выходом операционного блока и соединен с информационным входом третьего триггера, первый управляющий вход которого соединен с вторым управляющим входом операционного блока, второй управляющий вход третьего триггера соединен с прямым выходом второго триггера, а также с вторым входом

первого элемента И, выход которого соединен с первым информационным входом схемы сравнения, второй информационный вход которого соединен с выходом третьего триггера, выход схемы сравнения является

выходом несравнения операционного блока, первый вход третьего элемента И соединен с входом блокировки операционного блока, второй вход третьего элемента И соединен с инверсным выходом второго триггера.

Фиг. 1

(5)

(г)-гЛ

Фиг. 2

f7)

Фи&З

фие.

| название | год | авторы | номер документа |

|---|---|---|---|

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1988 |

|

SU1605241A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЭЛЕКТРОННОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1992 |

|

RU2066877C1 |

| Устройство для обмена информацией между объектом контроля и электронной вычислительной машиной | 1983 |

|

SU1156078A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для обмена информацией | 1989 |

|

SU1702378A1 |

Изобретение относится к вычислительной технике и может быть использовано при тестировании цифровых схем. Цель изобретения - расширение функциональных возможностей за счет проверки устройств с двунаправленными шинами в реальном времени. Устройство для тестового контроля цифровых блоков содержит интерфейсный блок, блок управления, регистр команд, регистр данных, триггер прерываний, блок памяти, блок управления памятью, блок адресации, операционный блок, схемы состояния, схему выделения ошибки. 3 з.п. ф-лы, 7 ил..^

| ЛопатоТ.П., Неменман М.В | |||

| и др | |||

| Персонально-профессиональные ЭВМ: Микро- ЭВМ/ Под ред | |||

| Л.Н.Преснухина | |||

| - М.: Высшая школа, 1988, кн.5, 143 с.Габдулин P.P. | |||

| Горемыкин В.В | |||

| и др.~ Комплекс БИС для встроенного диагностирования микропроцессорных систем | |||

| - Микропроцессорные средства и системы | |||

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

Авторы

Даты

1992-02-23—Публикация

1988-12-19—Подача