дулю два, выходы блока управления соединены соответственно с входом первого элемента НЕ и вторым входом первого элемента И-НЕ, с управляюпщми входами регистров и блока вывода данных, входы которого подключены к выходам пятого регистра, и одним из входов компаратора, другие входы которого соединены с выходами блока ввода данных и другими входами первого мультиплексора, выходы блока вывода адреса, входы блока ввода данных и выходы блока вьшода данных являются соответственно адресными выходами и информационными входами и выходсгми устройства, входы пуска, останова и режима ожидания блока управления и другие входы третьего мульт1тлексора являются управлянгщимй входами устройства, входами и выходами прерывания которого являются другие входы и выходы блока прерьгоания, а выходами обращения ;выходы первого элемента НЕ и первого элемента И-НЕ.

2. Устройство по п. I, отличающееся тем, что блок

прерываний содержит триггеры, формирователи одиночных импульсов, второй элемент НЕ, элемент И и элемен. ты согласования, причем выход первого элемента согласования соединен с первым входом элемента И, выход которого подключен к счетному входу первого триггера, установочньп вход которого соединен с выходом первого и входом второго формирователей одиночных импульсов, выход второго элемента согласования подключен к входу первого формирователя одиночных импульсов и входу второго элемента НЕ, выход которого соединен со счетным входом второго триггера, вход установки которого подключен к выходу второго формирователя одиночных импульсов, выходы первого и второго триггеров соединены соответственно с входами третьего и четвертого элементов согласования, выходы которых являются выходами блока, одним из входов которого является второй вход элемента И, а другими входами - входы первого и второго элементов согласования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Микропроцессор | 1985 |

|

SU1330634A1 |

| Микропроцессор | 1984 |

|

SU1257657A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Устройство для обмена информацией | 1989 |

|

SU1702378A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ПАМЯТИ, содержащее блок управления, один из входов которого подключен к выходу компаратора, регистры с первого по шестой, мультиплексоры, арифметико-логический блок, первый элемент НЕ и первый элемент И-НЕ, причем выходы первого мультиплексора подключены ко входам первого регистра, выходы которого соединены с одним из входов арифметико-логического блока, выходы которого подключены ко входам второго и третьего регистров, и одним из входов второго мультиплексора, выходы которого соединены с входами четвертого регистра, выходы второго регистра подключены к одним из входов первого мультиплексора, отличающее ся тем, что, с целью повышения быстродействия устройства, в него введены блок памяти микрокоманд, сумматор по модулю два. третин мультиплексор, накопитель,, седьмой и восьмой регистры, дешифратор, блок перерь вания, блок ввода данных, блок вывода данных, блок ввода управляющих сигналов и блок вывода адреса, причем входы пятого регистра соединены с выходами третьего регистра, входы и выходы шестого регистра подключены соответственно к выходам четвертого регистра и ко входам блока вывода адреса, выходы седьмого регистра соединены с входами блока памяти микpoкoмa щ, выходы которого подключены ко входам восьмого регистра, одни из выходов которого соединены соответственно Q S с одними из входов седьмого регистра, с одними из входов дешифратора, с входами сумматора по модулю два, с управляющими входами первого, второго и третьего мультиплексоров, накопителя, арифметико-логического блока и компаратора, с первым входом первого элемента И-НЕ и с одним из входов блока прерывания, другие Ю входы седьмого регистра подключены соответственно к выходам дешифратосл ра и к выходам второго регистра и C3t) другим входам дешифратора, одни из CD входов третьего мультиплексора соединены соответственно с выходами второго регистра и с выходами четвертого регистра, а выходы подключены ко входам накопителя, выходы которого соединены с другими входами арифметико-логического блока и второго мультиплексора, другие входы блока управления подключены соответственно к выходам блока ввода управляющих сигналов, к другим пыходлм восьмого регистра и к выходу сумгттора по мо

Изобретение относится к вычислительной технике и может быть использовано при осуществлении наладки и контроля периферийных и оперативных запоминающих устройств вычислительной тех1шки.

Известно устройство для контроля блоков памяти, содержащее процессор, базовое оперативное запоминающее устройство , внешнее запоминающее устройство, которое хранит программу проверки проверяемого устройстваС)Jt

Недостатком этого устройства является громоздкость и высокая стоимость оборудования, а тгисже низкое быстродействие.

Наиболее близким техническим решением к предлагаемому является устройство для контроля блоков памяти, содержащее блок управления, арифметический блок, блок обнаружения и коррекции ошибок, первый регистр, генератор контрольных сигналов, второй и третий регистры, триггер, элемент НЕ, элемент И, четвертый, пятый и шестой регистры, первый и второй блоки сравнения, причем первый выход блока обнаружения

и коррекции ошибок соединен с первым входом третьего регистра., а второй вькод t; с входом управления и первым входом арифметического блока, второй вход которого подключен к первому выходу блока управления, третий вход - к выходу третьего регистра, а первый выход - ко входу первого регистра, выход которого соединен с входом генератора контрольных: сигналов, выход которого подключен к первому входу второго регистра, выход которого является выходом устройства С2 1.

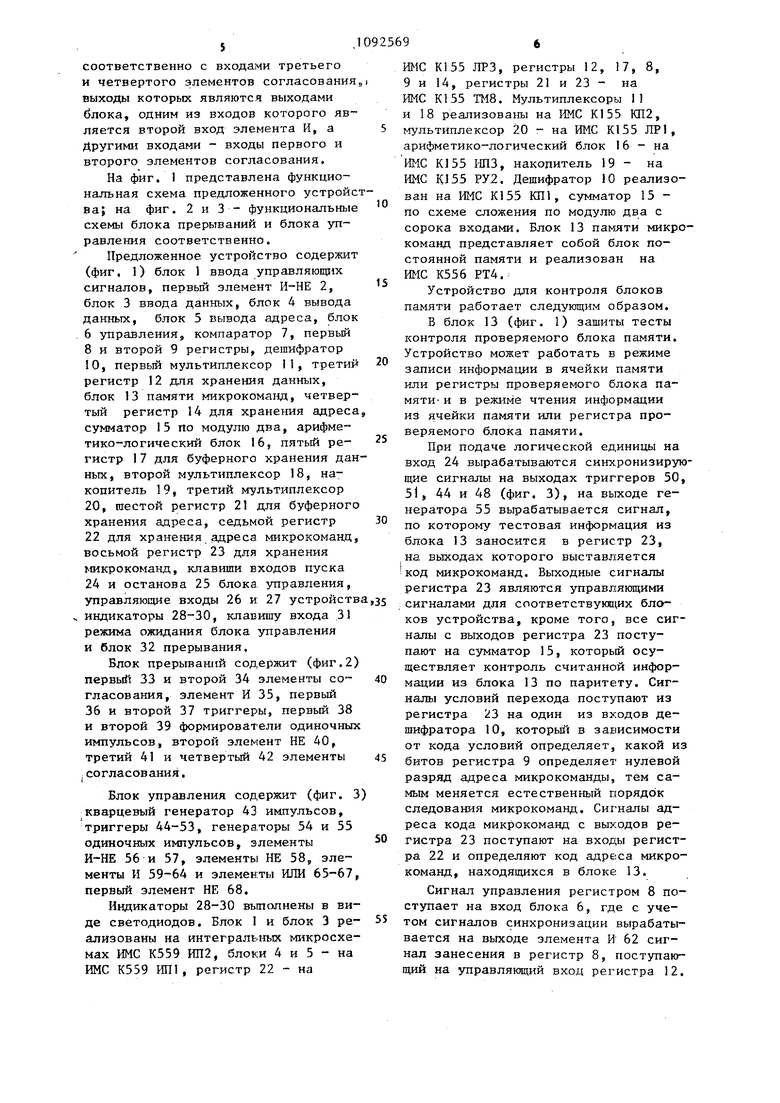

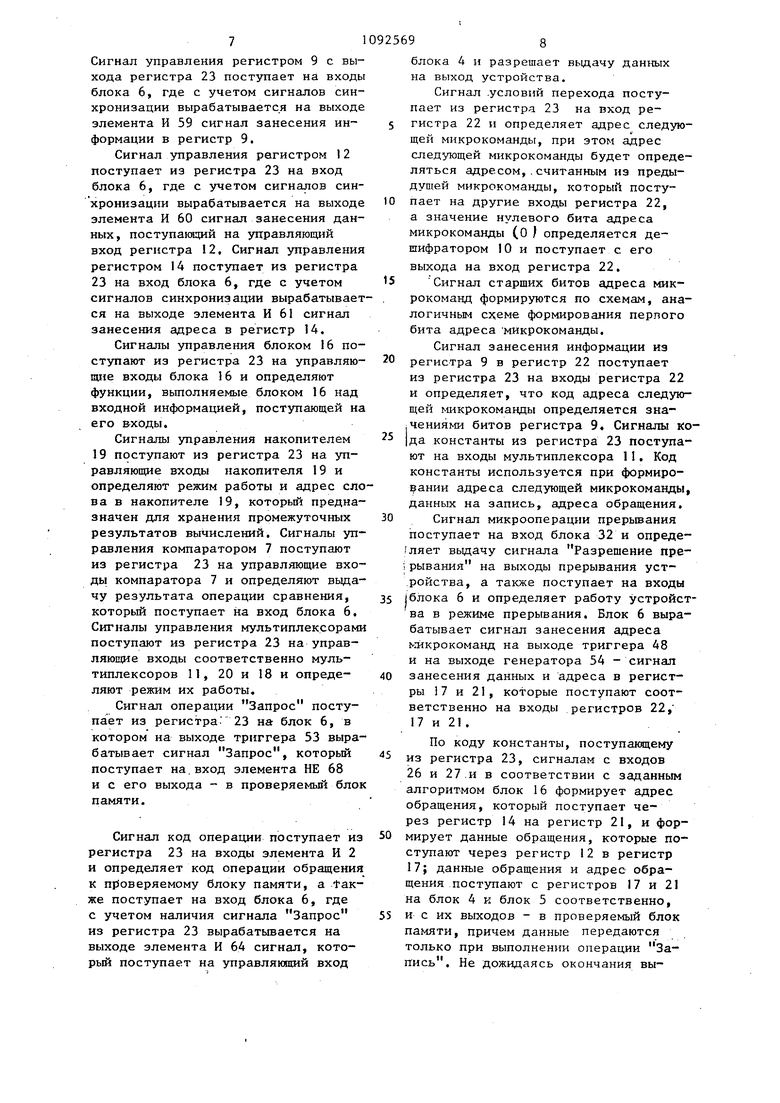

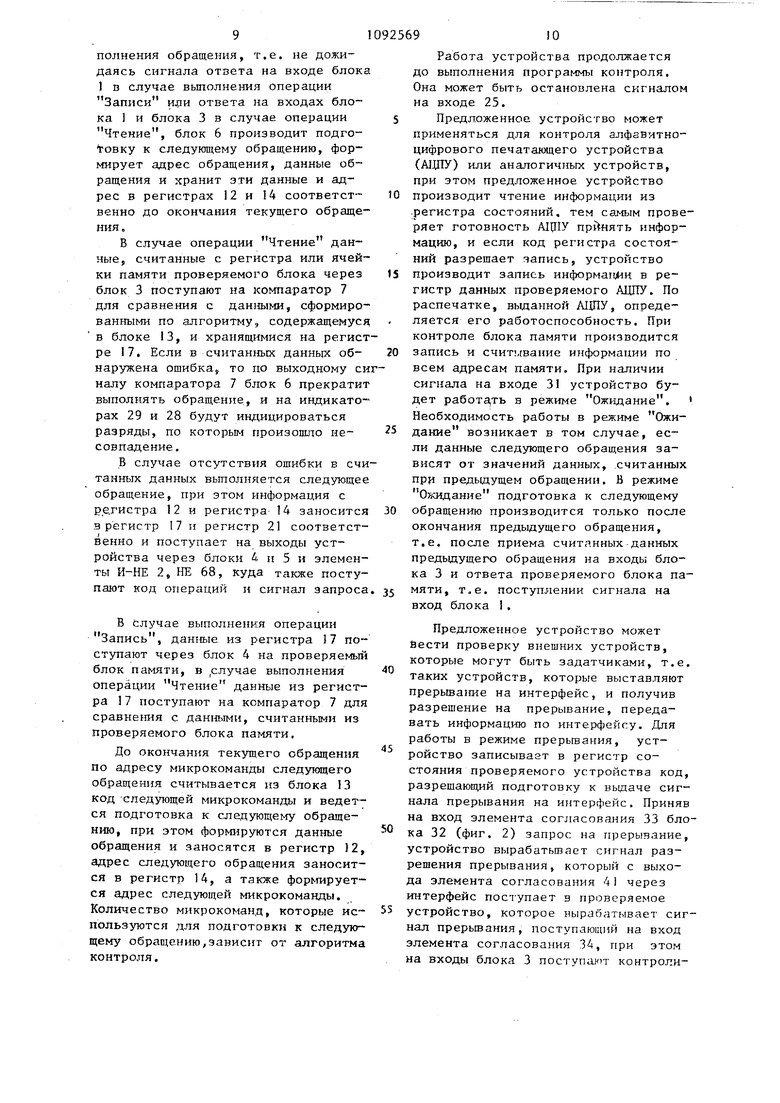

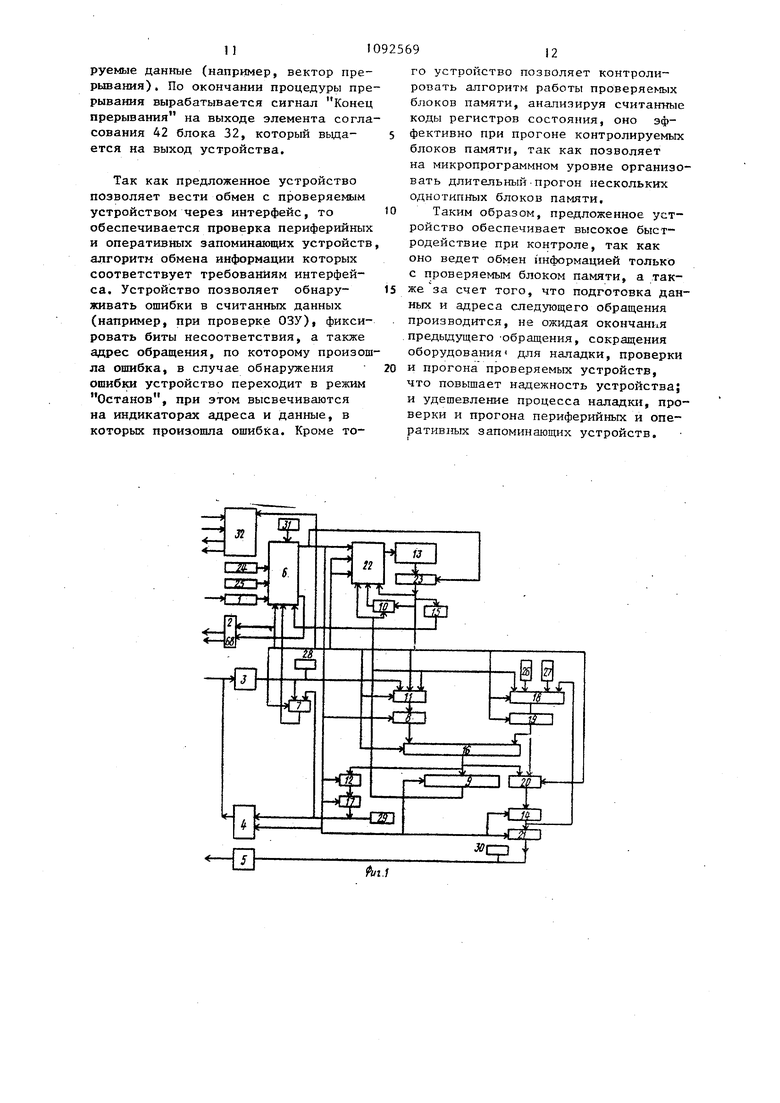

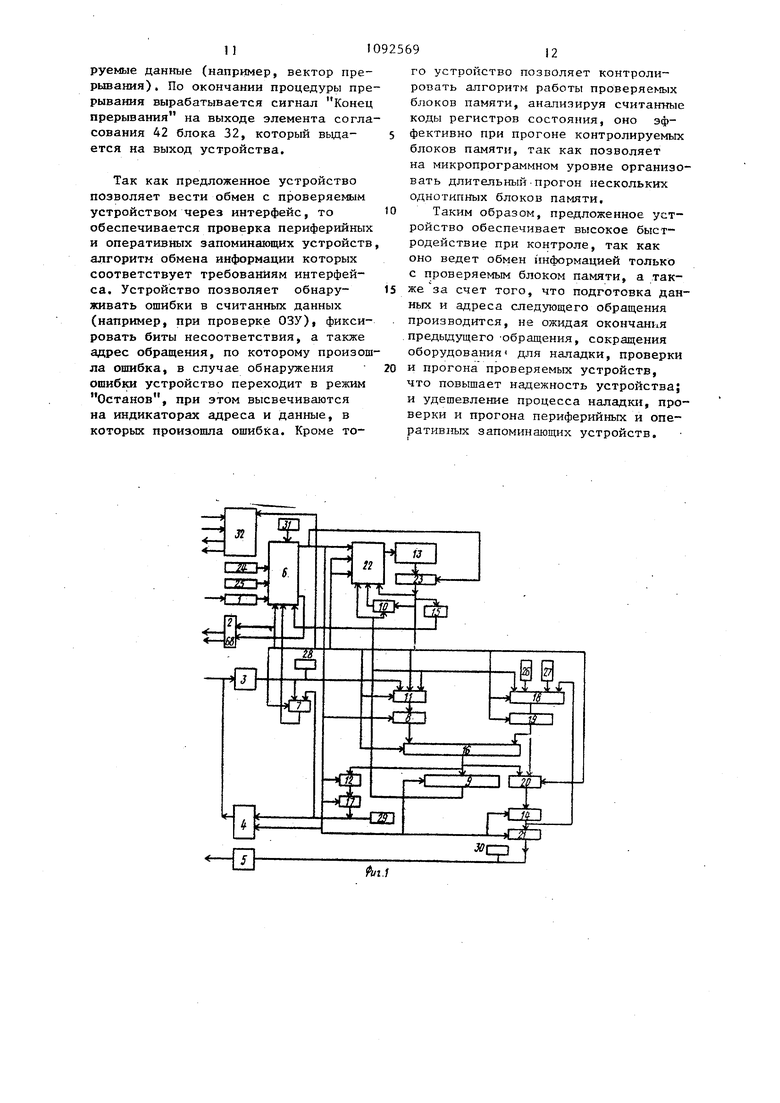

Недостатком известного устройстна является низкое быстродействие, так как необходимо из проверяемой памяти переслать код микропрограмм проверки в блок управления, и только после пересылки ведется контроль проверяемого устройства, за счет чего увеличивается время контроля, а также необходимо, чтобы часть памяти проверяемого устройства, в которой хранится микропрограмма проверки, была заведомо исправна, это затрудняет наладку и снижает достоверность контроля. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается те что в устройство для контроля блоков памяти, содержащее блок управле ния, один из входов которого подклю чен к выходу компаратора, регистры с первого по шестой, мультиплексоры арифметико-логический блок, первый элемент НЕ и первьп элемент И-НЕ, причем выходы первого мультиплексор подключены ко входам первого регист ра, выходы которого соединены с одним из входов арифметико-логического блока, выходы которого подключены ко входам второго и третьего регистров, и одним из входов второго мультиплексора, выходы которого, соединены с входами четвертого регистра, выходы второго регистра подключены к одним из входов первого мультиплексора, введены блок памяти микрокоманд, сумматор по модулю два, третий мультиплексор, накопитель, седьмой и восьмой регистры, дешифратор, блок перерывания, блок ввода данных, блок вывода данных, блок ввода управляю цих сигнало и блок вывода адреса, причем входы пятого регистра соединены с выходами третьего регистра, входы и выходы шестого регистра подключены соответственно к выходам четвертого регистра и ко входам блока вывода адреса, выходы седьмого регистра соединены с входами блока памяти микрокоманд, выходы которого подключены ко входам восьмого регистра одни из выходов которого соединены соответственно с одними из входов седьмого регистра, с одними из входов дешифратора, с входами сумматора по модулю два, с управляющими входами первого, второго и третьего мультиплексоров, накопителя, арифметико-логического блока и компаратора, с первым входом первого элемента И-НЕ и с одним из входов блок прерывания, другие входы седьмого регистра подключены соответственно к выходам дешифратора и к иыходам 694 второго регистра и другим входам дешифратора, одни из входов третьего мультиплексора соединены соответстBeiiiio с вь(ходами второго регистра и с выходами четвертого регистра, а выходы подключены ко входам накопителя, рыхоггы которого соединены с другими входами арифметико-логического блока и второго мт,льтиплексора5 другие входы блока управления подключены соответственно к выходам блока ввода управляющих сигналов, к другим выходам восьмого регистра и к выходу сумматора по модулю два, выходы блока управления соединены соответственно с входом первого элемента НЕ и вторым входом первого элемента И-ИЕ, с управляющими входами регистров и блока вывода данных, входы которого подключены к выходам пятого регистра, и одним из входов компаратора, другие входы которого соединены с выходами блока ввода данных и другими входами первого мультиплексора, выходы блока вывода адреса, входы блока ввода данных и выходы блока вывода данных являются соответственно адресныьш выходами и информационными входами и выходами устройства, входы пуска, останова и режима ожидания блока управления и другие входы третьего мультиплексора являются yпpaвляющIiMи входами устройства, входами и выходами прерывания которого являются другие входы и выходы блока прерывания, а выходами обращения - выходы первого элемента; НЕ и первого элемента Н-НЕ. Кроме того блок прерываний содержит триггеры, формирователи одиночных импульсов, второй элемент НЕ, элемент Н и элементь согласования, причем выход первого элемента согласования соединен с первым входом элемента И, выход которого подключен к счетному входу первого триггера, установочный вход которого соединен с выходом первого и входом второго формирователей одиночных импульсов, вькод второго элемента согласования подключен к, входу первого формирователя одиночных иьтульсов и входу второго элемента НЕ, выход которого соединен со счетным входом второго триггера, вход установки которого подключен к выходу второго формирователя одиночных импульсов, выходы первого и второго триггеров соединены соответственно с входами третьего и четвертого элементов согласования выходы которых являются выходами блока, одним из входов которого яв ляется второй вход элемента И, а Другими входами - входы первого и второго элементов согласования. На фиг. 1 представлена функциональная схема предложенного устройс ва; на фиг. 2 и 3 - функциональные схемы блока прерываний и блока управления соответственно. Предложенное устройство содержит (фиг, 1) блок 1 ввода управляющих сигналов, первый элемент И-НЕ 2, блок 3 ввода данных, блок 4 вывода данных, блок 5 вывода адреса, блок 6 управления, компаратор 7, первый 8 и второй 9 регистры, дешифратор 10, первый мультиплексор 11, третий регистр 12 Д.ПЯ хранения данных, блок 13 памяти микрокоманд, четвертый регистр 14 для хранения адреса сумматор 15 по модулю два, арифметико-логический блок 16, пятьй регистр 17 для буферного хранения дан ных, второй мультиплексор 18, накопитель 19, третий мультиплексор 20, шестой регистр 21 для буферного хранения адреса, седьмой регистр 22 для хранения адреса ьшкрокоманд восьмой регистр 23 для хранения микрокоманд, клавиши входов пуска 24 и останова 25 блока управления, управляющие входы 26 и 27 устройств . индикаторы 28-30, клавишу входа 31 режима ожидания блока управления и блок 32 прерывания. БЛОК прерываний содержит (фиг.2 первый 33 и второй 34 элементы согласования, элемент И 35, первый 36 и второй 37 триггеры, первый 38 и второй 39 формирователи одиночных импульсов, второй элемент НЕ 40, третий 41 и четвертый 42 элементы согласования. Блок управления содержит (фиг. 3 кварцевый генератор 43 импульсов, триггеры 44-53, генераторы 54 и 55 одиночных импульсов, элементы И-НЕ 56 и 57, элементы НЕ 58, элементы И 59-64 и элементы ИЛИ 65-67 первый элемент НЕ 68. Индикаторы 28-30 выполнены в виде светодиодов. Блок I и блок 3 реализованы на интегральных микросхемах ИКС К559 ИП2, блоки 4 и 5 - на ИМС К559 ИП1, регистр 22 - на К155 ЛРЗ, регистры 12, 17, 8, 14, регистры 21 и 23 - на ИМС К155 ТМ8. Мультиплексоры М и 18 реализованы на ИМС К155 КП2, мультиплексор 20 - на ИМС К155 ЛР1, арифметико-логический блок 16 - на имС К155 ШЗ, накопитель 19 - на ИМС KJ55 РУ2. Дешифратор 10 реализован на ИМС К153 КП1, сумматор 15 по схеме сложения по модулю два с сорока входами. Блок 13 памяти микрокоманд представляет собой блок постоянной памяти и реализован на ИМС К556 РТ4. Устройство для контроля блоков памяти работает следующим образом. В блок 13 (фиг. 1) зашиты тесты контроля проверяемого блока памяти. Устройство может работать в режиме записи информатдии в ячейки памяти или регистры проверяемого блока памяти- и в режиме чтения информации из ячейки памяти или регистра проверяемого блока памяти. При подаче логической единицы на вход 24 вырабатываются сиш :ронизирующие сигналы на выходах триггеров 50, 51, 44 и 48 (фиг. 3), на выходе генератора 55 вырабатывается сигнал, по которому тестовая информация из блока 13 заносится в регистр 23, на выходах которого выставляется код микрокоманд. Выходные сигналы регистра 23 яапяются управляющими сигналами для соответствукяцих блоков устройства, кроме того, все сигналы с выходов регистра 23 поступают на сумматор 15, который осуществляет контроль считанной информации из блока 13 по паритету. Сигналы условий перехода поступают из регистра 23 на один из входов дешифратора 10, которьй в зависимости от кода условий определяет, какой из битов регистра 9 определяет нулевой разряд адреса микрокоманды, тем самым меняется естественный порядок следования микрокоманд. Сигналы адреса кода микрокоманд с вьжодов регистра 23 поступают на входы регистра 22 и определяют код адреса микрокоманд, находящихся в блоке 13. Сигнал управления регистром 8 поступает на вход блока 6, где с учетом сигналов синхронизации вырабатывается на выходе элемента И 62 сигнал занесения в регистр 8, поступающий на управляющий вход регистра 12. 7 Сигнал управления регистром 9 с выхода регистра 23 поступает на входы блока 6, где с учетом сигналов синхронизации вырабатывается на выходе элемента И 59 сигнал занесения информации в регистр 9. Сигнал управления регистром 12 поступает из регистра 23 на вход блока 6, где с учетом сигналов синхронизации вырабатывается на выходе элемента И 60 сигнал занесения данных, поступаклдий на управляющий вход регистра 12, Сигнал управления регистром 14 поступает из регистра 23 на вход блока 6, где с учетом сигналов синхронизации вырабатывает ся на выходе элемента И 61 сигнал занесения адреса в регистр 14. Сигналы управления блоком 16 поступают из регистра 23 на управляющие входы блока 16 и определяют функции, вьшолняемые блоком 16 над входной информацией, поступающей на его входы. Сигналы управления накопителем 19 поступают из регистра 23 на управляющие входы накопителя 19 и определяют режим работы и адрес сло ва в накопителе 19, которьш предназначен для хранения промежуточных результатов вычислений. Сигналы управления компаратором 7 поступают из регистра 23 на управляющие вхо ды компаратора 7 и определяют выда чу результата операции сравнения, который поступает на вход блока 6, Сигналы управления мультиплексорам поступают из регистра 23 на управляющие входы соответственно мультиплексоров 11, 20 и 18 и определяют режим их работы. Сигнал операции Запрос поступает из регистра 23 на блок 6, в котором на выходе триггера 53 выра батывает сигнал Запрос, который поступает на,вход элемента НЕ 68 и с его выхода - в проверяемый бло памяти. Сигнал код операции поступает из регистра 23 на входы элемента И 2 и определяет код операции обращения к проверяемому блоку памяти, а акже поступает на вход блока 6, где с учетом наличия сигнала Запрос из регистра 23 вырабатьшается на выходе элемента И 64 сигнал, который поступает на управляюпий вход 9 блока 4 и разрешает выдачу данных на выход устройства. Сигнал .условий перехода поступает из регистра 23 на вход регистра 22 и определяет адрес следующей микрокоманды, при этом адрес следующей микрокоманды будет определяться адресом,.считанным из предыдущей микрокоманды, который поступает на другие входы регистра 22, а значение нулевого бита адреса микрокоманды (О J определяется дешифратором 10 и поступает с его выхода на вход регистра 22, Сигнал старших битов адреса микрокоманд формируются по схемам, аналогичным формирования первого бита адреса микрокоманды. Сигнал занесения информации из регистра 9 в регистр 22 поступает из регистра 23 на входы регистра 22 и определяет, что код адреса следующей микрокоманды определяется значениями битов регистра 9. Сигналы кода константы из регистра 23 поступают на входы мультиплексора 11, Код константы используется при формиро ании адреса следующей микрокоманды, данных на запись, адреса обращения. Сигнал микрооперации прерьшания поступает на вход блока 32 и определяет выдачу сигнала Разрешение прерывания на выходы прерывания устройства, а также поступает на входы блока 6 и определяет работу устройства в режиме прерывания. Блок 6 вырабатывает сигнал занесения адреса й кpoкoмaнд на выходе триггера 48 и на выходе генератора 54 - сигнал занесения данных и адреса в регистры 17 и 21, которые поступают соответственно на входы регистров 22, 17 и 21, По коду константы, поступанядему из регистра 23, сигналам с входов 26 и 27.и в соответствии с заданным алгоритмом блок 16 формирует адрес обращения, который поступает через регистр 14 на регистр 21, и формирует данные обращения, которые поступают через регистр 12 в регистр 17; данные обращения и адрес обращения поступают с регистров 17 и 21 на блок 4 и блок 5 соответственно, и с их выходов - в проверяемый блок амяти, причем данные передаются только при выполнении операции Запись, Не дожидаясь окончания выполнения обращения, т.е. не дожидаясь сигнала ответа на входе блока 1 в случае выполнения операции Записи вди ответа на входах блока и блока 3 в случае операции Чтение, блок 6 производит подгоговку к следующему обращению, формирует адрес обращения, данные обращения и хранит эти данные и адрес в регистрах 12 и 14 соответственно до окончания т(2кущего обращения , В случае операции Чтение данные, считанные с регистра или ячейки памяти проверяемого блока через блок 3 поступают на компаратор 7 для сравнения с , сформированными по алгоритму, содержащемуся в блоке 13, и хранящимися на регист ре 7. Если в считан1й х данньрс обнаружена ошибка, то по выходному си налу компаратора 7 блок 6 прекратит выполнять обращение, и на индикаторах 29 и 28 будут индицироваться разряды, по которым произошло несовпадение, В случае отсутствия ошибки в счи танных данных вьтолняется следующее обращение, при этом информация с .гистра 12 и регистра 14 заносится 3 регистр 17 и регистр 21 соответственно и поступает на выходы устройства через блоки 4 и 5 и элементы И-НЕ 2, НЕ 68, куда также поступают код операций и сигнал запроса В случае выполнения операции Запись, данные из регистра 17 поступают через блок 4 на проверяемьш блок памяти, в случае выполнения операции Чтение данные из регистра 17 поступают на компаратор 7 для сравнения с данными, считанными из проверяемого блока памяти, До окончания текущего обращения по адресу микрокоманды следующего обращения считывается из блока 13 код следующей микрокоманды и ведется подготовка к следующему обращению, при этом формируются данные обращения и заносятся в регистр 12, адрес следующего обращения заносится в регистр 14, а также форьгаруется адрес следующей микрокоманды. Количество микрокоманд, которые используются для подготовки к следующему обрап1ению,зависит от алгоритма контроля. 1 910 Работа устройства продолжается до выполнения программы контроля. Она может быть остановлена сигналом на входе 25. Предложенное устройство может применяться для контроля алфавитноцифрового печатакяцего устройства (А1Д1У) или аналогичных устройств, при этом предложенное устройство производит чтение информации из .регистра состояний, тем самым проверяет готовность АЦПУ принять информацию, и если код регистра состояний разрешает запись, устройство производит запись информа11 1и в регистр данных проверяемого АЦПУ. По распечатке, выданной АЦПУ, определяется его работоспособность. При контроле блока памяти производится запись и считывание информации по всем адресам памяти. При наличии сигнала на входе 31 устройство будет работа|Ть в режиме Ожидание. Необходимость работы в режиме Ожидание возникает в том случае, если данные следующего обращения зависят от значений данных, .считанных при предыдущем обращении. В режиме Ожидание подготовка к следующему обращению производится только после окончания предыдущего обращения, т.е. после приема считанных данных предыдущего обращения на входы блока 3 и ответа проверяемого блока памяти, т.е. поступлении сигнала на вход блока 1. Предложенное устройство может йести проверку внешних устройств, которые могут быть задатчиками, т.е. таких устройств, которые выставляют прерьша1ше на интерфейс, и получив разрешение на прерывание, передавать информацию по интерфейсу. Для работы в режиме прерьшания, устройство записывает в регистр состояния проверяемого устройства код, разрешающий подготовку к выдаче сигнала прерывания на интерфейс. Приняв на вход элемента согласования 33 блока 32 (фиг. 2) запрос на прерывание, устройство вырабатьшает сигнал разрешения прерьшания, который с выхода элемента согласования 41 через интерфейс поступает g проверяемое устройство, которое вырабатывает сигнал прерьшания, поступающий на вход элемента согласования 34, при этом на входы блока 3 поступали- контроляруемые данные (например, вектор прерьшания). По окончании процедуры пре рывания вырабатывается сигнал Конец прерывания на выходе элемента согла сования 42 блока 32, который выдается на выход устройства. Так как предложенное устройство позволяет вести обмен с проверяемым устройством через интерфейс, то обеспечивается проверка периферийных и оперативных запоминающих устройств алгоритм обмена информации которых соответствует требованиям интерфейса. Устройство позволяет обнаруживать ошибки в считанных данных (например, при проверке ОЗУ), фиксировать биты несоответствия, а также адрес обращения, по которому произош ла ошибка, в случае обнаружения ошибки устройство переходит в режим Останов, при этом высвечиваются адреса и данные, в на индикаторах которых произошла ошибка. Кроме того устройство позволяет контролировать алгоритм работы проверяемых блоков памяти, анализируя считанные коды регистров состояния, оно эффективно при прогоне контролируемых блоков памяти, так как позволяет на микропрограммном уровне организовать длительный-прогон нескольких однотипных блоков памяти. Таким образом, предложенное устройство обеспечивает высокое быстродействие при контроле, так как оно ведет обмен информацией только с проверяемым блоком памяти, а такжеза счет того, что подготовка данных и адреса следующего обращения производится, не ожидая окончанья предыдущего Обращения, сокращения оборудования для наладки, проверки и прогона проверяемых устройств, что повышает надежность устройства; и удешевление процесса наладки, проверки и прогона периферийных и оператив1а,гх запоминающих устройств.

3

fa г г

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| РЕЛЕ | 1924 |

|

SU1050A1 |

| Под ред | |||

| A.M | |||

| Ларионова, М., Статистика, 1976, с | |||

| СЧЕТНЫЙ ДИСК ДЛЯ РАСЧЕТА СОСТАВНЫХ ЧАСТЕЙ ПИЩИ | 1919 |

|

SU284A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля памяти | 1979 |

|

SU769641A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-05-15—Публикация

1983-02-11—Подача