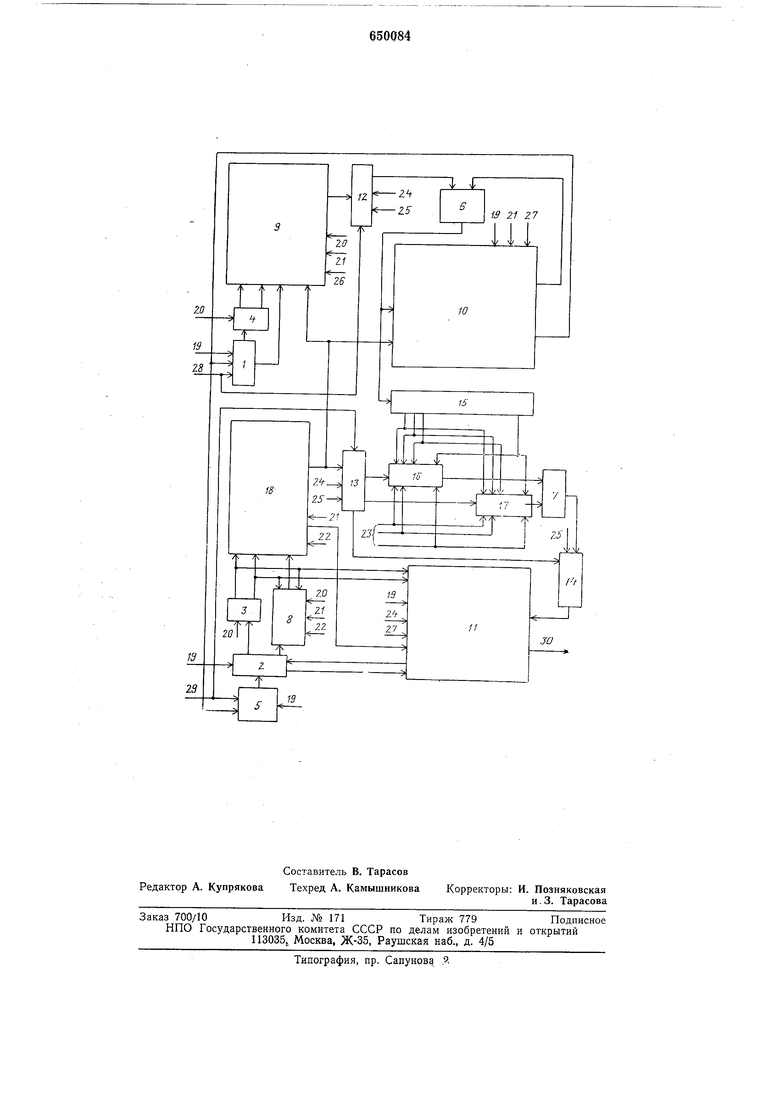

К недостаткам известного цифрового интегратора следует отнести уменьшение скорости вычисления за счет затрат определенного времени на обработку разрядов, заведомо равных нулю, а также на дополнительную операцию нормализации мантисс входных приращений, кроме того, снижается быстродействие из-за того, что все операции в цифровом интеграторе разнесены во времени. Целью изобретения является повышение быстродействия интегратора. Цель достигается тем, что в интегратор введены второй и третий преобразователи кода, два коммутатора, распределительный регистр и блок управления, причем первый и второй входы блока управления соединены с первым и вторым выходами второго .блока анализа знака, третий вход блока управления подключен к выходу блока элементов задержки, выход блока управления соединен с третьим входом блока сдвига кода, вторым входом блока нормализации мантисс и первым входом второго преобразователя кодов, второй вход которого подключен к второму входу второго сумматора, первый и второй выходы второго преобразователя кодов соединены соответственно с управляющими входами первого и второго коммутаторов, группа входов которых подключена к соответствующей группе выходов распределительного регистра, а выходы обоих коммутаторов соединены соответственно с первым и вторым входами третьего сумматора, третий выход второго преобразователя кодов соединен со вторым входом первого преобразователя кодов, выход блока сдвига кода соединен с первым входом третьего преобразователя кодов, второй вход которого соединен со вторым входом первого блока вычитания, а выход подключен к второму входу первого сумматора, выход которого соединен со входом распределительного регистра. На чертеже представлена блок-схема цифрового интегратора, содержащая блоки 1, 2 вычитания, блоки 3, 4 анализа знака, сумматоры 5-7, блок 8 элементов задержки, блок 9 сдвига кода, блок 10 нормализации мантисс, блок 11 квантования, преобразователи 12-14, распределительный регистр 15, коммутаторы 16, 17, блок 18 управления, управляющие входы 19-27, информационные входы 28, 29, информационный выход 30. Алгоритм работы данного цифрового интегратора имеет вид: ПН- i-YKl 2 УК 11-1} . О, если Пгд-,,,) -Пдг/гг К; г,,Щ,„,,г, - /fCHi) ,) X -i)-(+J) +м,. ,-Mлг,,,,.(.I); ;г(ги)- гЛМд%,,,; ,...,/); /e(l,2,..../и); ,,,,,,,,J,; Ук(1-1) (г+1)(;,1), (/-1) + ,)-П„.,0; osKi ± ДПдг,(г+1), если Пгуг(,1) + хк(1м) 0; () если n,(,j-f+1ПдА:АГ(м 1) - osKt 0; - osKi ± ДПдг..,,, IV- log,, т, Д«лг/с(,,, ащений подынтегральной функной интегрирования и интегственно, состоящие из старединичных разрядов и знаков К1 - весовые единичные разряды приращения подынтегральной функции на i-M шаге интегрирования в -м интеграторе; i) -порядок нормализованной мантиссы подынтегральной функции на (t-1)-м шаге интегрирования в й-м интеграторе; К-число, ограничивающее сверху разность порядков мантиссы Подынтегральной функции приращения Подынтегральной функции;I -мантисса подынтегральной функции на /-М шаге интегрирования в й-м интеграторе;) - нормализованная мантисса подынтегральной функции на (t-1)-м шаге интегрирования в /fe-м интеграторе; й -суммарное приращение подынтегральной функции в k-u интеграторе на J-M шаге интегрирования приведенной к младшему разряду подынтегральной функции Ny - число разрядов мантиссы подынтегральной функции;±Аrij / j-приращение порядка подынтегральной функции на i-M шаге интегрирования в k-M интеграторе, полученное в результате нормализации мантиссы подынтегральной функции Мк,; ,{,, J, - мантисса приращения интеграла на (t+l)-M щаге интегрирования в fe-м интеграторе;порядок приращения инii&Zf((i I) теграла на (i-|-l)-M шаге интегрирования в fe-M интеграторе; 1 A%(i4 I) порядокприращения переменной интегрирования на (i+l)-M шаге интегрирования в k-M интеграторе;niZ;f(,.i) нормализованная мантисса |прирашения интеграла на (t+l)-M шаге интегрирования в -м интеграторе;( 1) -приращение порядка интеграла, полученное в результате нормализации мантиссы приращения интеграла Мдг/г(г-г1)на (i+l)-M шаге интегрирования в k-M интеграторе; - порядок остатка приращения интеграла на i-м niare интегрирования в fe-м интеграторе;Pzi --Is-функция расчленения, выделяющая группу старщих /-разрядов в приращении интеграла; Г; - порядок выделенного /-го разряда в приращении; - мантисса остатка приращения интеграла , на (t-|-l)-M шаге интегрирования в й-м интеграторе;pV.... функция расчленения, выделяющая остаток приращения от -Л до (Гт- -1)-го разряда включительно; . . . . . . -N -порядок младшего разряда приращения интеграла;г„ -порядок младщего разряда выделенного приращения. Устройство работает следующим образом. На управляющий вход 19 блоков 1, 2, 10, 11 и сумматора 5 поступает из устройства управления потенциал выделения порядков приращений. На информационный вход 28 блока 1 поступает порядок приращения подынтегральной функции Ylyhi, а на вход 29 сумматора 5 - порядок приращения переменной интегрирования .ii) При этом в блоке 1 вычитаются порядки () - в сумматоре 5 суммируются порядки 1ПК/Г()4- ПдХ;(р,), в блоке 2 вычитаются порядки УК(1-1) + Пдхд.(г I) - По,г,|. в момент поступления знакового разряда порядка приращения из устройства управления подается сигнал выделения знака порядка. По этому сигналу перезаписываются из блока 2 в блок 8 вычисленная разность порядков Ук(1-1) + - 1а из блока 1 в блок 9 - разность 1Пк,г(,„ - , в блоке 4 анализируются знаки разности ПОРЯДКОВ УК(1-1) + I) - . По окончании операции выделения прирап1,ення и анализа знаковых разрядов из устройства управления поступает на вход 25 блоков 12. 13 сигнал выделения знакового разряда приращения. По этому сигналу знаковые разряды приращений подынтегральной функции и переменной интегрирования записываются в блоках 12, 13. По окончании выделения знаков приращений из устройства управления подается потенциал выделения приращения на вход 24 блоков 12, 13. По потенциалу выделения приращения в блоке 12 формируется код приращения подынтегральной функции. В блоке. 13 формируется код приращения переменной интегрирования )Рассмотрим процесс выравнивания порядков в цифровом Интеграторе. Управление операцией выравнивания Порядков осуществляется блоками 4, 3.(в этих блоках вырабатываются сигналы, определяющие направление сдвига.) и блоками 8, 9, 18, в которых вырабатываются сигналы, опред

ляющие, на сколько тактов нужно сдвинуть код числа. Так, если знак разности порядков

ПгА-() + (/41) ПМА-;

полол ительный, то по сигналу, поступающему из блока 3, и потенциалу работы, поступающему из устройства управления на вход 22 блока 18, в блоке 18 управления вырабатывается сигнал управления блоком И. По этому сигналу осуществляется Продвижение мантиссы остатка Mosk(-i) младшими разрядами влеред в блоке 11 и суммирование ее с нулевымИ разрядами до поступления мантиссы приращения интеграла. А через

2Пул-(,) + () -

тактов выдается блоком 8 сигнал пуска блока 18. И из блоКа 18 управления поступает Потенциал на управляющие входы блока 10, блока 9, .преобразователя 13. По этому потенциалу запускаются блок 17 и блок 9, если знак разности -порядков

((г-1) - Плгд-Л

отрицательный. При этом блоком 4 совместно с блоком 9 вырабатывается сигнал, обеспечивающий сдвиг кода приращения влево в блоке 12 относительно мантиссы

подынтегральной функци-и ,, на

2%/-)

К1

разрядов. А если разность порядков

Гк(1-1) - ПА/Л-Л

положительная, то пуск блока 9 осуществляется ПО предварительному потенциалу работы, поступающему из устройства управления на вход 26. В этом случае выравниваются порядки подынтегральной функции и ее приращений до начала операции суммирования мантиссы подынтегральной функции с ее приращениями, причем, если разность порядков находится в пределах

А Пгй-() - .

При этом код приращения сдвигается вправо на

2%.-,) - « разрядов относительно мантиссы

Ука-1) А если разность порядков

nxjqi i) -Плку г А.

то блок 9 выдает сигнал запрета в блок 12, и последним выдается нулевое приращение. Из выхода блока 12 код приращения в виде

п - YKI 2 У/(1-1) .т,

поступает на один вход сумматора 6, а на второй - мантисса

)

ИЗ выхода блока 10. В сумматоре б вычисляется новое значение мантиссы подынтегральной функции . Вычисленная

мантисса перезаписывается в блок 10 и одповременно поступает в регистр 15. В блоке 13 формируются весовые единичные разряды приращения переменной интегрирования. В свою очередь весовые единичные разряды поступают на входы коммутаторов 17. Последние онращиваются специальными сигналамИ, поступающими из устройства управления на входы 23. Причем первый сигнал начинается со второго такта после поступления сигнала из выхода блока 18 управления, а каждый последующий начинается на такт позже. Коммутаторы 16, 17 подключают соответствующие выходные шины ячеек регистра 15 к входам сумматора 7. Через коммутаторы 16, 17 информация из выхода регистра 15 поступает в виде частичных произведений на входы сумматора 7. В сумматоре 7 вычисляется мантисса приращения интеграла. Результат из выхода сумматора 7 поступает

младшими разрядами вперед через преобразователь 14 на информационный вход блока 11 с задержкой на

/.(.-1)()- тактов относительно мантиссы остатка

osf,r

что эквивалентно умножению мантиссы приращения интеграла на величину п,у„,, ., - п„

))

oSffi

В преобразователе 14 произведению присваивается знак приращения переменной интегрирования. Таким образом, с выхода преобразователя 14 информация поступает на вход блока 11 в виде вычисленной мантиссы приращения интеграла

Мк,,.А«.х,.,) блоке 11 вычисленная мантисса Интеграла суммируется со старшими разрядами мантиссы остатка М.

По окончании операции интегрирования снимается потенциал работы, и из устройства управления поступает потенциал нормализации на вход 27 блока И и блока 10. При этом в блоке 10 нормализуется мантИСса подынтегральной функции Мку,- и формируется новый порядок

Пк/г() ± Ук1

а в блоке II нормализуется мантисса при

ращения интеграла ,,

и формируется новый порядок приращения интеграла

Ук(1-.1)(1+1)(1+1г если Пк/г(,1) + Пдху(,1) - -По.,,0; Пдгу(г+1) j ± ) если

Пку() + /f(41) w 0;

ДПдг;,(;+1), если ) +

+ ПАХЛ:(/. I) Ki ОА по Потенциалу выделения приращения, поступающему по входу 24 из устройства управления, формируется в блоке 11 Переменное приращение интеграла

Д/гадг(г+1) ) 1

путем выделения группы / старших разрядов из вычисленной мантиссы -приращения интеграла, при этом выделяется остаток интеграла в виде

Mo.(,,,),,J

Одновременно в -блоке И формируется порядок остатка

(; + 1) - По5д-; + (ij I) тИспользование предлагаемого цифрового интегратора дает возможность увеличить скорость вычисления по сравнению с существующими цифровыми интеграторами.

Формула изобретения

Цифровой интегратор, содержащий два блока вычитания, два блока анализа знака, три сумматора, блок сдвига -кода, блок нормализации мантисс, блок элементов задержки, блок квантования и первый преобразователь кода, причем лервый выход -первого блока вычитания через первый блок анализа знака соединен с первым и вторым входами блока сдвига кода, третий вход которого подключен к второму выходу первого блока вычитания, выход первого сумматора соединен с первым входом блока нормализации мантисс, первый выход которого подключ.ен к первому входу первого сумматора, а второй выход блока нормализации мантисс соединен с первым входом второго сумматора, выход которого подключен к первому входу второго блока вычитания, второй вход которого соединен с выходом блока квантования, первый выход второго блока вычитания через второй блок анализа знака соединен с первым и вторым входами блока элементов задержки и блока квантования, третий вход которого подключен к второму выходу второго блока вычитания, третий выход которого -соединен с третьим входом блока элементов задержки, четвертый вход блока квантования соеди-нен с выходом первого преобразователя кода, первый вход которого подключен к выходу третьего сумматора, отличающийся тем, что, с целью повышения быстродействия, в него введены второй и третий прео-бразователи кода, два коммутатора, распределительный регистр и блок управления, -причем первый и второй входы блока управления соединены с первым И вторым выходами второго блока анализа знака, третий вход блока управления подключен к выходу блока элементов задержки, выход блока управления соединен с третьим входом блока сдвига кода, вторым входом блока нормализации мантисс и первым входом второго преобразователя кодов, второй вход которого

подключен к второму входу второго сумматора, первый и второй выходы второго преобразователя кодов соединены соответственно с управляющими входами первого и второго коммутаторов, группа входов которых подключена к соответствующей группе выходов распределительного регистра, а выходы обоих коммутаторов соединены соответственно с первым и вторым входами третьего сумматора, третий

выход второго преобразователя кодов соединен со вторым входом первого -преобразователя кодов, выход блока сдвига кода соединен с первым входом третьего -преобразователя кодов, второй вход которого

соединен со вторым входом первого блока вычитания, а выход подключен к второму входу первого сумматора, выход которого соединен со входом распределнтельпого регистра.

Источники информации,

принятые во внимание при экспертизе 1. Каляев В. А. Теория цифровых интегрирующих маши-н и структур. М., «Энергия, 1970, с. 355-362.

2. Авторское свидетельство СССР № 453711, кл. G 06J 1/02, 22.11.72.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор | 1975 |

|

SU661572A1 |

| Вычислительное устройство цифровой интегрирующей структуры | 1977 |

|

SU703840A1 |

| Цифровой интегратор | 1976 |

|

SU651371A1 |

| Цифровой интегратор для однородных цифровых интегрирующих структур (оцис) с плавающей запятой | 1973 |

|

SU510727A1 |

| Вычислительное устройство цифровой интегрирующей структуры | 1974 |

|

SU518781A1 |

| Цифровой интегратор с плавающей запятой | 1975 |

|

SU590774A2 |

| Интегрирующее устройство | 1990 |

|

SU1727122A1 |

| РЕШАЮЩИЙ БЛОК ДЛЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО | 1972 |

|

SU355631A1 |

| Устройство масштабирования цифрового дифференциального анализатора | 1983 |

|

SU1156069A1 |

| Интегроарифметическое устройство | 1990 |

|

SU1784975A1 |

Авторы

Даты

1979-02-28—Публикация

1975-03-25—Подача