00

о

СО

фиг.1

Изобретение относится к запоминаю- щим устройствам, в частности к оперативным запоминающим устройствам динамического типа, которые для сохра- нения записанной в них информации требуют периодического к ним обращения (восстановления или регенерации информации).

Целью изобретения является упро- щение устройства.

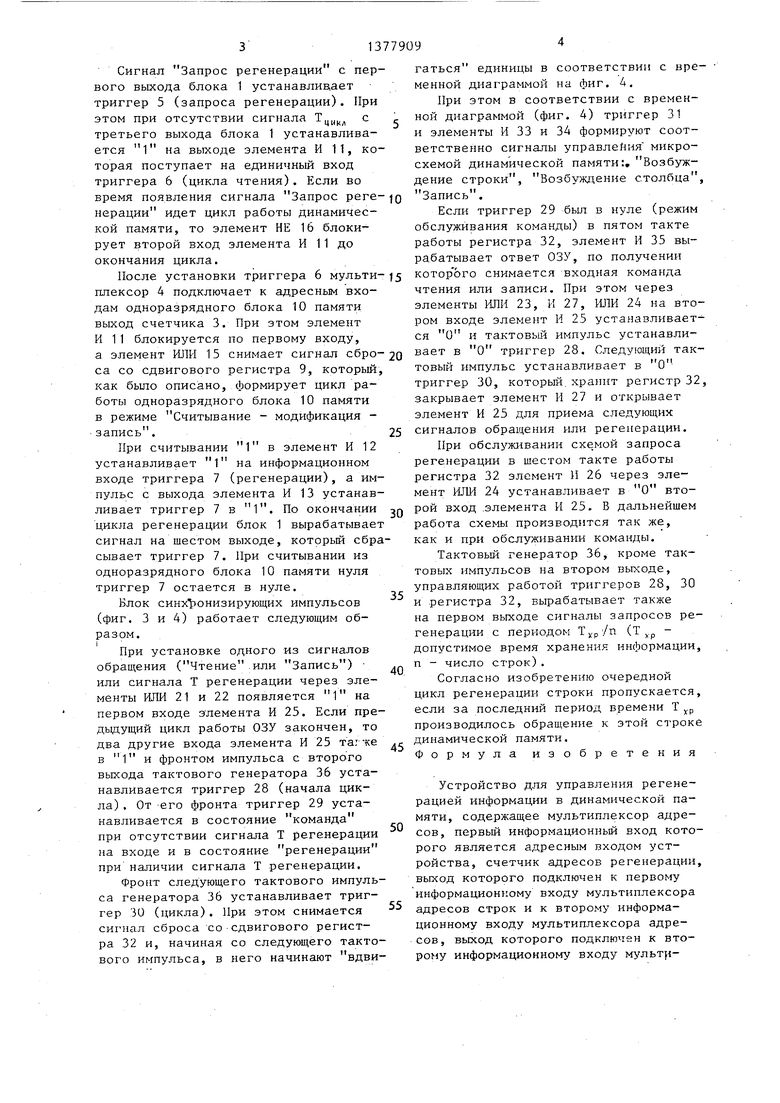

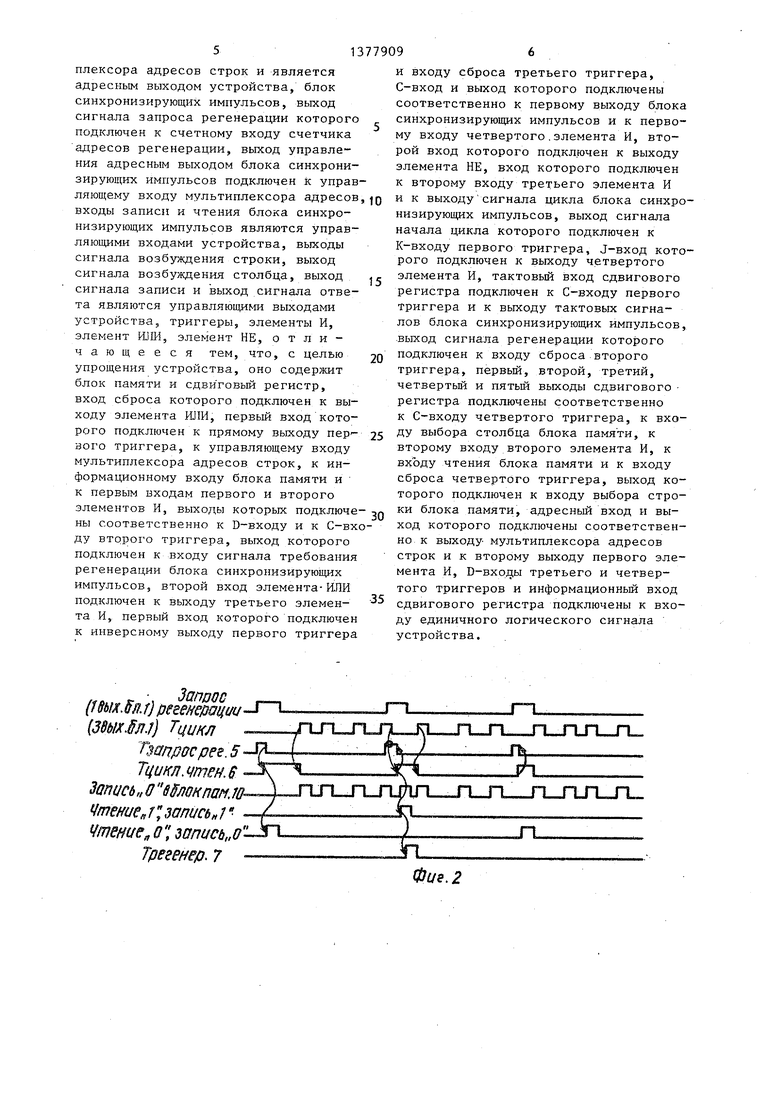

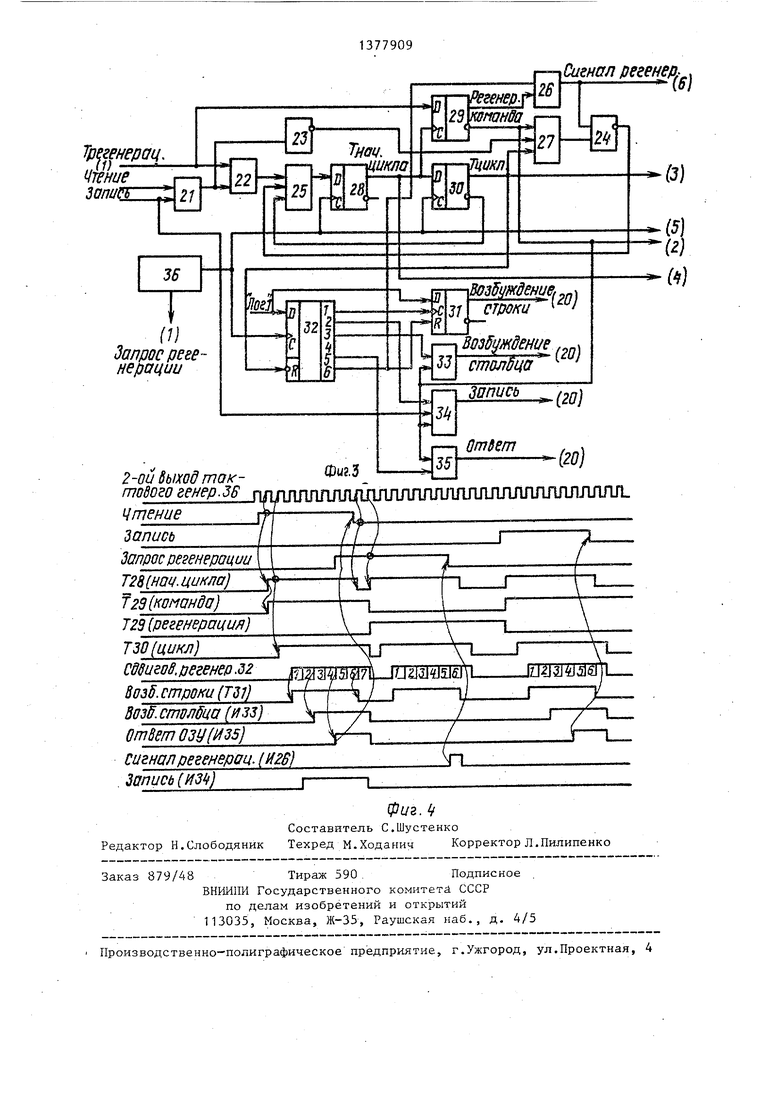

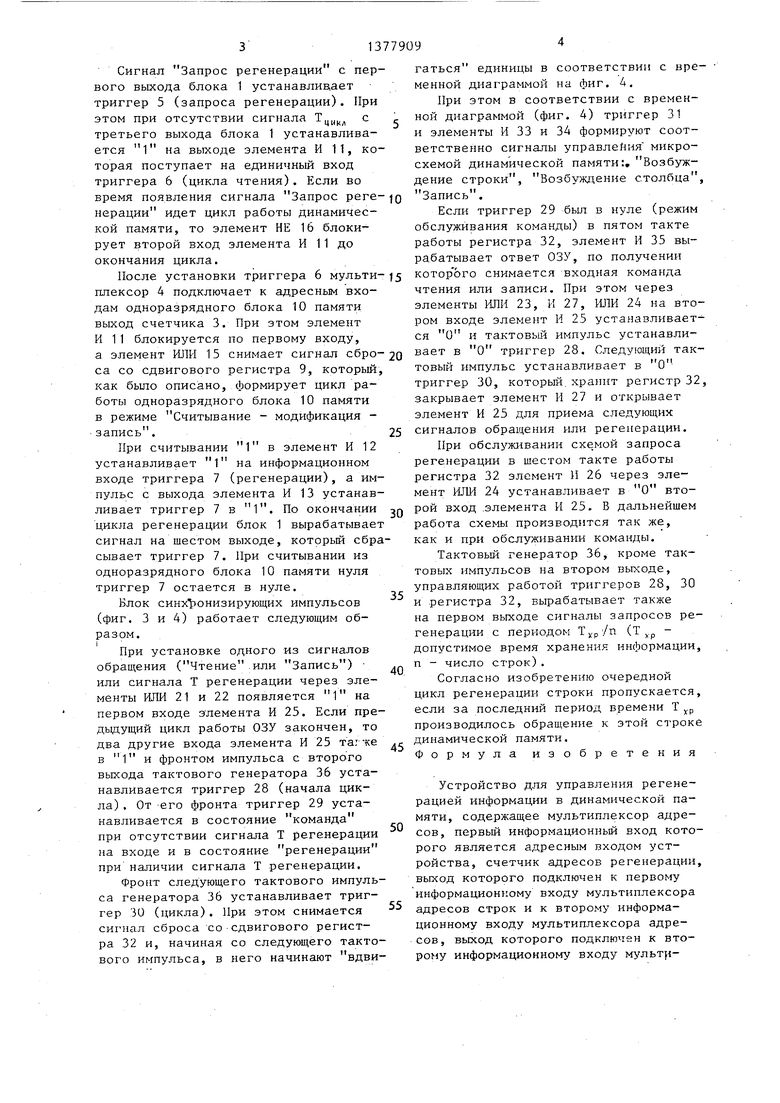

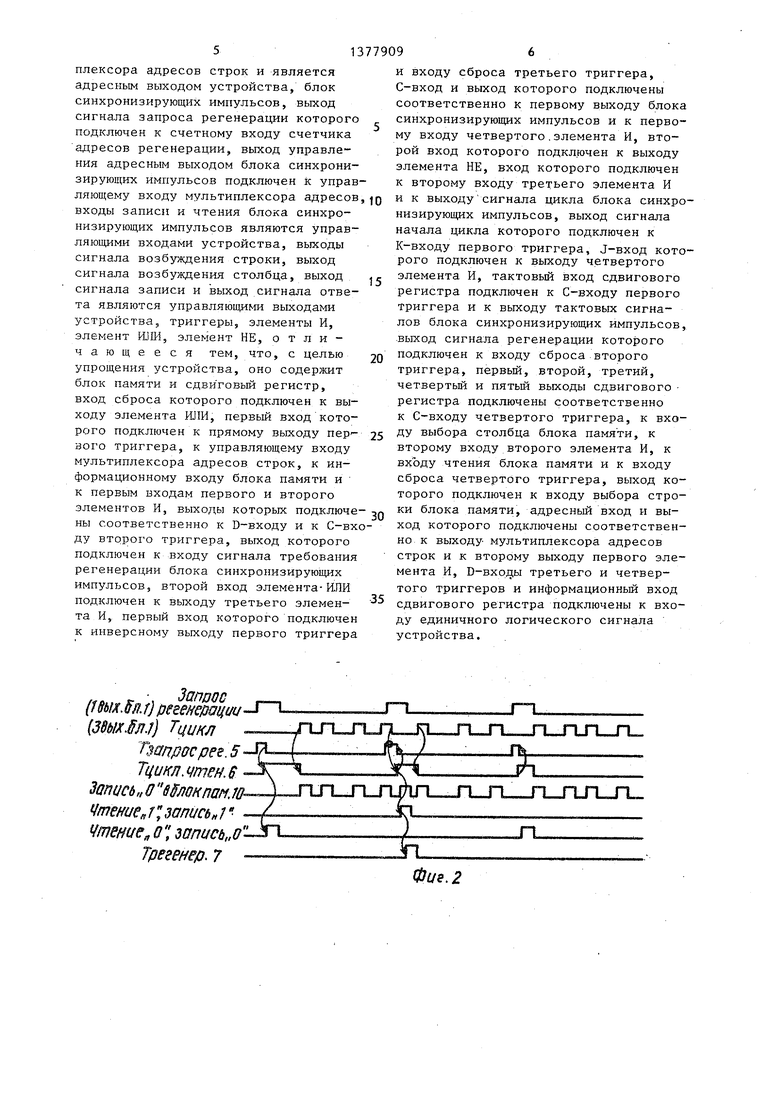

На фиг. 1 показана функциональная схема устройства регенерации информации в блоке динамической памяти; на фиг. 2 - временная диаграмма работы устройства; на фиг. 3 - функциональная схема блока синхронизирующих импульсов; на фиг. 4 - временная диаграмма работы блока синхронизирующих импульсов.

Устройство содержит блок 1 синхронизирующих импульсов, мультиплексор 2 адресов, счетчик 3 адресов регенерации, мультиплексор 4 адресов строк, триггер 5 (запроса регенерации), триггер 6 (цикла чтения), триггер 7 (регенерации), триггер 8 (выбора ряда) , сдвиговый регистр 9, блок 10 памяти (одноразрядный), элементы И 11- 14, элемент ИЛИ 15, элемент НЕ 16, адресные входы 17, адресные выходы 18 входные шины 19 режима команд, выходы 20 управления блоком памяти.

Блок 1 (фиг. 3) синхронизирующих импульсов содержит элементы ИЛИ 21-24 элементы И 25-27, триггер 28 (начала цикла)5 триггер 29 (регенерации), триггер 30 (цикла), триггер 31 (возбуждения строки), сдвиговый регистр 32, элементы И 33-35, тактовый гене- ратор 36.

Устройство.работает следующим образом.

При поступлении команд чтения или записи на входы 19 релсима блок 1 синхронизирующих импульсов вырабатывает на втором выходе сигнал, управляющий подключением к выходам мультиплексора 2 адресных выходов 18, а на выходах 20 формирует управляющие сигналы для работы динамической памяти. Пог- дробнее работа блока 1 рассмотрена ниже.

Мультиплексор 2 в зависимости от сигнала на его управляющем входе под ключает на выход первый или второй вход.

Во время выполнения команд чтени или записи блок 1 вырабатывает на

5 0

Q

5

третьем выходе сигнал на четвертом выходе - сигнал Т начала цикла. При этом триггер 6 (цикла чтения) установлен в О и сигнал через элемент И 14 и элемент ИЛИ 13 снимает сигнал сброса с входа сброса сдвигового регистра 9, который с каждым синхроимпульсом последовательно, начиная с первого разряда, начинает устанавливать 1 на каждом из своих выходов, которые используются для формирования цикла работы одноразрядного блока 14 памяти в режиме Считывание - модификация - запись.

После установки первого разряда сдвигового регистра 9 устанавливается триггер 8 (выбора строки), соединенный с входом выбора строки одноразрядного блока 10 памяти. После установки третьего разряда возбуждается вход выбора столбца, после установки пятого разряда - вход записи. При этом на информационном входе одноразрядного блока памяти - О, а на адресный вход мультиплексор 4 адреса строки коммутирует адресные выходы 18.

Таким образом, параллельно с рабочими обращениями к ячейкам динамической памяти записываются нули в строки одноразрядного блока 10 памяти, соответствующие строкам основной динамической памяти.

I

В устройстве используется способ

распределенной регенерации. Блок 1, как показано ниже, с периодом вырабатывает на первом выходе сигналы Запрос регенерации (ТХР - допустимое время хранения информации в динамической памяти, п - количество строк блока динамической памяти).

С приходом очередного сигнала Запрос регенерации добавляется 1 к счетчику 3 адресов регенерации, из одноразрядного блока 10 памяти читается содержимое ячейки с адресом, соответствующим счетчику 3 (адресу регенерации очередной строки), и затем в эту ячейку записывается 1. При этом, если из одноразрядного блока 10 памяти читается О, то значит, что за период к строке с таким адресом бьшо обращение и регенерации этой строки не требуется, если читается 1, то требуется регенерация строки..

Работа производится следующим образом (фиг. 1 и 2).

Сигнал Запрос регенерации с первого выхода блока 1 устанавливает триггер 5 (запроса регенерации). При этом при отсутствии сигнала третьего выхода блока 1 устанавливается 1 на выходе элемента И 11, которая поступает на единичный вход триггера 6 (цикла чтения). Если во

гаться единицы в соответствии с временной диаграммой на фиг. 4,

При этом Б соответствии с временной диаграммой (фиг. 4) триггер 31 и элементы И 33 и 34 формируют соответственно сигналы управления микросхемой динамической памяти:, Возбуждение строки, Возбуждение столбца.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| УСТРОЙСТВО ДЛЯ РЕГЕНЕРАЦИИ ИНФОРМАЦИИ ДИНАМИЧЕСКОЙ ПАМЯТИ | 1992 |

|

RU2049363C1 |

| Устройство для регенерации динамической памяти | 1980 |

|

SU943845A1 |

| Буферное запоминающее устройство | 1981 |

|

SU1022221A1 |

| Устройство для сопряжения ЭВМ с факсимильным аппаратом | 1988 |

|

SU1524060A1 |

| Устройство для преобразования малокадрового телевизионного стандарта | 1985 |

|

SU1256245A1 |

| Устройство для вывода информации | 1983 |

|

SU1094040A1 |

| Устройство управления взаимным доступом процессора многопроцессорной системы | 1989 |

|

SU1631548A1 |

| МНОГОМОДУЛЬНОЕ УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ТЕКСТОВОЙ И ГРАФИЧЕСКОЙ ИНФОРМАЦИИ | 1992 |

|

RU2037885C1 |

Изобретение относится к запоминающим устройствам, в частности к оперативным запоминающим устройствам динамического типа, к которым для сохранения записанной в них информации требуется периодически обращаться (восстанавливать или регенерировать информацию). Целью изобретения является упрощение устройства. Устройство содержит блок 1 синхронизации, мультиплексор 2 адресов, счет- чиК 3 адресов регенерации, мультиплексор 4 адресов строк, триггер 5 (запроса регенерации), триггер 6 (цикла чтения), триггер 7 регенерации, триггер 8 (выбора ряда), сдвиговый регистр 9, одноразрядный блок Ш памяти, элементы И 11-14, элемент ИJШ 15, элемент, НЕ 16, входы и выходы устройства. 4 ил. S . &

ремя появления сигнала Запрос реге- Q Запись

Если обслужив работы р рабатыва которЪго чтения и элементы ром вход ся О и

нерации идет цикл работы динамической памяти, то элемент НЕ 16 блокирует второй вход элемента И 11 до окончания цикла.

После установки триггера 6 мульти- 5 плексор 4 подключает к адресным входам одноразрядного блока 10 памяти выход счетчика 3. При этом элемент И 11 блокируется по первому входу.

Если триггер 29 был в нуле (режим обслуживания команды) в пятом такте работы регистра 32, элемент И 35 вырабатывает ответ ОЗУ, по получении которЪго снимается входная команда чтения или записи. При этом через элементы ИЛИ 23, И 27, Ш1И 24 на втором входе элемент И 25 устанавливается О и TaKTOBbUi импульс устанавлиа элемент ИЛИ 15 снимает сигнал сбро-20 вает в О триггер 28. Следующий так25

са со сдвигового регистра 9, который, как бьто описано, формирует цикл работы одноразрядного блока 10 памяти в режиме Считывание - модификация - - запись.,

При считывании 1 в элемент И 12 устанавливает 1 на информационном входе триггера 7 (регенерации), а импульс с выхода элемента И 13 устанавливает триггер 7 в 1. По окончании п цикла регенерации блок 1 вырабатывает сигнал на шестом выходе, который сбрасывает триггер 7. При считывании из одноразрядного блока 10 памяти нуля триггер 7 остается в нуле.

Блок синхТзонизирующих импульсов (фиг. 3 и 4) работает следующим образом. I

При установке одного из сигналов

обращения (Чтение или Запись) или сигнала Т регенерации через элементы ИЛИ 21 и 22 появляется 1 на первом входе элемента И 25. Если предыдущий цикл работы ОЗУ закончен, то два другие входа элемента И 25 та: же в 1 и фронтом импульса с второго выхода тактового генератора 36 устанавливается триггер 28 (начала цикла) . От его фронта триггер 29 устанавливается в состояние команда при отсутствии сигнала Т регенерации на входе и в состояние регенерации при наличии сигнала Т регенерации.

Фронт следующего тактового импульса генератора 36 устанавливает триггер 30 (цикла). При этом снимается сигнал сброса со сдвигового регистра 32 и, начиная со следующего такто35

40

45

50

55

товый импульс устанавливает в О триггер 30, которьш.хранит регистр 32, закрывает элемент И 27 и открывает элемент И 25 для приема следующих сигналов обращения или регенерации.

При обслуживании схемой запроса регенерации в шестом такте работы регистра 32 элемент И 26 через элемент ИЛИ 24 устанавливает в О второй вход .элемента И 25. В дальнейшем работа схемы производится так же, как и при обслуживании команды.

Тактовый генератор 36, кроме тактовых импульсов на втором выходе, управляющих работой триггеров 28, 30 и регистра 32, вырабатывает также на первом выходе сигналы запросов регенерации с периодом Тур /п (Т .р - допустимое время хранения информации, п - число строк).

Согласно изобретению очередной цикл регенерации строки пропускается, если за последний период времени Т ,р производилось обращение к этой строке динамической памяти. Формула изобретения

Устройство для управления регенерацией информации в динамической памяти, содержащее мультиплексор адресов, первый информационный вход которого является адресным входом устройства, счетчик адресов регенерации, выход которого подключен к первому информационному входу мультиплексора адресов строк и к второму информационному входу мультиплексора адресов, выход которого подключен к втового импульса, в него начинают вдви- рому информационному входу мyльт Запись

Если триггер 29 был в нуле (режим обслуживания команды) в пятом такте работы регистра 32, элемент И 35 вырабатывает ответ ОЗУ, по получении которЪго снимается входная команда чтения или записи. При этом через элементы ИЛИ 23, И 27, Ш1И 24 на втором входе элемент И 25 устанавливается О и TaKTOBbUi импульс устанавли0 вает в О триггер 28. Следующий так5

п 5

0

5

0

5

товый импульс устанавливает в О триггер 30, которьш.хранит регистр 32, закрывает элемент И 27 и открывает элемент И 25 для приема следующих сигналов обращения или регенерации.

При обслуживании схемой запроса регенерации в шестом такте работы регистра 32 элемент И 26 через элемент ИЛИ 24 устанавливает в О второй вход .элемента И 25. В дальнейшем работа схемы производится так же, как и при обслуживании команды.

Тактовый генератор 36, кроме тактовых импульсов на втором выходе, управляющих работой триггеров 28, 30 и регистра 32, вырабатывает также на первом выходе сигналы запросов регенерации с периодом Тур /п (Т .р - допустимое время хранения информации, п - число строк).

Согласно изобретению очередной цикл регенерации строки пропускается, если за последний период времени Т ,р производилось обращение к этой строке динамической памяти. Формула изобретения

Устройство для управления регенерацией информации в динамической памяти, содержащее мультиплексор адресов, первый информационный вход которого является адресным входом устройства, счетчик адресов регенерации, выход которого подключен к первому информационному входу мультиплексора адресов строк и к второму информационному входу мультиплексора адресов, выход которого подключен к втоплексора адресов строк и является адресным выходом устройства, блок синхронизирующих импульсов, выход сигнала запроса регенерации которого подключен к счетному входу счетчика адресов регенерации, выход управления адресным выходом блока синхронизирующих импульсов подключен к управляющему входу мультиплексора адресов,Q и к выходу сигнала цикла блока синхро15

20

входы записи и чтения блока синхронизирующих импульсов являются управляющими входами устройства, выходы сигнала возбуждения строки, выход сигнала возбуждения столбца, выход сигнала записи и выход сигнала ответа являются управляющими выходами устройства, триггеры, элементы И, элемент Ш1И, элемент НЕ, отличающееся тем, что, с целью упрощения устройства, оно содержит блок памяти и сдви говьш регистр, вход сброса которого подключен к выходу элемента ШШ, первый вход которого подключен к прямому выходу 25 зого триггера, к управляющему входу мультиплексора адресов строк, к информационному входу блока памяти и к первым входам первого и второго элементов И, выходы которых подключе- эп ны соответственно к D-входу и к С-вхо- ду второго триггера, выход которого подключен к входу сигнала требования регенерации блока синхронизирующих импульсов, второй вход элемента-ИПИ подключен к выходу третьего элемен- та И, первый вход которого подключен к инверсному выходу первого триггера

низирующих импульсов, выход сигнала начала цикла которого подключен к

К-входу первого триггера, J-вход которого подключен к выходу четвертого элемента И, тактовый вход сдвигового регистра подключен к С-входу первого триггера и к выходу тактовых сигналов блока синхронизирующих импульсов, выход сигнала регенерации которого подключен к входу сброса второго триггера, первьш, второй, третий, четвертьм и пятый выходы сдвигового регистра подключены соответственно к С-входу четвертого триггера, к входу выбора столбца блока памяти, к второму входу второго элемента И, к ВХОДУ чтения блока памяти и к входу сброса четвертого триггера, выход которого подключен к входу выбора строки блока памяти, адресный вход и выход которого подключены соответственно к выходу мультиплексора адресов строк и к второму выходу первого элемента И, D-BXOJJM третьего и четвертого триггеров и информационньш вход сдвигового регистра подключены к входу единичного логического сигнала устройства.

(Пык.п.} регенерации- (ЗШ.§л.1} Тцикл Tsanpocpes.s Тци(л.чтен.$ 8 локпам,10 Чтение„J1 запись -.-- Чтение „О, wnucb,, Трегенер, 7

79096

и входу сброса третьего триггера, С-вход и выход которого подключены соответственно к первому выходу блока синхронизирующих импульсов и к первому входу четвертого.элемента И, второй вход которого подключен к выходу элемента НЕ, вход которого подключен к второму входу третьего элемента И

5

0

5 эп

низирующих импульсов, выход сигнала начала цикла которого подключен к

К-входу первого триггера, J-вход которого подключен к выходу четвертого элемента И, тактовый вход сдвигового регистра подключен к С-входу первого триггера и к выходу тактовых сигналов блока синхронизирующих импульсов, выход сигнала регенерации которого подключен к входу сброса второго триггера, первьш, второй, третий, четвертьм и пятый выходы сдвигового регистра подключены соответственно к С-входу четвертого триггера, к входу выбора столбца блока памяти, к второму входу второго элемента И, к ВХОДУ чтения блока памяти и к входу сброса четвертого триггера, выход которого подключен к входу выбора строки блока памяти, адресный вход и выход которого подключены соответственно к выходу мультиплексора адресов строк и к второму выходу первого элемента И, D-BXOJJM третьего и четвертого триггеров и информационньш вход сдвигового регистра подключены к входу единичного логического сигнала устройства.

Фиг. 2

Трегенерац

Цтие 3ani/i

т

Запрос реее- нерации

Запрос регенерации Т2В(НО1.цикла)

723 (регенерация

ШЖШдар1ЫШ1ги 11№

J

L

L

сигнал 1зееенерац.К26

Запись jHSif)

J

Редактор Н.Слободяник

UZ.ff

Составитель С.Шустенко

Техред М.Ходанич Корректор Л.Пилипенко

Сигнал регенер- .

(0/

кшзшаа

J

L

S

г

| ТРУБЧАТОЕ СОЕДИНЕНИЕ ДЛЯ Л\ОНТАЖА РЕАКЦИОННЫХ ЕМКОСТЕЙ | 0 |

|

SU351389A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство регенерации информации для динамического блока матричной памяти | 1978 |

|

SU780035A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-02-28—Публикация

1986-06-10—Подача