(54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ВВОДОМ-ВЫВОДОМ

выход которого соединены с ссютветствующимй агодагли к выходом устройства, третъи выходы блоков синхронизации обмена соединены с соответствующими выходами устройства 2J.

8 известном устройстве оборудование модификации дескрипторов обмена дублируется Б каждой секции аппаратуры обслуживания данных, что снижает степень использования оборудования.

КрогйО того, система разработана для управления периферийными приборами но интерфейсу, отличающемуся от интерфейса.широко распространенных устройств фирмы JBM и ЕС ЭВМ, и не может работать с ними.

Целью изобретения является повышение коэффициента использования оборудования.

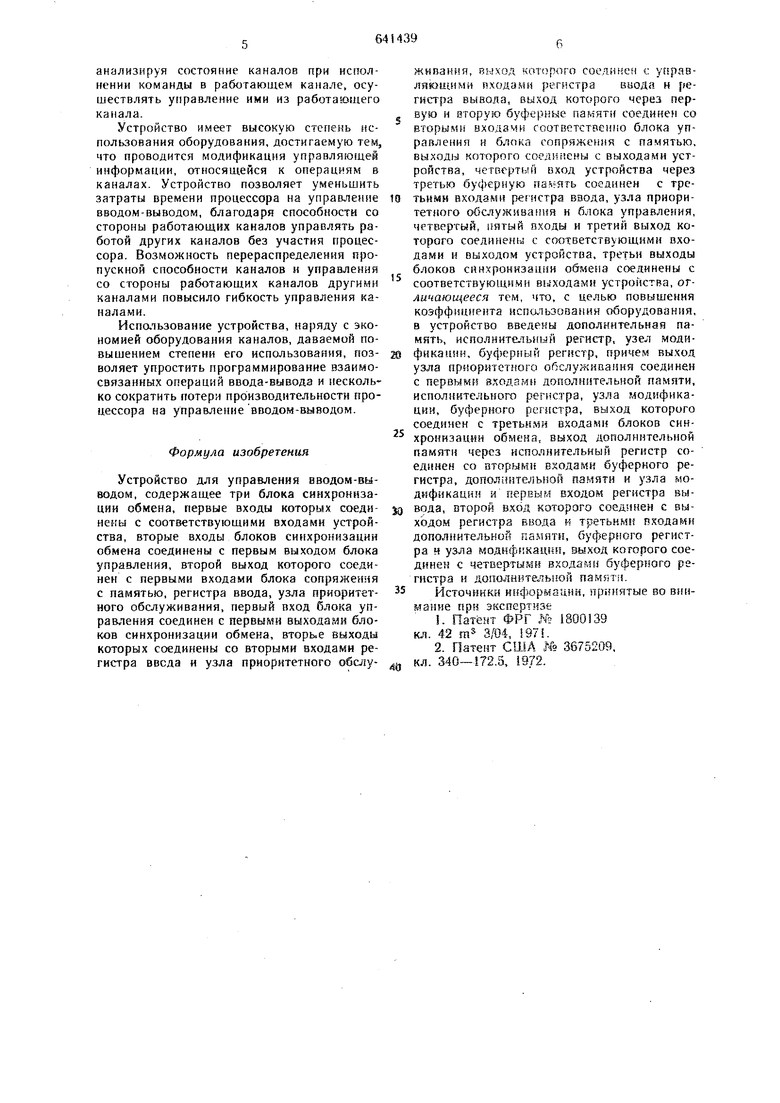

Поставленная цель достигается тем, что в устройство введены дополнительная память, исполнительный регистр, узел модификации, буферный регистр, причем выход узла приоритетного обслуживания соединен с первыми входами дополнительной памяти, исполнительного регистра, узла модификации, буферного регистра, выход которого соединен с третьими входами блоков синхронизации обмена выход дополнительной памяти через исполнительный регистр соединен со вторыми входами буферного регистра, дополнительной памяти и узла модификации и первым входом регистра вывода, второй вход которого соединен с выходом регистра ввода и третьими входами дополнительной памяти, буферного регистра и узла модификации, выход которого соединен с четвертыми входами буферного регистра и дополнительной памяти.

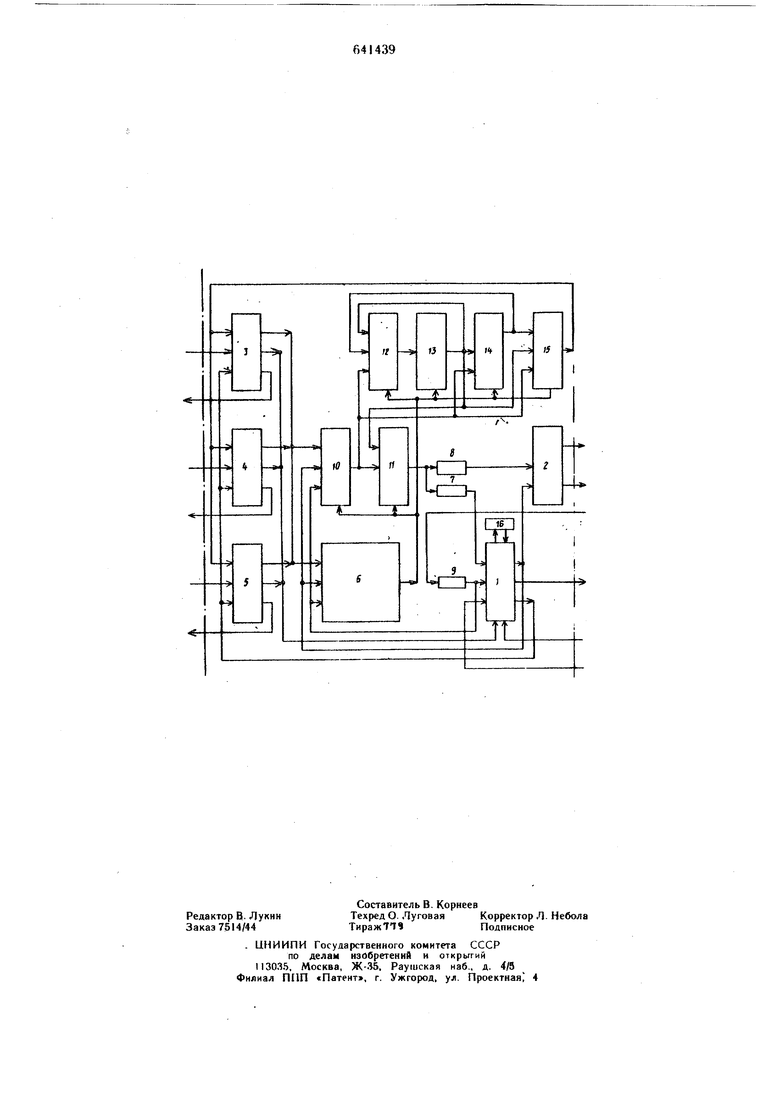

Блок-схема устройства приведена на чертеже, где приведены блок управления {, блок сопряжения с памятью 2, блоки синхронизации обмена 3 - 5, узел приоритетного обслуживания б, буферные блоки памяти 7-9, регистр ввода 0, регистр вывода И, дополнительная память 12, исполнительный регистр 13, узел модификации 14, буферный регистр 15, узел запуска каналов 16.

Работа устройства по обмену с внешними устройствами ведется автономно от процессора, первоначальный же запуск осуществляется процессором. Последующие запуски каналов производятся как процессором, так и уже работающими каналами. Работа канала заканчивается по окончании цепочки команд в программе канала или по команде «Останов из программы другого канала.

Запуск канала от процессора производится через нулевой канал, в который прдаимается адрес программы. Нулевой капал переводится блоком 1 в состояние «Работа и в нем, как и в любом работающем канале, ведется обработка команды, считанной по адресу программы. Отработка команды, например «Начать обмен, включает:

-де иифрацик) кода команды блоком 1; - анализ узлом 16 состояния канала,

указанного в команде, на возможность запуска (перевод его в состояние «Работа, обращение за первой командой в программе канала через блок 2);

-отработку программно-управляемого прерывания блоками 1, 2;

-анализ признака «Цепочка команд в обрабатываемой команде и переход, если предписано, к следующей команде работающего канала.

Считанные из ОЗУ команды управления периферийными устройствами пересылаются через регистры 10, 11 в блоки синхронизации обмена, например 3. Блок 3 связывается с периферийным устройством, считывает начальный байт состояния, пересылает через регистры 10, 11 и буферную память 7 в блок 1 для анализа. Если байт состояния равен нулю, то блок 1 разрещает блоку 3 продолжить команду. Блок 3 но запросам устройства набирает из байтов слово (при считывании с внешнего устройства - ВУ) и обращается с запросом в узел 6.5«Узел 6 обеспечивает обработку запросов блоков 3- 5 в соответствии с заданным приоритетом и позволяет увеличить пропускную способность высокоприоритетных каналов за счет снижения ее в менее приоритетных каналах, так чтобы не превышалась суммарная пропускная способность устройства. Принимая слова (при считывании с ВУ) от блока 3 на регистр 10, узел 6 обеспечивает: считывание на исполнительный регистр i3 из дополнительной памяти 2 информации, относящейся к данному каналу, модификацию количества байтов и адреса слова по ОЗУ в узле 14; обращение через регистр И, буферную память 8 и блок 2 в ОЗУ; запись модифицированной информации в дополнительную память 12; определение «Конца обмена. Все эти действия на регистрах и узлах 6, 10-15 производятся последовательно над информацией, относящейся ;; различным каналам. Отработав очередной запрос канала, узел 6 обеспечивает запоминание его информаци в дополнительной памяти 12 н освобождение регистров 10, il, 13, 15 и узла 14 для работы с запросами других каналов. Такая организация работы по обслуживанию запросов каналов позволяет повысить степень использования оборудования. Блок 3 по команде «Конец обмена выдает конечный байт состояния, который через регистры 10, Ни память 7 пересылается для анализа в блок i. Если в байте имеются указатели окончания, то узел 16 запускается на анализ признака «Цепочка команд в исполняемой команде н переход к следующей команде, если предписано. В «Цепочку команд могут входить как команды управления периферийными устройствами, так и команды управления каналами. Это позволяет узлу 16, анализируя состояние каналов при исполнении команды в работающем канале, осушествлять управление ими из работающего канала. Устройство имеет высокую степень использования оборудования, достигаемую тем, что проводится модификация управляющей информации, относящейся к операциям в каналах. Устройство позволяет уменьщить затраты времени процессора на управление вводом-выводом, благодаря способности со стороны работающих каналов управлять работой других каналов без участия процессора. Возможность перераспределения пропускной способности каналов и управления со стороны работающих каналов другими каналами повысило гибкость управления каналами. Испатьзование устройства, наряду с экономией оборудования каналов, даваемой повыщением степени его использования, позволяет упростить программирование взаимосвязанных операций ввода-вывода и несколько сократить потери производительности процессора на управление вводом-выводом. Формула изобретения Устройство для управления вводом-выводом, содержащее три блока синхронизации обмена, первые входы которых соедннеиы с соответствующими входами устройства, вторые входы блоков синхронизации обмена соединены с первым выходом блока управления, второй выход которого соединен с первыми входами блока сопряжения с памятью, регистра ввода, узла приоритетного обслуживания, первый вход блока управления соединен с первыми выходами блоков синхронизации обмена, вторые выходы которых соединены со вторыми входами регистра ввода и узла приоритетного обс/ уживания, выхо.д которого соединен с yfipaBляющими входами регистра ввода н регистра вывода, выход которого через первую н вторую буферные памяти соединен со вторыми входами соотЕгетствеино блока управления н блока сопряжения с памятью, выходы которого соедиг ены с выходами устройства, четвертый вход устройства через третью буферную соединен с третьими входами регистра ввода, узла приоритетного о{}служива иш и блока управления, четвертый, пятый входы и третий выход которого соединены с соответствующими входами и выходом устройства, третьи выходы блоков синхронизации обмена соединены с соответствующими выходами устройства, огличающееся тем, что, с целью повышения коэффициента испатьзоваиин оборудования, в устройство введены дополнительная память, исполнительный регистр, узел модификации, буферный регистр, причем выход узла приоритетного обслуживания соединен с первыми входами дополнительной памяти, исполнительного регистра, узла модификации, буферного регистра, выход которого соединен с третьи.ми входа чн блоков синхронизации обмена, выход дополнительной памяти через исполнительный регистр соединен со аторымн входами буферного регистра, допол;игтельной памяти и узла модификации и перЕын входом регистра вывода, второй вход которого соединен с выходом регистра ввода и третьими входами дополнительно : па.чпти, буферного регистра н узла моднфикац, выход которого соединен с четвертымн входами буфертюго регистра и допалнвте. памяти. Источники информации, принятые во внимание при экспертизе . Патент ФРГ № 1800139 кл. 42 т ЗГ04, 1971. 2. Патент США К 3675209, кл. 340--172.5, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1984 |

|

SU1187174A1 |

| ПРОЦЕССОР ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ СХЕМ | 1972 |

|

SU435527A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

Авторы

Даты

1979-01-05—Публикация

1977-02-03—Подача