информационный вход блока управления является одноименным входом фильтра.

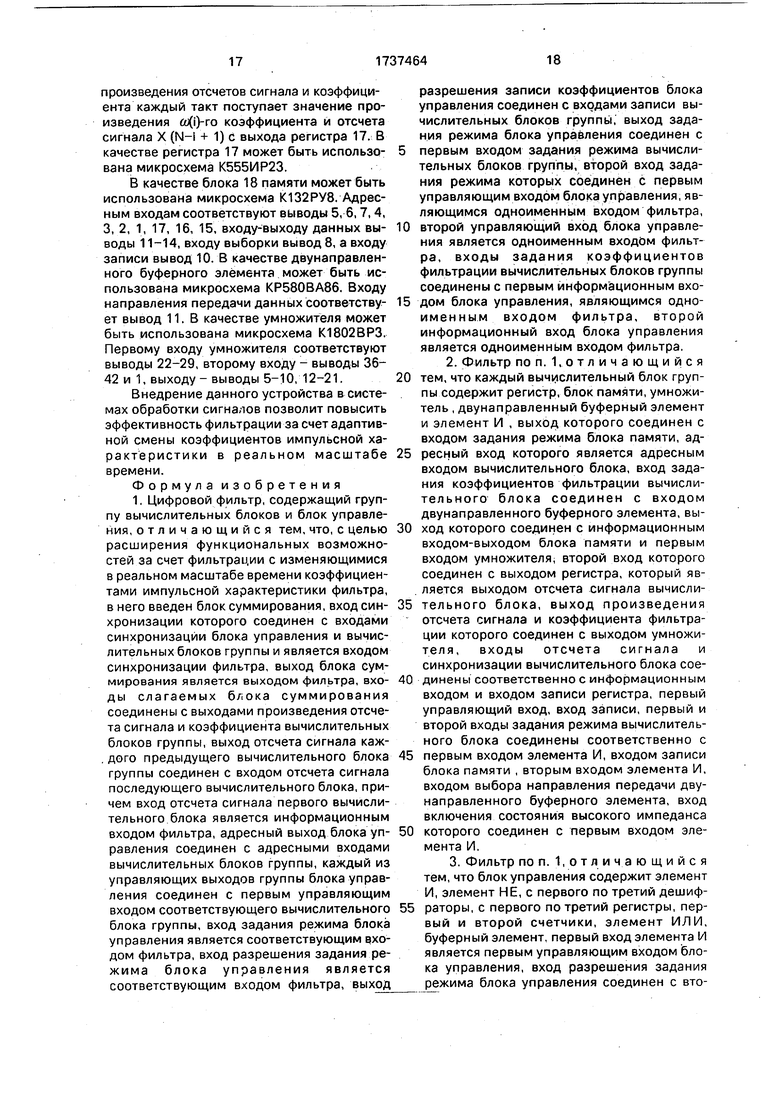

Каждый вычислительный блок группы содержит регистр, блок памяти, умножитель, двунаправленный буферный элемент и элемент И, выход которого соединен с входом задания режима блока памяти, адресный вход которого является адресным входом вычислительного блока, вход задания коэффициентов фильтрации вычислительного блока соединен с входом двунаправленного буферного элемента, выход которого соединен с информационным входом/выходом блока памяти и первым входом умножителя, второй вход которого соединен с выходом регистра, который является выходом отсчета сигнала вычислительного блока, выход произведения отсчета сигнала и коэффициента фильтрации которого соединен с выходом умножителя, входы отсчета сигнала и синхронизации вычислительного блока соединены соответственно с информационным входом и входом записи регистра, первый управляющий вход, вход записи, первый и второй входы задания режима вычислительного блока соединены соответственно к первым входом элемента И входом записи блока памяти, вторым входом элемента И, входом выбора направления передачи двунаправленного буферного элемента, вход включения состояния высокого импеданса которого соединен с первым входом элемента И.

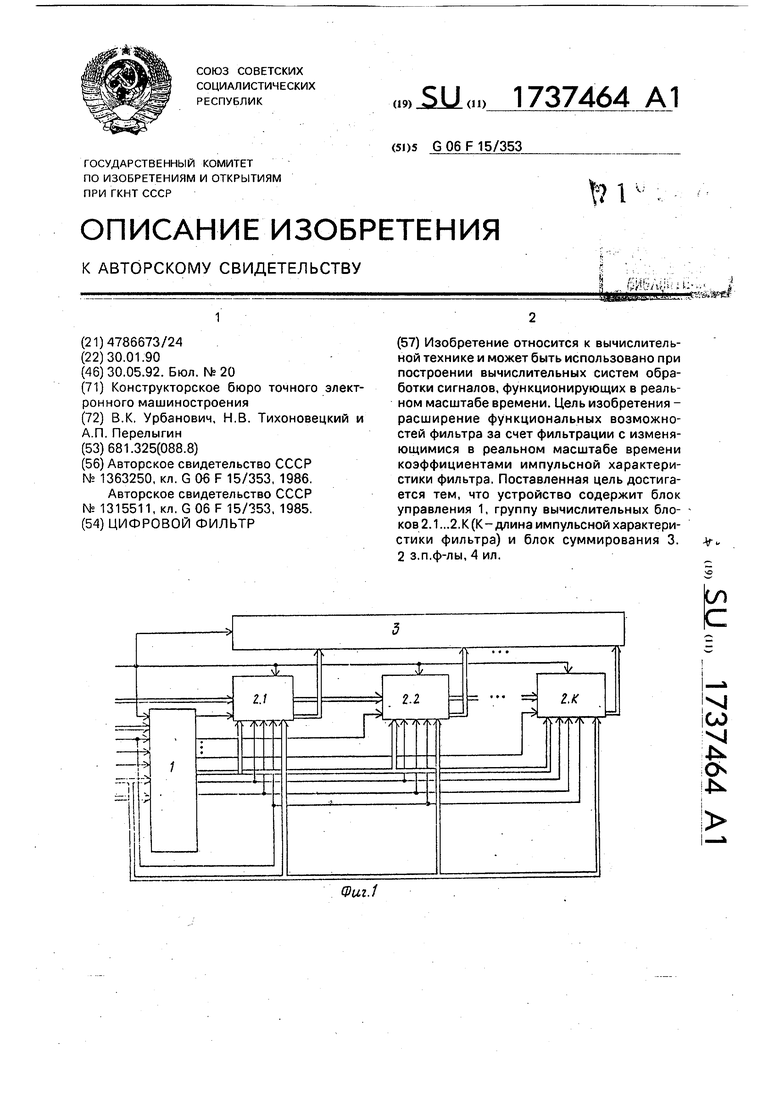

Блок управления содержит элемент И, элемент НЕ, с первого по третий дешифраторы, с первого по третий регистры, первый и второй счетчики, элемент ИЛИ, буферный элемент, первый вход элемента И является первым управляющим входом блока управления, вход разрешения задания режима блока управления соединен с вторым входом элемента И и входом разрешения второго дешифратора, информационный вход которого соединен с информационным входом первого дешифратора и является входом задания режима блока управления, выход элемента И соединен с входом разрешения первого дешифратора, выход которого соединен с входом разрешения третьего дешифратора, выходы которого являются группой управляющих выходов блока управления, выход разрешения записи коэффициентов которого соединен с первым выходом второго дешифратора, второй, третий и четвертый выходы которого соединены с входами записи соответственно второго, третьего и первого регистров, информационные входы которых соединены с первым информационным входом блока управления, второй информационный вход которого соединен с информационным входом буферного элемента, выход которого соединен с выходом первого регистра и информационным входом второго счетчика, выход которого является адресным выходом блока управления, вход синхронизации блока управления соединен со счетными входами первого и второго счетчиков, выход

0 переполнения первого счетчика соединен с первым входом элемента ИЛИ, выход которого соединен с входом разрешения счета второго счетчика, вход сброса которого соединен с входом сброса первого счетчика и

5 первым выходом третьего регистра, второй выход которого является выходом задания режима блока управления, второй управляющий вход которого соединен с входом разрешения счета первого счетчика и вторым

0 входом элемента ИЛИ, третий выход третьего регистра соединен с входом включения состояния высокого импеданса первого регистра и входом элемента НЕ, выход которого соединен с входом включения состояния

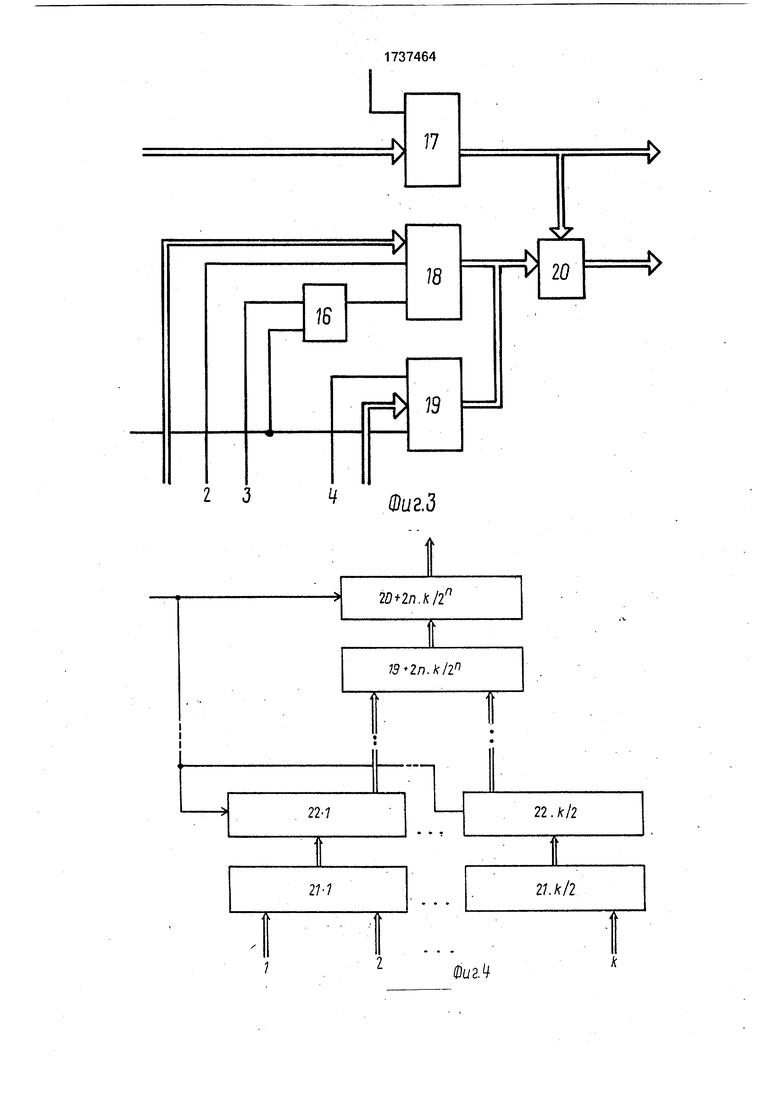

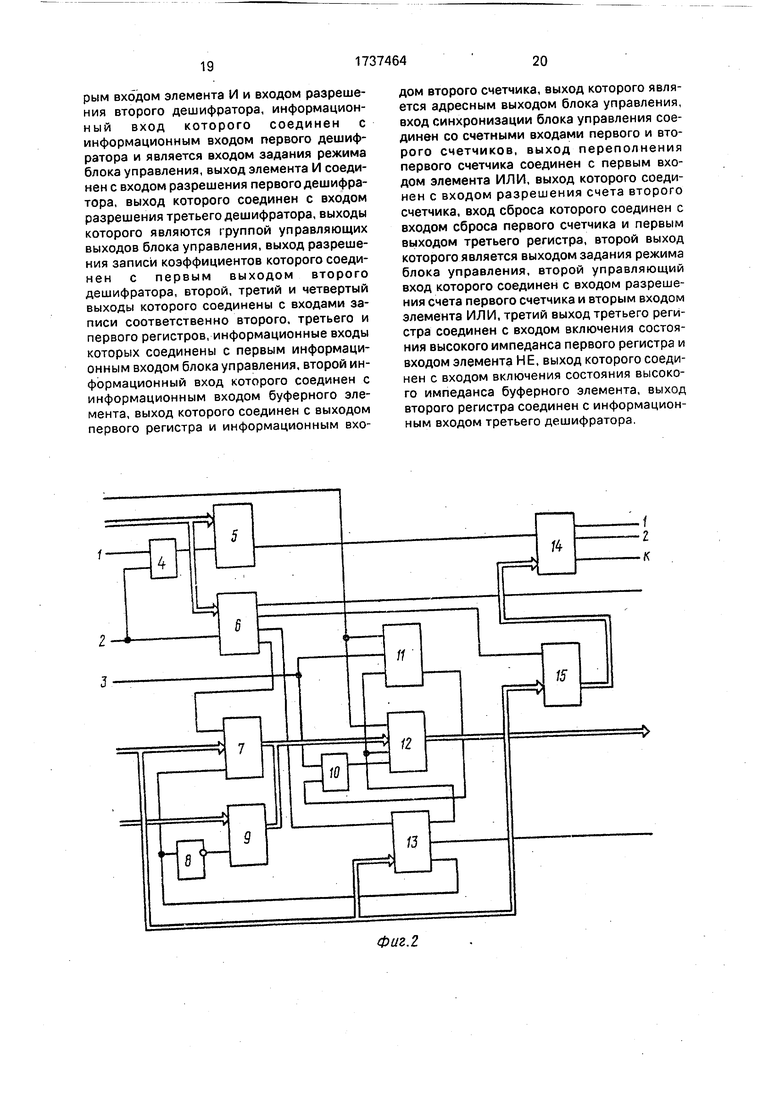

5 высокого импеданса буферного элемента, выход второго регистра соединен с информационным входом третьего дешифратора. На фиг. 1 приведена схема фильтра; на фиг. 2 - схема блока управления; на фиг. 3 0 схема вычислительного блока; на фиг. 4 - схема фильтра.

Фильтр содержит блок 1 управления, группу вычислительных блоков 2.1 ... 2.К(где К-длина импульсной характеристики филь5 тра) и блок 3 суммирования, причем вход синхронизации блока 3 суммирования соединен с входом синхронизации блока 1 управления и вычислительных блоков 2.1 ... 2.К группы и является входом синхронизации

0 фильтра, выход блока 3 суммирования является выходом фильтра входы слагаемых блока 3 суммирования соединены с выходами произведения отсчета сигнала и коэффициента вычислительных блоков 2.1 ... 2.К

5 группы, выход отсчета сигнала каждого предыдущего вычислительного блока 2.i (i -, К - 1) - группы соединен с входом отсчета сигнала последующего вычислительного блока 2.I + 1 ( 1, К-1), причем вход отсчета

0 сигнала первого вычислительного блока 2.1 является информационным входом фильтра, адресный вход блока 1 управления соединен с адресными входами вычислительных блоков 2.1 ... 2.К группы, i-й (i 1, К) управ5 ляющий выход блока 1 управления соединён с первым управляющим входом соответствующего 2. i-го (i 1, К) вычислительного блока группы, вход задания режима блока 1 управления является соответствующим входом фильтра, вход

разрешения задания режима блока 1 управления является соответствующим входом фильтра, выход разрешения записи коэффициентов блока 1 управления соединен с входами записи вычислительных блоков 2.1 ... 2.К группы, выход задания режима блока 1 управления соединён с первым входом задания режима вычислительных блоков 2.1 ... 2.К группы, второй вход задания режима которых соединен с первым управляющим входом блока 1 управления, являющимся одноименным входом фильтра, второй управляющий вход блока 1 управления является одноименным входом фильтра, входы задания коэффициентов фильтрации вычислительных блоков 2.1 ... 2.К группы соединены с первым информационным входом блока 1 управления, являющимся одноименным входом фильтра, второй информационный вход блока 1 управления является одноименным входом фильтра.

Для реализации процедуры цифровой фильтрации, устройство вычисляет выражение следующего вида:

к Y(N)- %w (i)X(N-l + 1),

i 1

где Y(N)- выходные отсчеты фильтра;

X(N) - входные отсчеты фильтра;

ftj(i) коэффициенты импульсной характеристики фильтра;

К - количество коэффициентов импульсной характеристики фильтра.

При этом имеется возможность смены коэффициентов импульсной характеристики фильтра либо по внешнему разрешающему сигналу, либо через каждые К тактов работы фильтра, либо через каждый такт работы фильтра.

Фильтр работает следующим образом.

Перед рассмотрением условимся, что вход задания режима фильтра подключается к шине адреса ЭВМ, первый информационный вход к шине данных ЭВМ, на первый управляющий вход фильтра подается сигнал чтения ЭВМ, а на вход разрешения задания режима - сигнал записи ЭВМ. Состоянию чтения ЭВМ соответствует сигнал чтения низкого уровня, сигнал записи высокого уровня, а состоянию записи ЭВМ сигнал записи низкого уровня, сигнал чтения высокого уровня. Фильтр имеет два основных режима работы: занесения коэффициентов импульсной характеристики и занесения коэффициентов импульсной характеристики и режим фильтрации.

Рассмотрим работу фильтра в режиме занесения коэффициентов импульсной характеристики. Для установки режима занесения коэффициентов импульсной характеристики ЭВМ по адресу, соответствующему установке состояния фильтра, записывает в

блок управления двоичный код 010. На входе задания режима фильтра ЭВМ выставляет значение адреса, соответствующего установке состояния фильтра.на первом информационном входе фильтра двоичный

код 010 и одновременно с данными на вход разрешения задания режима, ЭВМ выдает сигнал записи низкого уровня, по которому и производится запись двоичного кода 010 в блоке управления. После этой процедуры

сигнал на выходе задания режима блока управления переводится в состояние высокого уровня и, поступая на первый вход задания режима вычислительных блоков 2.1. 2.2 ... 2.4, разрешают им запись (или

чтение) данных с шины данных ЭВМ.

Затем по адресу, соответствующему установке номера М импульсной характеристике фильтра, ЭВМ записывает в блок управления код номера М импульсной характеристики, который после записи появляется на адресном выходе блока 1 управления и на адресных входах вычислительных блоков 2.1, 2.2 ... 2К. После этого по адресу, соответствующему установке i-ro

(1 1 ... К) номера отсчета импульсной характеристики фильтра производится запись от ЭВМ кода номера i (i 1, К) в блок 1 управления. Затем по адресу, соответствующему записи коэффициента импульсной характеристики, ЭВМ выставляет на первый информационный вход значение коэффициента w(i) 0 1. Ю- которое поступает на входы задания коэффициентов вычислительных блоков 2.1, 2.2 ...2К Одновременно

на i-м (i 1, К ) управляющем выходе и выходе разрешения записи коэффициентов блока 1 управления появляются сигналы в состоянии низкого уровня. Сигнал с выхода разрешения записи коэффициентов блока 1

управления переводит вычислительные блоки 2.1, 2.2 ... 2JC в состояние записи данных с первого информационного входа фильтра, а сигнал с i-ro(i 1, К) управляющего выхода разрешает запись данных с входа задания

коэффициентов только 2.1-му вычисли- тельному блоку, т.е. производится запись оХО (I Т, К) коэффициента импульсной характеристики фильтра в 2.1-й (i 1, К) вычислительный блок. Для контроля ЭВМ может

прочитать значение ft)(i)-ro коэффициента по тому же адресу, что и при его записи. При этом сигналом чтения от ЭВМ в состоянии низкого уровня, поступающим на первый управляющий вход блока 1 управления и

вторые входы задания режима вычислительных блоков 2.1 ... 2К, вычислительные блоки 2.1, 2.2 ... ЯК переводятся в состояние выдачи &ХО коэффициента М-й импульсной характеристики на вход задания коэффициентов, но разрешается выдача ft$)-ro (i 1. К) коэффициента только тому 2.1-му (1 1, К) вычислительному блоку, на первый управляющий вход которого поступает сигнал в состоянии низкого уровня с i-ro (i 1, К) управляющего выхода блока 1 управления. Аналогичным образом для импульсной характеристики записываются (читаются) все К коэффициентов. Затем в блок 1 управления заносится следующий номер М + 1 импульсной характеристики и производится запись (чтение) ft#)-x (i 1, К) коэффициентов М + 1 импульсной характеристики и т.д. Завершается этот режим операцией записи некоторого номера М по адресу, соответствующему установке номера М импульсной характеристике.

В режим фильтрации устройство переводится записью от ЭВМ в блок 1 управления по адресу, соответствующему установке состояния фильтра двоичного кода состояния 000 или 001., или 100. Двоичному коду

000соответствует режим фильтрации с неизменяющейся импульсной характеристикой с номером М и длиной К, двоичному коду

001режим фильтрации с изменяющейся, начиная с номера М, импульсной характеристикой длиной К через каждые К тактов, либо по внешнему разрешающему сигналу, двоичному коду 100 - режим фильтрации с изменяющимися каждый такт коэффициентами импульсной характеристики фильтра.

Рассмотрим работу фильтра в режиме фильтрации с М-й импульсной характеристикой длиной К. После записи двоичного кода состояния в блок 1 управления на i-x (h - 1, К) управляющих выходах и выходе разрешения записи коэффициентов формируются сигналы в состоянии высокого уровня, на выходе задания режима сигнал низкого уровня. На адресном выходе блока 1 управления формируется код номера М импульсной характеристики, поступающий на адресные входы вычислительных блоков 2.1, 2.2 ... 2.К. На информационный вход фильтра подается входная последовательность Х(М). Тогда в произвольном N-м такте на выходе произведения отсчета сигнала и коэффициента вычислительного блока 2.1 имеем произведение X(N)-O) (1), на выходе отсчета сигнала отсчет сигнала X(N), на выходе произведения отсчета сигнала 4 коэффициента вычислительного блока 2.2 произведение X(N - 1) (о (2), на выходе

отсчета сигнала отсчет сигнала X(N-1) и т.д., т.е. на выходе произведения отсчета сигнала и коэффициента вычислительного блока 2,К произведение X(N - К + )ш (К),на выходе отсчета сигнала отсчет сигнала X (N - К + 1). Первые К-1 тактов работы фильтра будут холостые. На К-м такте, после суммирования в блоке 3 суммирования произведений с выходов произведения отсчета сигнала и коэффициента вычислительных блоков 2.1, 2.2 ... 2.К, на выходе блока 3 суммирования будем иметь результат фильтрации в соответствии с указанным выражением.

Рассмотрим работу фильтра в режиме фильтрации с изменяющейся импульсной характеристикой длиной К, начиная с номера М. После записи двоичного кода состояния 001 в блоке 1 управления на 1-х управляющих выходах, выходе разрешения записи коэффициентов и выходе задания режима блока управления формируются такие же сигналы, как и в предыдущем случае. Состояние адресного выхода блока 1 управления в этом режиме будет зависеть от состояния сигнала на втором управляющем входе блока управления. Если этот сигнал будет постоянно в состоянии низкого уровня, то на адресном выходе блока 1 управления через каждые К тактов значение кода номера М импульсной характеристики будет изменяться на единицу, т.е. через каждые 2 тактов работы будем иметь смену коэффициентов импульсной характеристики по заранее заданному закону.

При подаче на второй управляющий вход блока 1 управления импульсов низкого уровня длиной К тактов, значение кода номера М импульсной характеристики будет изменяться на единицу по каждому импульсу, т.е. по каждому внешнему импульсу на втором управляющем входе блока 1 управления будем иметь смену коэффициентов импульсной характеристики. Работа вычислительных блоков 2.1, 2.2 ... 2.К и блока 3 суммирования в режиме фильтрации без изменения коэффициентов.

Рассмотрим работу фильтра в режиме фильтрации с изменяющимися каждый такт коэффициентами импульсной характеристики. После записи двоичного кода 100 в блок 1 управления на i-x управляющих выхо- дах; выходе разрешения записи коэффициентов и выходе задания режима блока управления формируются такие же сигналы, как и в предыдущем случае. Состояние адресного блока управления в этом режиме будет повторять состояние сигнала на втором информационном входе блока управления. Сигнал на втором информационном

входе блока управления будет тактироваться в блоке управления и подаваться на его адресный выход. Таким образом, имея на втором информационном входе блока управления изменяющийся каждый такт код, на адресном выходе блока управления получаем изменяющийся каждый такт номер М импульсной характеристики, определяемой этим кодом, т.е. получаем в результате смену коэффициентов импульсной характеристики в каждом такте. Работа вычислительных блоков 2.1,2.2... 2К и блока 3 суммирования в этом режиме аналогична режиму фильтрации без изменения коэффициентов.

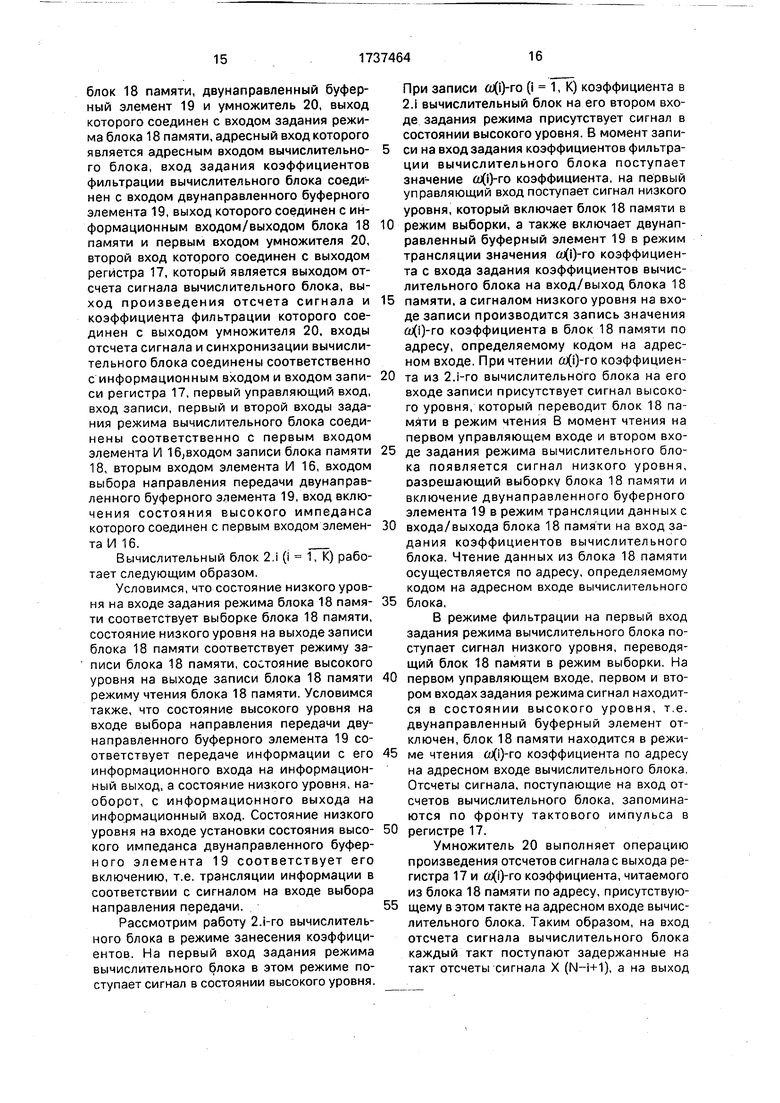

Блок управления содержит элемент И 4, первый 5 и второй 6 дешифраторы, первый регистр 7, элемент НЕ 8, буферный элемент

9,элемент ИЛИ 10, счетчики 11 и 12, третий регистр 13, дешифратор 14 и второй регистр 15.

Первый вход элемента И 4 является первым управляющим входом блока управления, вход разрешения задания режима блока управления соединен с вторым входом элемента И 4 и входом разрешения второго дешифратора 6,информационный вход которого соединен с информационным входом первого дешифратора 5 и является входом задания режима блока управления, выход элемента И 4 соединен с входом разрешения первого дешифратора 5, выход которого соединен с входом разрешения третьего дешифратора 14, выходы которого являются группой управляющих выходов 1 ... К блока управления, выход разрешения записи коэффициентов которого соединен с первым выходом второго дешифратора б, второй, третий и четвертый выходы которого соединены с входами записи соответственно второго 15, третьего 13 и первого 7 регистров, информационные входы которых соединены с первым информационным входом блока управления, второй информационный вход которого соединен с информационным входом буферного элемента 9, выход которого соединен с выходом первого регистра 7 и информационным входом второго счетчика 12, выход которого является адресным выходом блока управления, вход синхронизации блока управления соединен со счетными входами первого 11 и второго 12 счетчиков, выход переполнения первого счетчика 11 соединен с первым входом элемента ИЛИ

10,выход которого соединен с входом разрешения счета второго счетчика 12, вход сброса которого соединен с входом сброса первого счетчика 11 и первым выходом

третьего регистра 13, второй в.ыход которого является выходом задания режима блока управления, второй управляющий вход которого соединен с

входом разрешения счета первого счетчика 11 и вторым входом элемента ИЛИ 10, третий выход третьего регистра 13 соединен с входом включения состояния высокого импеданса первого регистра 7

0 и входом элемента НЕ 8, выход которого соединен с входом включения состояния высокого импеданса буферного элемента 9, выход второго регистра 15 соединен с информационным входом третьего де5 шифратора 14.

Блок 1 управления работает следующим образом.

Условимся, что разрешение работы дешифраторов 5, 6, и 14 производится подачей

0 сигнала низкого уровня на вход разрешения, сброс и разрешение счета счетчиков 11 и 12 производится подачей сигнала низкого уровня на соответствующие входы. В режиме сброса счетчика 11, 12 осуществляют

5 трансляцию данных с входа на выход, тактируемую импульсами на счетном входе. Сигнал переноса счетчика 11 имеет состояние низкого уровня. Условимся также, что установка состояния высокого импеданса

0 регистра 7 и буферного элемента 9 соответствует сигналу в состоянии высокого уровня на входе установки состояния высокого импеданса этих элементов.

Рассмотрим работу блока 1 управления

5 в режиме занесения коэффициентов фильтрации.

При установке этого режима значение адреса, соответствующего установке состояния фильтра, дешифруется дешифра0 торами 5 и 6. При поступлении от ЭВМ на вход разрешения задания режима блока управления сигнала записи в состоянии низкого уровня разрешается работа дешифратору 6, на третьем выходе которого

5 формируется сигнал записи, которым производится запись двоичного кода 010 с первого информационного входа в регистр 13. В результате этой процедуры сигналом низкого уровня с первого выхода регистра

0 13 счетчики 11 и 12 переводятся в режим сброса, сигнал высокого уровня с второго выхода регистра 13 устанавливает состояние высокого уровня выхода задания режима, блока 1 управления, сигналом

5 низкого уровня с третьего выхода регистра 13 устанавливается состояние высокого импеданса буферного элемента 9 и включается регистр 7.

При записи номера М импульсной характеристики в блок управления подобно

тому, как и в предыдущем случае, на четвертом выходе дешифратора б формируется сигнал записи, по которому производится запись кода номера М импульсной характеристики фильтра в регистр 7. Так как счетчик 12 находится в режиме сброса, то данные с выхода регистра 7 транслируются на адресный выход блока управления.

При записи номера i коэффициента импульсной характеристики фильтра сигналом с второго дешифратора 6 производится запись этого номера i в регистр 15.

При записи значения ftj(i)(i 1, К) коэффициента на первом выходе дешифратора 5 формируется сигнал разрешения для де; шифратора 14 и на одном из его f-x (1 1, К) выходов, определяемом состоянием регистра 15, появляется сигнал низкого уровня, поступающий на i-й управляющий выход блока управления. Одновременно с ним на выходе разрешения записи коэффициентов блока управления поступает сигнал низкого уровня с первого выхода дешифратора 6. При чтении (а() коэффициента сигналом чтения на первом управляющем входе блока управления разрешения будет даваться только дешифратору 5 и сигнал низкого уровня будет только на i-м (i И, к) выходе дешифратора 14 и соответственно i-м (i 1, К) управляющем выходе блока управления.

В режиме фильтрации в регистр 13 блока управления заносится двоичный код 000 или 001j или 100. В первом случае на выход разрешения записи коэффициентов блока управления с второго выхода регистра 13 поступает сигнал низкого уровня, а на адресный выход транслируемый через счетчик 12 код с регистра 7, так как на входе сброса счетчика 12 присутствует сигнал низкого уровня с первого выхода регистра 13, а регистр 7 включен сигналом низкого уровня с третьего выхода регистра 13. Во втором случае сигнал на выходе разрешения записи коэффициентов блока управления также находится в состоянии низкого уровня, сигнал высокого уровня на входе сброса счетчиков 11,12 переводит их в режим счета и сигнал на адресном выходе блока управления будет определяться состоянием сигнала на втором управляющем входе блока 1 управления. Сигнал низкого уровня на этом входе разрешает работу счетчику 11. Через К тактов на выходе переноса счетчика 11 формируется сигнал низкого уровня, который через элемент ИЛИ 10 поступает на вход разрешения счета счетчика 12, что вызывает изменение

на единицу его выходного кода, начиная с номера М, предварительно занесенного в регистр 7. При подаче на второй управляющий вход импульсов низкого уровня длиной

К тактов будем иметь изменение выходного кода счетчика 12 по каждому входному импульсу. В третьем случае сигналом высокого уровня с третьего выхода регистра 13 устанавливается

0 состояние высокого импеданса регистра 7 и включается буферный элемент 9, в результате чего данные с второго информационного входа блока управления поступают на вход счетчика 12.

5 Сигнал низкого уровня с первого выхода регистра 13 переводит счетчик 12 в режим сброса и данные с четвертого управляющего входа блока управления тактируются и транслируются на его ад0 ресный выход, сигнал на выходе задания режима блока управления, как и в предыдущем случае, находится в состоянии низкого уровня.

В качестве элемента И 4 можно исполь5 зовать микросхему К155ЛИ1. При этом первому входу соответствует первый вывод, второму входу второй вывод, выходу - третий вывод. В качестве дешифраторов 5, б и 14 можно использовать микросхемы

0 К155ИДЗ. При этом входу разрешения соответствует вывод 18, входам-выводы 20, 21,22 и 23, выходам-выводы 1-11, 13-17. В качестве регистров 7, 15 и регистра 13 состояния могут использоваться регистры

5 К55ИР23. Информационным входам регистра соответствуют выводы 3, 4, 7, 8, 13, 14, 17 и 18, информационным выхо- дам-выводы 2, 5, 6, 8, 12, 15, 16 и 19, входу записи вывод 11, входу установки треть0 его состояния первый вывод. В качестве счетчиков 11 и 12 могут использоваться микросхемы К531ИЕ17. Счетному входу соответствует вывод 2, входу разрешения счета вывод, входу установки вывод

5 9, входам выводы 3-6, выходам выводы 11 - 14. В качестве элемента НЕ 8 может использоваться микросхема К155АН1. При этом ее входу соответствует вывод 1, выходу вывод 2. Первому входу соответ0 ствует первый вывод, второму входу второй вывод, выходу третий вывод. В качестве буферного элемента 9 может быть использована микросхема КР580ВА86. Информационным входам со5 ответствуют выводы 1-8, информационным выходам выводы 19, 18, 17, 16, 15, 14, 13, 12 и 11, входу установки третьего состояния вывод 9.

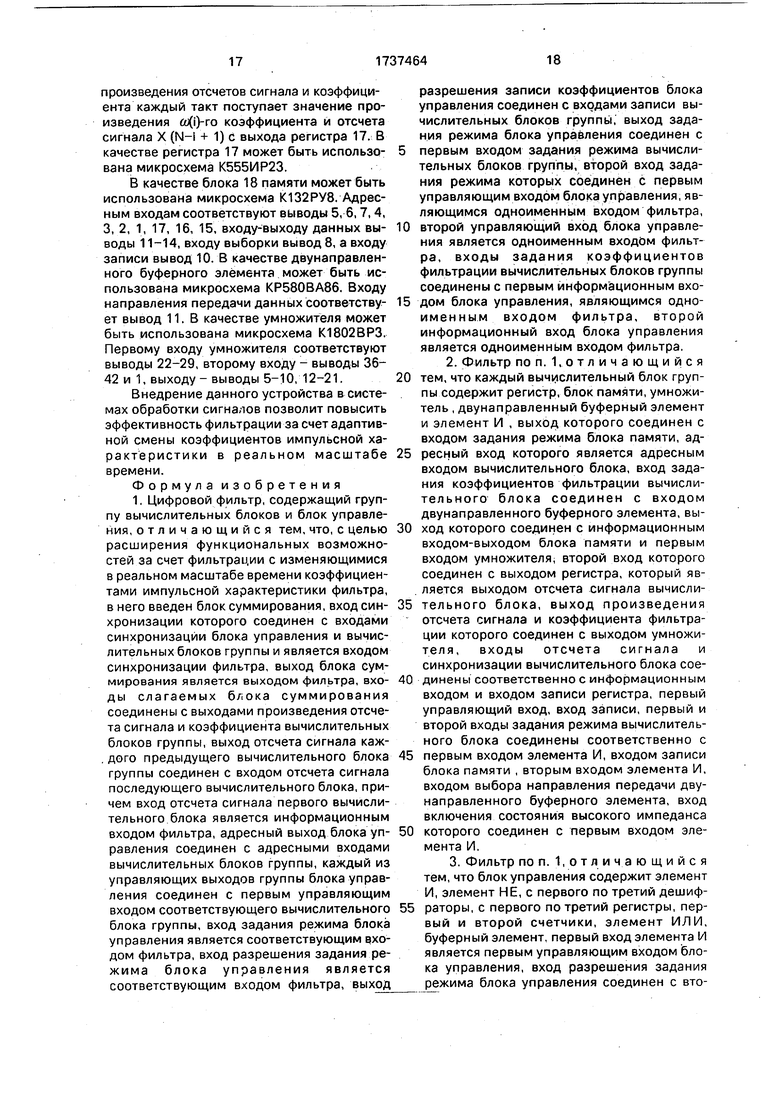

Каждый вычислительный блок 2 группы 2.1 ... 2.К содержит элемент И 16, регистр 17,

блок 18 памяти, двунаправленный буферный элемент 19 и умножитель 20, выход которого соединен с входом задания режима блока 18 памяти, адресный вход которого является адресным входом вычислительного блока, вход задания коэффициентов фильтрации вычислительного блока соединен с входом двунаправленного буферного элемента 19, выход которого соединен с информационным входом/выходом блока 18 памяти и первым входом умножителя 20, второй вход которого соединен с выходом регистра 17, который является выходом отсчета сигнала вычислительного блока, выход произведения отсчета сигнала и коэффициента фильтрации которого соединен с выходом умножителя 20, входы отсчета сигнала и синхронизации вычислительного блока соединены соответственно с информационным входом и входом записи регистра 17, первый управляющий вход, вход записи, первый и второй входы задания режима вычислительного блока соединены соответственно с первым входом элемента И 1 выходом записи блока памяти 18, вторым входом элемента И 16, входом выбора направления передачи двунаправленного буферного элемента 19, вход включения состояния высокого импеданса которого соединен с первым входом элемента И 16.

Вычислительный блок 2.i (i 1, К) работает следующим образом.

Условимся, что состояние низкого уровня на входе задания режима блока 18 памяти соответствует выборке блока 18 памяти, состояние низкого уровня на выходе записи блока 18 памяти соответствует режиму записи блока 18 памяти, состояние высокого уровня на выходе записи блока 18 памяти режиму чтения блока 18 памяти. Условимся также, что состояние высокого уровня на входе выбора направления передачи двунаправленного буферного элемента 19 соответствует передаче информации с его информационного входа на информационный выход, а состояние низкого уровня, наоборот, с информационного выхода на информационный вход. Состояние низкого уровня на входе установки состояния высокого импеданса двунаправленного буферного элемента 19 соответствует его включению, т.е. трансляции информации в соответствии с сигналом на входе выбора направления передачи.

Рассмотрим работу 2.i-ro вычислительного блока в режиме занесения коэффициентов. На первый вход задания режима вычислительного блока в этом режиме поступает сигнал в состоянии высокого уровня.

При записи й#)-го (i 1, К) коэффициента в 2.I вычислительный блок на его втором входе задания режима присутствует сигнал в состоянии высокого уровня. В момент запи- си на вход задания коэффициентов фильтра- ции вычислительного блока поступает значение й#)-го коэффициента, на первый управляющий вход поступает сигнал низкого

уровня, который включает блок 18 памяти в

режим выборки, а также включает двунаправленный буферный элемент 19 в режим трансляции значения ftj(i)-ro коэффициента с входа задания коэффициентов вычислительного блока на вход/выход блока 18

памяти, а сигналом низкого уровня на входе записи производится запись значения oi(i)-ro коэффициента в блок 18 памяти по адресу, определяемому кодом на адресном входе. При чтении №(i)-ro коэффициента из 2.1-го вычислительного блока на его входе записи присутствует сигнал высокого уровня, который переводит блок 18 памяти в режим чтения В момент чтения на первом управляющем входе и втором входе задания режима вычислительного блока появляется сигнал низкого уровня, разрешающий выборку блока 18 памяти и включение двунаправленного буферного элемента 19 в режим трансляции данных с

входа/выхода блока 18 памяти на вход задания коэффициентов вычислительного блока. Чтение данных из блока 18 памяти осуществляется по адресу, определяемому кодом на адресном входе вычислительного

блока.

В режиме фильтрации на первый вход задания режима вычислительного блока поступает сигнал низкого уровня, переводящий блок 18 памяти в режим выборки. На

первом управляющем входе, первом и втором входах задания режима сигнал находится в состоянии высокого уровня, т.е. двунаправленный буферный элемент отключен, блок 18 памяти находится в режиме чтения ct#)-ro коэффициента по адресу на адресном входе вычислительного блока. Отсчеты сигнала, поступающие на вход отсчетов вычислительного блока, запоминаются по фронту тактового импульса в

регистре 17.

Умножитель 20 выполняет операцию произведения отсчетов сигнала с выхода регистра 17 и д( коэффициента, читаемого из блока 18 памяти по адресу, присутствующему в этом такте на адресном входе вычислительного блока. Таким образом, на вход отсчета сигнала вычислительного блока каждый такт поступают задержанные на такт отсчеты сигнала X (N-i+1), а на выход

произведения отсчетов сигнала и коэффициента каждый такт поступает значение произведения (О()-го коэффициента и отсчета сигнала X (N-i + 1) с выхода регистра 17. В качестве регистра 17 может быть использована микросхема К555ИР23.

В качестве блока 18 памяти может быть использована микросхема К132РУ8. Адресным входам соответствуют выводы 5, 6, 7, 4, 3, 2, 1, 17, 16, 15, входу-выходу данных выводы 11-14, входу выборки вывод 8, а входу записи вывод 10. В качестве двунаправленного буферного элемента может быть использована микросхема КР580ВА86. Входу направления передачи данных соответствует вывод 11. В качестве умножителя может быть использована микросхема К1802ВРЗ. Первому входу умножителя соответствуют выводы 22-29, второму входу - выводы 36- 42 и 1, выходу- выводы 5-10, 12-21.

Внедрение данного устройства в системах обработки сигналов позволит повысить эффективность фильтрации за счет адаптивной смены коэффициентов импульсной характеристики в реальном масштабе времени.

Формула изобретения

1. Цифровой фильтр, содержащий группу вычислительных блоков и блок управления, отличающийся тем, что, с целью расширения функциональных возможностей за счет фильтрации с изменяющимися в реальном масштабе времени коэффициентами импульсной характеристики фильтра, в него введен блок суммирования, вход синхронизации которого соединен с входами синхронизации блока управления и вычислительных блоков группы и является входом синхронизации фильтра, выход блока суммирования является выходом фильтра, входы слагаемых блока суммирования соединены с выходами произведения отсчета сигнала и коэффициента вычислительных блоков группы, выход отсчета сигнала каждого предыдущего вычислительного блока группы соединен с входом отсчета сигнала последующего вычислительного блока, причем вход отсчета сигнала первого вычислительного блока является информационным входом фильтра, адресный выход блока управления соединен с адресными входами вычислительных блоков группы, каждый из управляющих выходов группы блока управления соединен с первым управляющим входом соответствующего вычислительного блока группы, вход задания режима блока управления является соответствующим входом фильтра, вход разрешения задания режима блока управления является соответствующим входом фильтра, выход

разрешения записи коэффициентов блока управления соединен с входами записи вычислительных блоков группы, выход задания режима блока управления соединен с

первым входом задания режима вычислительных блоков группы, второй вход задания режима которых соединен с первым управляющим входом блока управления, являющимся одноименным входом фильтра,

0 второй управляющий вход блока управления является одноименным входом фильтра, входы задания коэффициентов фильтрации вычислительных блоков группы соединены с первым информационным вхо5 дом блока управления, являющимся одноименным входом фильтра, второй информационный вход блока управления является одноименным входом фильтра.

2.Фильтр по п. 1,отличающийся 0 тем, что каждый вычислительный блок группы содержит регистр, блок памяти, умножитель , двунаправленный буферный элемент и элемент И , выход которого соединен с входом задания режима блока памяти, ад5 ресный вход которого является адресным входом вычислительного блока, вход задания коэффициентов фильтрации вычислительного блока соединен с входом двунаправленного буферного элемента, вы0 ход которого соединен с информационным входом-выходом блока памяти и первым входом умножителя, второй вход которого соединен с выходом регистра, который является выходом отсчета сигнала вычисли5 тельного блока, выход произведения отсчета сигнала и коэффициента фильтрации которого соединен с выходом умножителя, входы отсчета сигнала и синхронизации вычислительного блока сое0 динены соответственно с информационным входом и входом записи регистра, первый управляющий вход, вход записи, первый и второй входы задания режима вычислительного блока соединены соответственно с

5 первым входом элемента И, входом записи блока памяти , вторым входом элемента И, входом выбора направления передачи двунаправленного буферного элемента, вход включения состояния высокого импеданса

0 которого соединен с первым входом элемента И.

3.Фильтр по п. 1,отличающийся тем, что блок управления содержит элемент И, элемент НЕ, с первого по третий дешиф5 раторы, с первого по третий регистры, первый и второй счетчики, элемент ИЛИ, буферный элемент, первый вход элемента И является первым управляющим входом блока управления, вход разрешения задания режима блока управления соединен с вторым входом элемента И и входом разрешения второго дешифратора, информационный вход которого соединен с информационным входом первого дешифратора и является входом задания режима блока управления, выход элемента И соединен с входом разрешения первого дешифратора, выход которого соединен с входом разрешения третьего дешифратора, выходы которого являются группой управляющих выходов блока управления, выход разрешения записи коэффициентов которого соеди- нен с первым выходом второго дешифратора, второй, третий и четвертый выходы которого соединены с входами записи соответственно второго, третьего и первого регистров, информационные входы которых соединены с первым информационным входом блока управления, второй информационный вход которого соединен с информационным входом буферного элемента, выход которого соединен с выходом первого регистра и информационным входом второго счетчика, выход которого является адресным выходом блока управления, вход синхронизации блока управления соединен со счетными входами первого и второго счетчиков, выход переполнения первого счетчика соединен с первым входом элемента ИЛИ, выход которого соединен с входом разрешения счета второго счетчика, вход сброса которого соединен с входом сброса первого счетчика и первым выходом третьего регистра, второй выход которого является выходом задания режима блока управления, второй управляющий вход которого соединен с входом разрешения счета первого счетчика и вторым входом элемента ИЛИ, третий выход третьего регистра соединен с входом включения состояния высокого импеданса первого регистра и входом элемента НЕ, выход которого соединен с входом включения состояния высокого импеданса буферного элемента, выход второго регистра соединен с информационным входом третьего дешифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| Таймер | 1985 |

|

SU1357939A1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1381541A1 |

| Цифровой фильтр | 1987 |

|

SU1501088A1 |

| Цифровой адаптивный фильтр | 1990 |

|

SU1837322A1 |

| Устройство для вычисления свертки | 1990 |

|

SU1709342A1 |

| Устройство для воспроизведения запаздывающих функций | 1983 |

|

SU1173424A1 |

| УСТРОЙСТВО БУФЕРИЗАЦИИ И СИНХРОНИЗАЦИИ ДЛЯ ОБРАБОТКИ НЕПРЕРЫВНОГО СИГНАЛА | 1990 |

|

SU1812885A1 |

| УСТРОЙСТВО АВТОВЫБОРА ДИСКРЕТНОГО КАНАЛА | 2011 |

|

RU2488222C1 |

Фиг. 2

г з

Ш

20

,-is

19

®иг.З

2D+2n.k/2r

.k/2n

Т

Авторы

Даты

1992-05-30—Публикация

1990-01-30—Подача