XI OJ

VJ

XI

hO О

Изобретение относится к импульсной технике и может быть использовано в системах преобразования и передачи информации с фазоимпульсным представлением. Целью изобретения является повышение точности.

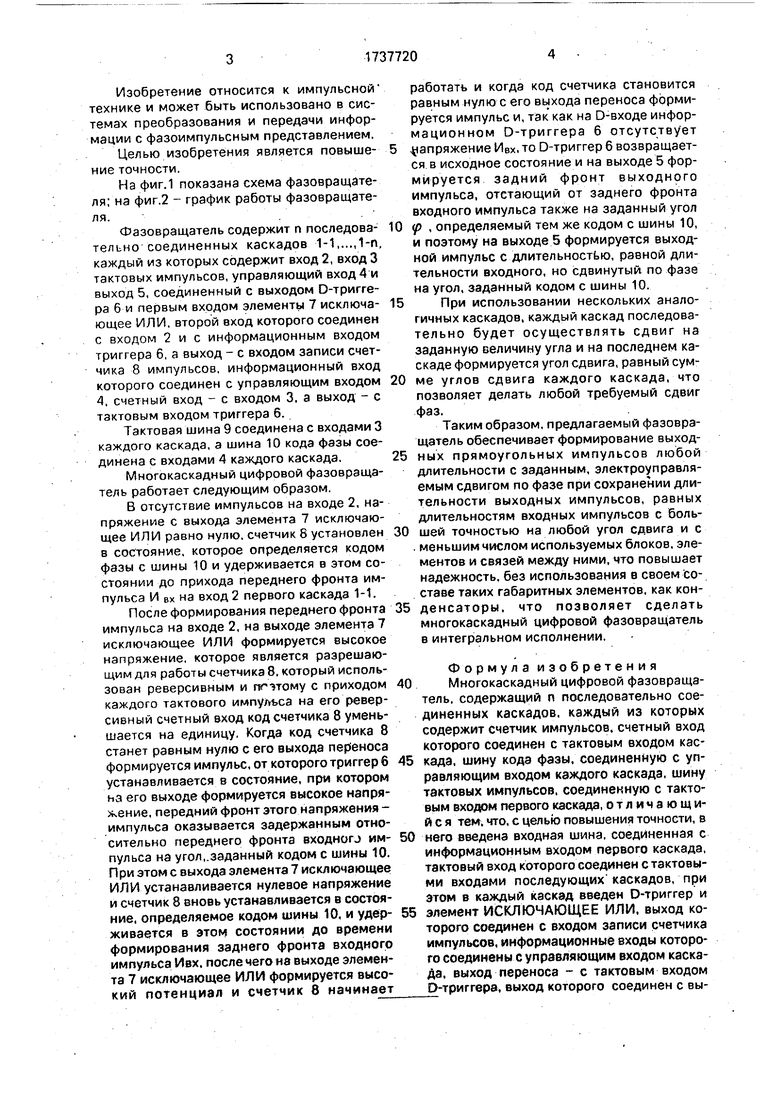

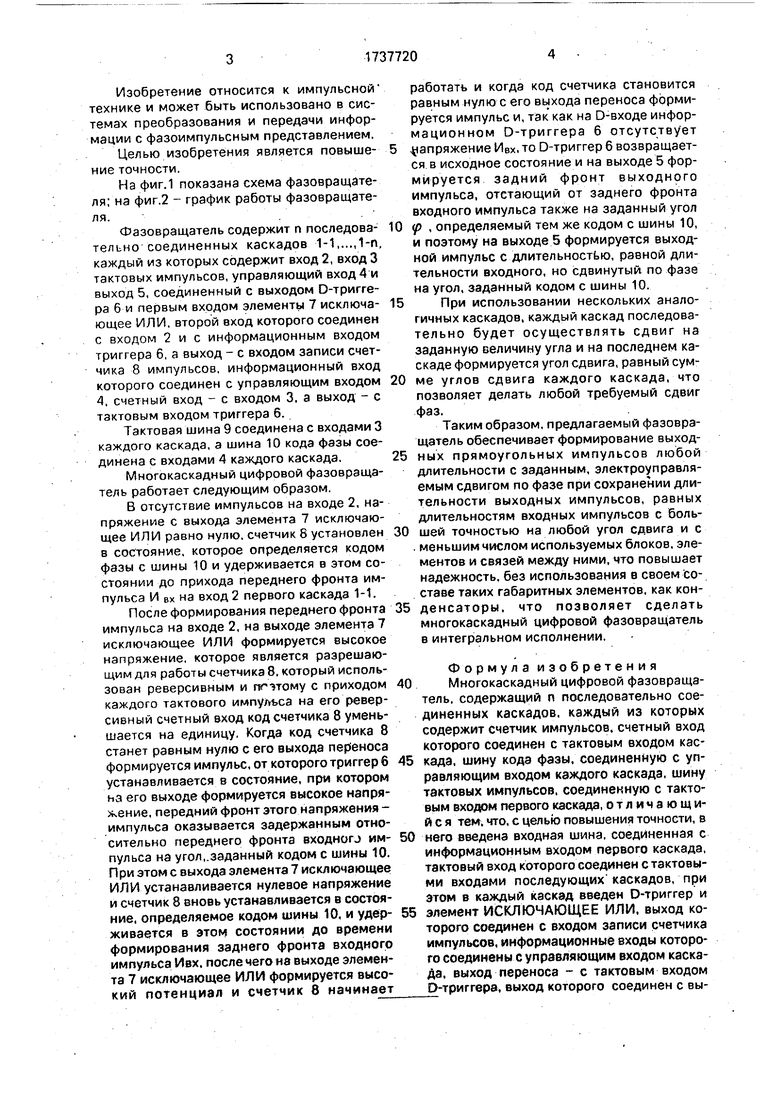

На фиг.1 показана схема фазовращателя; на фиг.2 - график работы фазовращателя.

Фазовращатель содержит п последовательно соединенных каскадов 1-1,...,1-п, каждый из которых содержит вход 2, вход 3 тактовых импульсов, управляющий вход 4 и выход 5, соединенный с выходом D-тригге- ра 6 и первым входом элементы 7 исключающее ИЛИ, второй вход которого соединен с входом 2 и с информационным входом триггера 6, а выход - с входом записи счетчика 8 импульсов, информационный вход которого соединен с управляющим входом 4. счетный вход - с входом 3, а выход - с тактовым входом триггера 6.

Тактовая шина 9 соединена с входами 3 каждого каскада, а шина 10 кода фазы соединена с входами 4 каждого каскада.

Многокаскадный цифровой фазовращатель работает следующим образом.

В отсутствие импульсов на входе 2, напряжение с выхода элемента 7 исключающее ИЛИ равно нулю, счетчик 8 установлен в состояние, которое определяется кодом фазы с шины 10 и удерживается в этом состоянии до прихода переднего фронта импульса И вх на вход 2 первого каскада 1-1.

После формирования переднего фронта импульса на входе 2, на выходе элемента 7 исключающее ИЛИ формируется высокое напряжение, которое является разрешающим для работы счетчика 8. который использован реверсивным и пгттому с приходом каждого тактового импулъса на его реверсивный счетный вход код счетчика 8 уменьшается на единицу. Когда код счетчика 8 станет равным нулю с его выхода переноса формируется импульс, от которого триггер 6 устанавливается в состояние, при котором на его выходе формируется высокое напряжение, передний фронт этого напряжения - импульса оказывается задержанным относительно переднего фронта входного импульса на угол,.заданный кодом с шины 10. При этом с выхода элемента 7 исключающее ИЛИ устанавливается нулевое напряжение и счетчик 8 вновь устанавливается в состояние, определяемое кодом шины 10, и удерживается в этом состоянии до времени формирования заднего фронта входного импульса Ивх. после чего на выходе элемента 7 исключающее ИЛИ формируется высокий потенциал и счетчик 8 начинает

работать и когда код счетчика становится равным нулю с его выхода переноса формируется импульс и, так как на D-входе инфор- мационном D-триггера б отсутствует

.напряжение ИВх, то D-триггер 6 возвращается в исходное состояние и на выходе 5 формируется задний фронт выходного импульса, отстающий от заднего фронта входного импульса также на заданный угол

р , определяемый тем же кодом с шины 10, и поэтому на выходе 5 формируется выходной импульс с длительностью, равной длительности входного, но сдвинутый по фазе на угол, заданный кодом с шины 10.

При использовании нескольких аналогичных каскадов, каждый каскад последова- тельно будет осуществлять сдвиг на заданную величину угла и на последнем каскаде формируется угол сдвига, равный сумме углов сдвига каждого каскада, что позволяет делать любой требуемый сдвиг фаз.

Таким образом, предлагаемый фазовращатель обеспечивает формирование выходных прямоугольных импульсов любой длительности с заданным, электроуправля- емым сдвигом по фазе при сохранении длительности выходных импульсов, равных длительностям входных импульсов с большей точностью на любой угол сдвига и с . меньшим числом используемых блоков, элементов и связей между ними, что повышает надежность, без использования в своем составе таких габаритных элементов, как конденсаторы. что позволяет сделать многокаскадный цифровой фазовращатель в интегральном исполнении.

Формула изобретения

Многокаскадный цифровой фазовращатель, содержащий п последовательно соединенных каскадов, каждый из которых содержит счетчик импульсов, счетный вход которого соединен с тактовым входом каскада, шину кода фазы, соединенную с управляющим входом каждого каскада, шику тактовых импульсов, соединенную с тактовым входом первого каскада, отличающийся тем. что, с целью повышения точности, в

него введена входная шина, соединенная с информационным входом первого каскада, тактовый вход которого соединен с тактовыми входами последующих каскадов, при этом 8 каждый каскад введен D-триггер и

элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. выход которого соединен с входом записи счетчика импульсов, информационные входы которого соединены с управляющим входом каскада, выход переноса - с тактовым входом D-триггера, выход которого соединен с выходом каскада и с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с входом каскада и с информационным входом D-триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Измерительное устройство для измерителя группового времени запаздывания | 1989 |

|

SU1620986A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Цифровой фазовращатель | 1986 |

|

SU1394410A1 |

| Преобразователь сдвига фазы в код | 1989 |

|

SU1709524A1 |

| ПРЕОБРАЗОВАТЕЛЬ БИНАРНОГО КОДА В ФАЗОМАНИПУЛИРОВАННЫЙ КОД | 2005 |

|

RU2297096C1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Преобразователь моментов времени в код | 1979 |

|

SU855995A1 |

| Многоканальное устройство для вычисления модульной функции | 1985 |

|

SU1280394A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1677869A2 |

| Устройство для контроля исправности цепей фазовращателя | 1983 |

|

SU1213441A1 |

U0WA2J

f

. ъ

Шиг.2

Авторы

Даты

1992-05-30—Публикация

1989-12-05—Подача