сл

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения периодов следования импульсов при контроле перемещения магнитного носителя | 1989 |

|

SU1647644A1 |

| Многоканальный программируемый аналого-цифровой преобразователь | 1985 |

|

SU1266002A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Частотный преобразователь | 1980 |

|

SU884131A1 |

| Измерительный двухфазный генератор | 1987 |

|

SU1442931A1 |

| Управляемый делитель частоты с дробным коэффициентом деления | 1989 |

|

SU1691959A1 |

| Управляемый делитель частоты с дробным коэффициентом деления | 1989 |

|

SU1677870A1 |

| Устройство задержки | 1984 |

|

SU1202045A1 |

Изобретение относится к импульсной технике. Цель изобретения - повышение надежности устройства за счет его упрощения. Устройство содержит первый, второй и третий регистры 1, 2 и 3 хранения, сумматор 4, первый и второй инверторы 5 и 6, входную шину 7, четвертый регистр 8 хранения и D-триггер 9, третий инвертор 10, первый и второй элементы ИЛИ 11 и 12, первую и вторую шины 13 и 14 записи, первую и вто- рую-информационные шины 15 и 16 и выходную шину 17. 2 ил.

J7

VI СА) VJ VI

ю

XI

Изобретение относится к импульсной технике и может быть использовано в автоматике.

Цель изобретения - повышение надежности устройства за счет его упрощения.

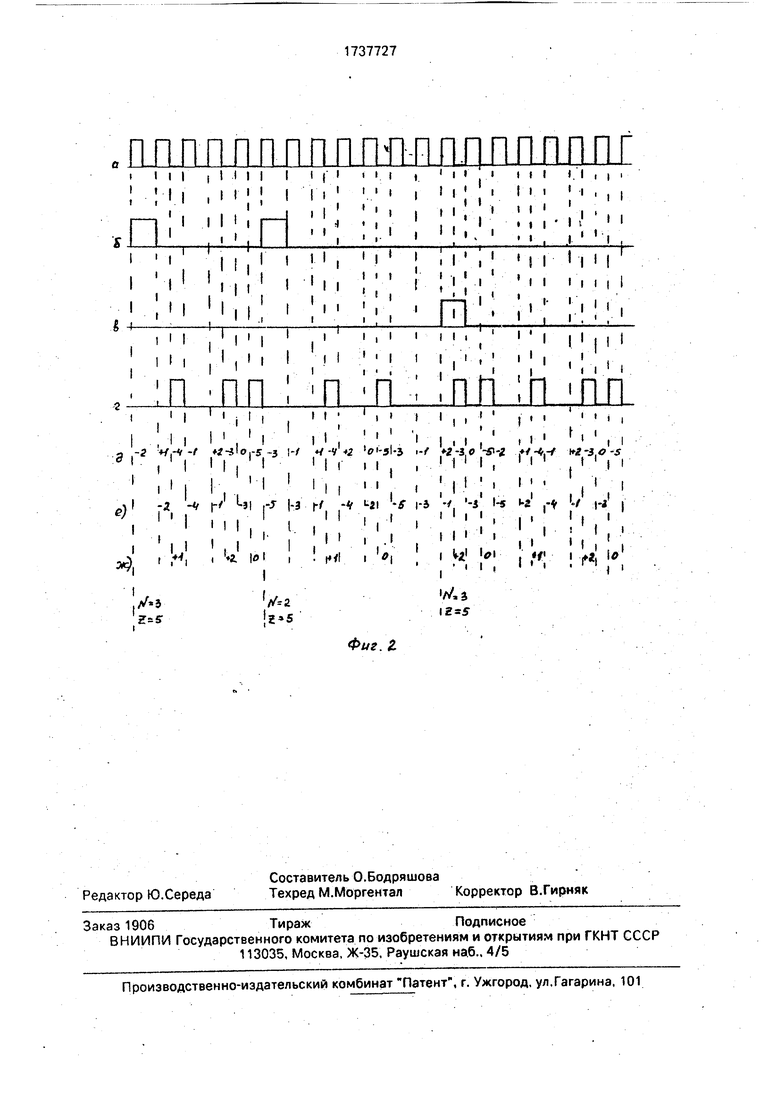

На фиг.1 приведена структурно-электрическая схема устройства; на фиг.2 - временные диаграммы, поясняющие его работу.

Устройство содержит первый, второй и третий регистры 1,2 и 3 хранения, сумматор 4, первый и второй инверторы 5 и 6, входную шину 7, четвертый регистр 8 хранения и D-триггер 9, третий инвертор 10, первый и второй элементы ИЛИ 11 и 12, первую и вторую шины 13 и 14 записи, первую и вторую информационные шины 15 и 16 и выходную шину 17.

Информационные входы первого и второго регистров 1 и 2 соединены с выходами сумматора 4, входы записи - соответственно с входной шиной 7, входом второго инвер- тора 6, вторым входом установки 1 D-триггера 9 и выходом второго инвертора 6, входом синхронизации D-триггера 9, входы считывания - соответственно с выходной шиной 17, выходом D-триггера 9, входом третьего инвертора 10, вторым входом второго элемента ИЛИ 12 и выходом первого инвертора 5. а выходы - соответственно с первой и второй группой входов сумматора 4 и выходами третьего и четвертого регистров 3 и 8, информационные входы которых соединены с первой и второй информационными шинами 15 и 16, входы записи - с выходом первого элемента ИЛИ 11, а входы считывания - соответственно с выходом третьего инвертора 10 и выходом второго элемента ИЛИ 12 и входом первого инвертора 5.

Первый вход второго элемента ИЛИ 12 соединен с первой шиной 13 записи, первым входом установки 1 D-триггера 9 и вторым входом первого элемента ИЛИ 11, первый вход которого соединен с второй шиной 14 записи. Выход старшего разряда сумматора 4 соединен с информационным входом Ь-триггера 9.

На диаграмме на фиг.2 показано следующее: а - импульсы входной частоты; б - импульсы на первой шине 13 записи; в - импульсы на второй шине 14 записи; г - выходные импульсы; д - код на выходе сумматора; е - код на выходе регистра 2 после записи в него данных; ж - код на выходе регистра 1 после записи в него данных.

Управляемый делитель частоты с дробным коэффициентом деления работает следующим образом.

Импульс записи, поступающий по первой шине 13 записи, по длительности равен периоду следования входных импульсов, поступающих по входной шине 7 и синхровизирован, например, положительными фронтами импульсов входной частоты. Импульсом записи переписывается код N по первой информационной шине 15 в регистр 3 и дополнительный код Z по второй инфор0 мационной шине в регистр 8 и одновременно блокируется возможность сброса триггера 9, предотвращая генерацию выходного импульса, что обеспечивает на время действия импульса записи третье со5 стояние по выходу регистра 1 и считывание информации с выхода регистра 3. Импульс записи поступает также на схему ИЛИ 12, обеспечивая третье состояние на выходе регистра 2 и считывание информации с вы0 хода регистра 8. С выхода сумматора 4 код N-Z отрицательным фронтом импульса на выходе инвертора 6 переписывается в регистр 2. После завершения импульса записи вплоть до появления выходного импульса

5 управляемого делителя на первый и второй входы сумматора 4 поступает информация с выходов регистров 3 и 2 соответственно, что обеспечивает в регистре 1, в который информация переписывается отрицательным

0 фронтом импульса входой частоты, накопление кода в соответствии с выражением

,

где At, AM - содержимое регистра 1 в I и 1+1 цикле вычисления.

5 В очередном цикле вычисления, когда на выходе сумматора 4 возникает нулевой

или положительный код, переписываемый по отрицательному фронту в регистр 1, за счет присутствия на D-входе сигнала логи0 ческого нуля триггер 9 по синхровходу сбрасывается, что соответствует формированию выходного импульса устройства, завершаемому установкой триггера 9 по второму входу установки. Генерация выходного импульса

5 устройства сопровождается отключением выходов регистров 3 и 2 от соответственно первого и второго входов сумматора 4 и подключением к ним выходов регистров и 8. На выходе сумматора 4 появляется код,

0 равный величине D-Z, где D - остаток от деления Z на N, содержащийся к этому моменту времени в регистре 1. Код D-Z переписывается отрицательным фронггом сигнала на выходе инвертора 6 в регистр 2.

5 Изменение коэффициента преобразования управляемого делителя частоты, связанное с записью управляющей информации в регистры 3 и 8 при( помощи импульса записи, поступающего в устройство по первой шине 13 записи, одновременно сопряжено с установкой начального состояния, заключающейся в разрешении считывания на входы сумматора 4 выходной информации регистров 3 и 8 и блокировке возможности сброса триггера 9 по синхров- ходу.

В ряде случаев изменение коэффициента преобразования необходимо производить без установки начального состояния. Для этого предусмотрена вторая шина 14 записи, поступающий по которой импульс записи, синхронизированный с импульсами входной частотытак жекак и импульс записи по первой шине 13 записи, вызывает запись в регистры 3 и 8 информации, но не производит установку начального состояния устройства.

Управляемый делитель частоты дроб- ным коэффициентом деления позволяет выполнять преобразование общего вида.

f -Nf

Твых-чт Твх

Формула изобретения

Управляемый делитель частоты с дробным коэффициентом деления, содержащий первый, второй и третий регистры хранения, сумматор, выходы которого соединены с информационными входами первого регистра хранения, первый и второй инверторы, выходы которых соединены соответственно с входами считывания и записи второго регистра хранения, вход второго инвертора

соединен с входной шиной, отличаю щи й- с я тем, что, с целью повышения надежности делителя частоты, в него введены четвертый регистр хранения, D-триггер, третий инвер- тор, первый и второй элементы ИЛИ, первая и вторая шины записи, последняя из которых соединена с первым входом первого элемента ИЛИ, второй вход которого соединен с первым входом второго элемента

ИЛИ, первой шиной записи и первым входом установки единицы D-триггера, а выход - с входами записи третьего и четвертого регистров хранения, информационные входы которых соединены соответственно с

первой и второй информационными шинами, входы считывания - соответственно с выходами инвертора и второго элемента ИЛИ, а выходы - соответственно с первой и

второй группами информационных входов сумматора и выходами первого и второго регистров хранения, информационные входы последнего соединены с выходами сумматора, а вход записи соединен с входом

синхронизации D-триггера, информационный вход которого соединен с выходом старшего разряда сумматора, второй вход установки единицы - с входом второго инвертора и входом записи первого регистра

хранения, а выход - с входной шиной, входом считывания первого регистра хранения, вторым входом второго элемента ИЛИ и входом третьего инвертора, причем выход второго элемента ИЛИ соединен с входом

первого инвертора.

ППЛПППППППЛ-ПП.ППППППГ

//5

. 2

/vU

I

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1298908A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Управляемый делитель частоты с дробным коэффициентом деления | 1984 |

|

SU1274154A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1992-05-30—Публикация

1989-09-05—Подача