ел

4

Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и в синтезаторах частоты.

Цель изобретения - повьш1ени быстродействия.

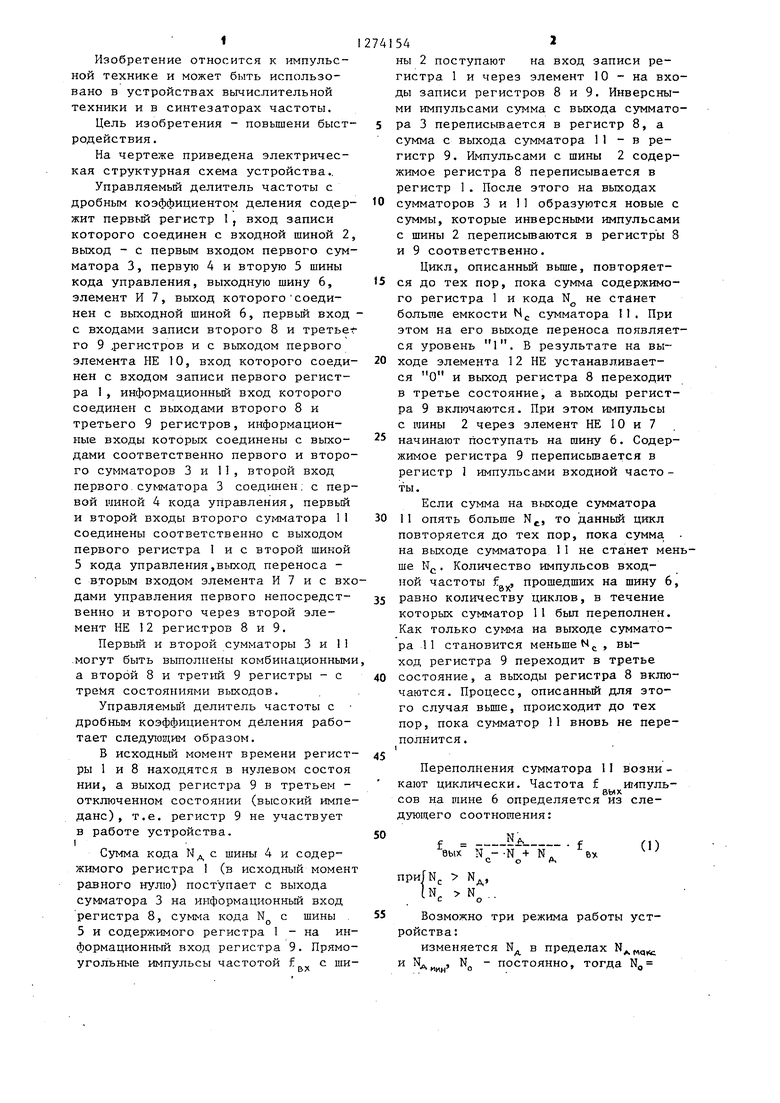

На чертеже приведена электрическая структурная схема устройства..

Управляемый делитель частоты с дробным коэффициентом деления содержит первый регистр 1, вход записи которого соединен с входной шиной 2, выход - с первым входом первого сумматора 3, первую 4 и вторую 5 шины кода управления, выходную шину 6, элемент И 7, выход которогосоединен с выходной шиной 6, первьш вход с входами записи второго 8 и третьег го 9 регистров и с выходом первого элемента НЕ 10, вход которого соединен с входом записи первого регистра I, информационный вход которого соединен с выходами второго 8 и третьего 9 регистров, информационные входы которых соединены с выходами соответственно первого и второго сумматоров 3 и 11, второй вход первого сумматора 3 соединен: с первой шиной 4 кода управления, первьй и второй входы второго сумматора 11 соединены соответственно с выходом первого регистра 1 и с второй шиной 5 кода управления,выход переноса с вторым входом элемента И 7 и с входами управления первого непосредственно и второго через второй элемент НЕ 12 регистров 8 и 9.

Первый и второй сумматоры 3 и 11 .могут быть выполнены комбинационными а второй 8 и третий 9 регистры - с тремя состояниями выходов.

Управляемый делитель частоты с дробным коэффициентом деления работает следующим образом.

В исходный момент времени регистры 1 и 8 находятся в нулевом состоя НИИ, а выход регистра 9 в третьем отключенном состоянии (высокий импеданс) , т.е. регистр 9 не участвует

в работе устройства.

I

Сумма кода 1д с шины 4 и содержимого регистра 1 (в исходный момент равного нулю) поступает с выхода сумматора 3 на информационный вход регистра 8, сумма кода N с шины . 5 и содержимого регистра 1 - на информационный вход регистра 9. Прямоугольные импульсы частотой f с шиВл

542

ны 2 поступают на вход записи регистра 1 и через элемент 10 - на входы записи регистров 8 и 9. Инверсными импульсами сумма с выхода сумматора 3 переписывается в регистр 8, а сумма с выхода сумматора 11 - в регистр 9. Импульсами с шины 2 содержимое регистра 8 переписывается в регистр I. После этого на выходах сумматоров 3 и 1 образуются новые с суммы, которые инверсными импульсами с шины 2 переписываются в регистры 8 и 9 соответственно.

Цикл, описанный вьшге, повторяется до тех пор, пока сумма содержимого регистра 1 и кода N не станет больше емкости N. сумматора П. При этом на его выходе переноса появляется уровень 1. В результате на выходе элемента 12 НЕ устанавливается О и выход регистра 8 переходит в третье состояние, а выходы регистра 9 включаются. При этом импульсы с шины 2 через элемент НЕ IО и 7 начинают поступать на шину 6. Содержимое регистра 9 переписьшается в регистр 1 импульсами входной часто ты.

Если сумма на выходе сумматора 11 опять больше N, то данньш цикл повторяется до тех пор, пока сумма. на выходе сумматора 11 не станет менше N, . Количество импульсов входной частоты f,, , прошедших на шину 6

&х равно количеству циклов, в течение

которых сумматор 11 был переполнен. Как только сумма на выходе сумматора 11 становится меньшеN , выход регистра 9 переходит в третье состояние, а выходы регистра 8 включаются. Процесс, описанный для этого случая вьппе, происходит до тех пор, пока сумматор П вновь не переполнится . I

Переполнения сумматора 11 возни кают циклически. Частота f иппуль,вых

сов на шине 6 определяется из следуюш;его соотношения:

N.

..

(1)

N - -N + N .,

ВУ

с о А,

приГН Нд, Ь, N..

Возможно три режима работы устройства:

изменяется N в пределах N и N , Ng - постоянно, тогда Ng fnu, имеет нелинейную A Ma зависимость; изменяется N в пределах N и мм°о макс оиин в ПОСТОЯННО, при ЭТОМ N. Ы„- N и „ имеет обратно про Л с Омчкс 6Ь1Х порциональную зависимость от N ; изменяя одновременно и N в функции времени, можно получить пра тически любую нелинейную зависиF (N N,) в том числе и мость f. линейную. Емкость сумматора 3 и 1 1 необходимо брать равной 2Ng. Во-первых, чтобы исключить потерю информации в сумматоре 3 в случае, когда сумма н его выходе будет больше (Ч. Во-вторы в сумматоре 11 в качестве выхода пе носа используется старший (дополнительный) разряд. Формула изобретени 1.Управляемьй делитель частоты с дробным коэффициентом деления, содержащий первый регистр, вход зап си которого соединен с входной шино выход - с первым входом первого сум матора, первую гаину кода управления и выходную шину, отличающи с я тем, что, с целью повышения быстродействия, в него введены вторая шина кода управления, второй 1544 сумматор, второй и третий регистры, первьш и второй элементы НЕ и элемент И, выход которого соединен с выходной шиной, первый вход - с входами записи второго и третьего регистров и с выходом первого элемента НЕ, вход которого соединен с входом записи первого регистра, информационньй вход которого соединен с выходами второго и третьего регистров, информационные входы которых соединены с выходами соответственно первого и второго сумматоров, причем второй вход первого сумматора соединен с перЗой шиной кода управления, первый и второй входы второго сумматора соединены соответственно с вьпходом первого регистра и с второй шиной кода управления, выход переноса - с вторым входом элемента И и с входами управления первого непосредственно и второго через второй элемент НЕ регистров. 2,Устройство по п,1, о т л и чающееся тем, что первый и второй сумматоры выполнены комбинационными. 3.Устройство по п.1, отличающееся тем, Что второй и третий регистры выполнены, с тремя состояниями выходов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1988 |

|

SU1532921A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 2002 |

|

RU2210102C1 |

| Частотный преобразователь | 1980 |

|

SU884131A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ БЫСТРЫХ ГЕОМЕТРИЧЕСКИХ ПРЕОБРАЗОВАНИЙ | 1991 |

|

RU2020557C1 |

| Управляемый делитель частоты с дробным коэффициентом деления | 1989 |

|

SU1737727A1 |

| Многоканальный анализатор электрофизиологических сигналов | 1991 |

|

SU1806603A1 |

| Накапливающий сумматор | 1987 |

|

SU1499335A1 |

| Преобразователь частоты в код | 1978 |

|

SU744977A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и в синтезаторах частоты. Цель изобретения - повышение быстродействия. Устройство содержит регистры l,8 и 9, входную шину 2, сумматоры 3 и 11, шины 4 и 5 кода управления , выходную ШИКУ 6, элемент 7 И и элемент 10 и 12 НЕ. Сумматоры 3 и 11 могут быть выполнены комбинационными, а регистры 8 и 9 с тремя состояниями выходов. 2 з.п. ф-лы, 1 ил.

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1978 |

|

SU669487A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Каскад цифрового накопителя | 1983 |

|

SU1140249A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-11-30—Публикация

1984-10-04—Подача