ел

00

О

ОС

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования адресов буферной памяти | 1986 |

|

SU1434495A1 |

| Устройство для формирования адресов буферной памяти | 1986 |

|

SU1510009A1 |

| Устройство для автоматического установления соединений и обмена сообщениями | 1989 |

|

SU1737760A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Микропроцессор | 1985 |

|

SU1330634A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1837305A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Коммутатор | 1989 |

|

SU1716622A2 |

Изобретение относится к вычислительной технике и может быть использовано в блоках буферной памяти для устройств приемопередачи данных по уплотненным линиям связи в устройствах автоматического установления соединения в системах автоматической коммутации, а также в качестве многоканального счетчика. Цель изобретения - упрощение устройства и расширение области его применения за счет увеличения разрядности формируемых адресов и для создания многоканальных счетчиков. Устройство содержит блок 1 памяти, арифметико-логический блок 2, регистр 3, элемент И 4, первый 5 и второй 6 счетчик, мультиплексор 7 и формирователь 8 управляющих сигналов. 1 табл., 5 ил.

Л ue.f

Изобретение относится к вычислительной технике и может быть использовано в блоках буферной памяти для устройств при- емопередачи данных по уплотненным линиям связи в устройствах автоматического установления соединений в системах автоматической коммутации с распределенным управлением, а также в качестве многоканального счетчика.

Цель изобретения - упрощения устройства и расширение области его применения за счет увеличения разрядности формируемых адресов.

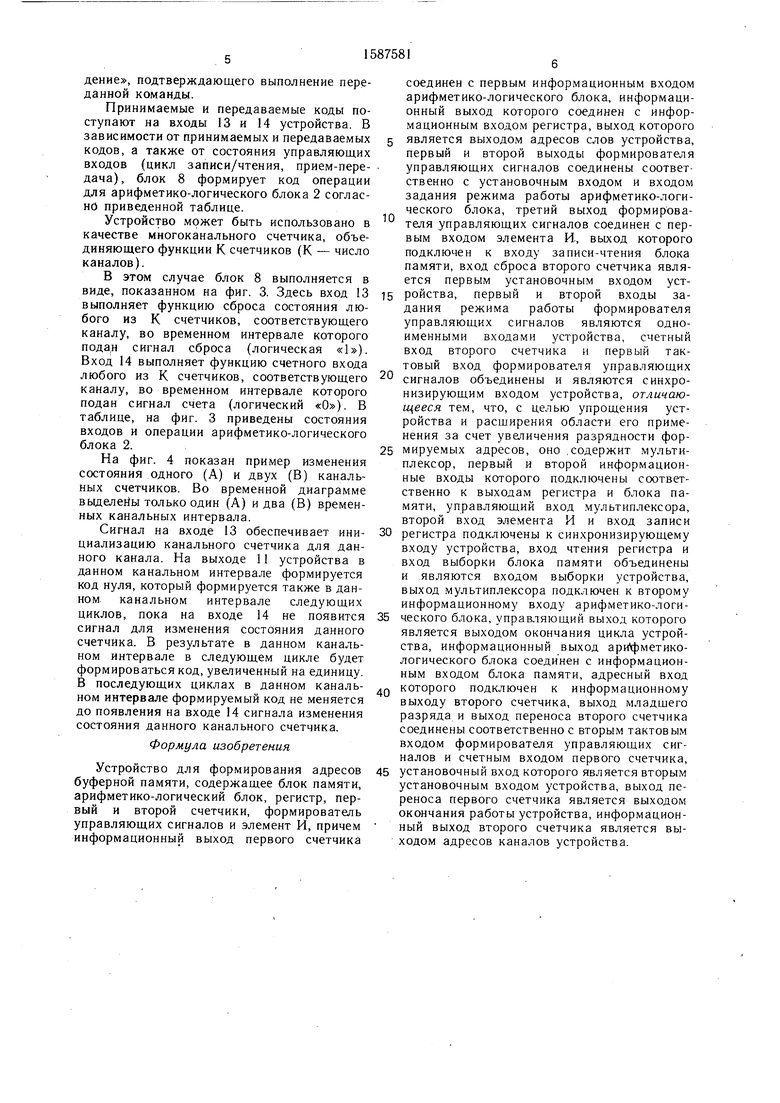

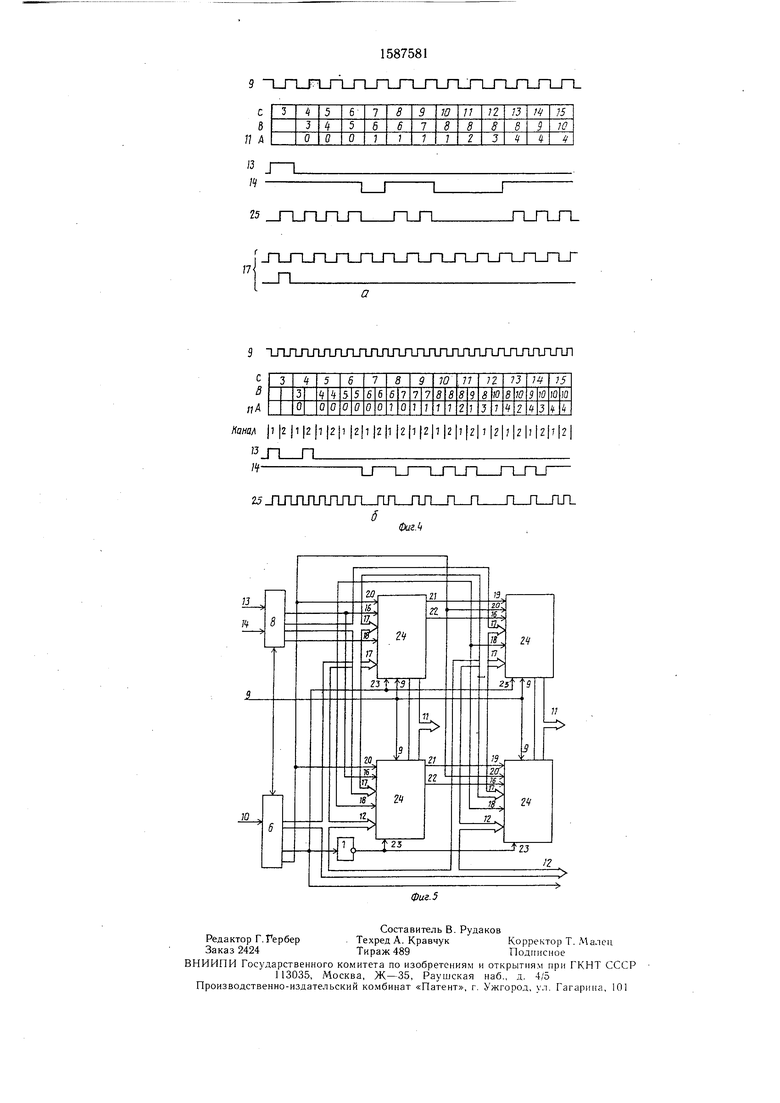

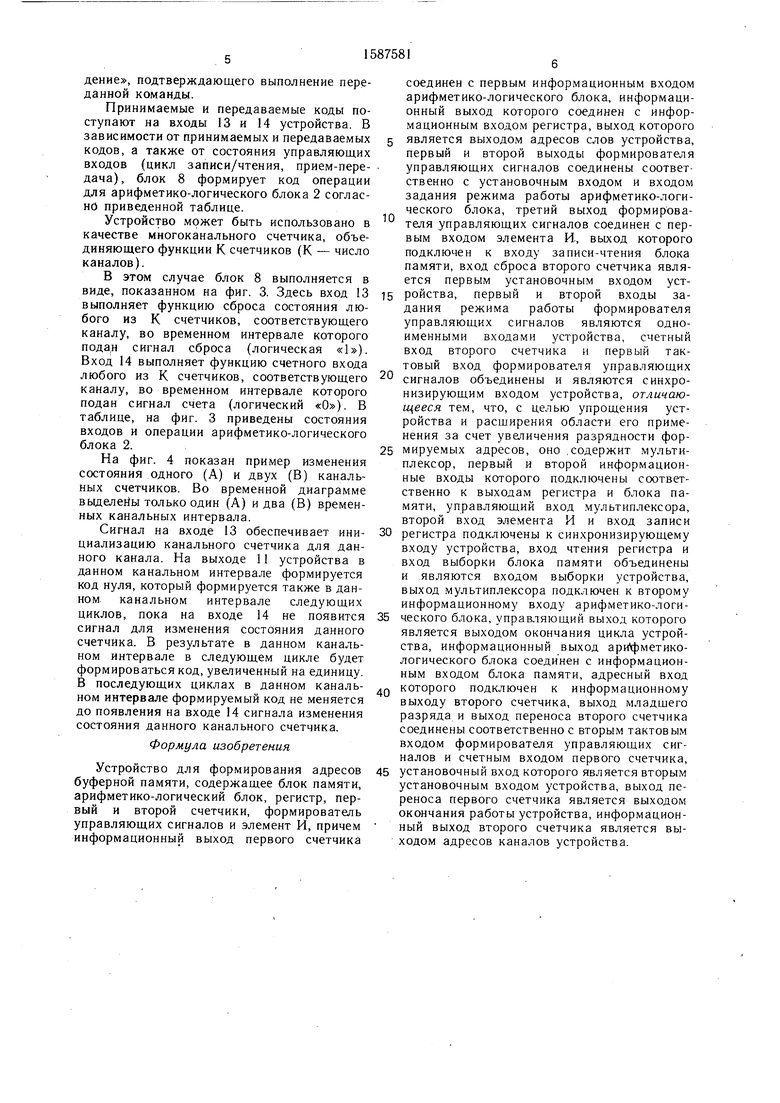

На фиг. 1 изображена блок-схема устройства; на фиг. 2 - временная диаграмма работы устройства; на фиг. 3 - функциональная схема формирователя управляющих сигналов при использовании устройства в качестве многоканального счетчика, таблица состояний входо-выходов и операции арифметико-логического блока; на фиг. 4 - временная диаграмма работы устройства в качестве многоканального счетчика, состояния счетчиков и операции арифметико-логического блока для одного (А) и двух (В) каналов; на фиг. 5 - пример каскадного включения устройств.

Устройство содержит блок 1 памяти, арифметико-логический блок 2, регистр 3, элемент И 4, первый 5 и второй 6 счетчики, мультиплексор 7, формирователь 8 управляющих сигналов.

На фиг. 1 обозначены: синхронизирующий вход 9, первый установочный вход 10, выход 11 адресов слов, выход 12 адресов каналов, первый 13 и второй 14 входы задания режима работы устройства, выход 15 младшего разряда счетчика, выходы 16 - 18 формирователя, второй установочный вход 19 устройства, счетный вход 20 счетчика 5, выходы окончания работы 21 и цикла 22 устройства, вход 23 выборки устройства. Блоки 1-5 и 7 образуют блок 24 вычисления адресов. Кроме того, на фиг. 1 обозначен вход 25 записи-считывания блока 1 памяти.

Разрядность счетчика 6 определяется из числа канальных интервалов во всех приемных и всех передающих трактах. При одном приемном и одном передающем тракте разрядность счетчика равна 6 (32 канала в каждом тракте). При двух приемных и двух передающих трактах разрядность счетчика равна 7.

Разрядность счетчика 5 определяется из максимальной длины пакета сообщения. При максимальной длине пакета сообщения 64 слова счетчик 5, как и блок 1 памяти, имеет разрядность, равную 6.

Счетчик 5 предназначен для формирования текущего отсчета с целью вычисления текущих адресов и изменяет свое состояние при переходе счетчика 6 в нулевое состояние. Блок 1 памяти предназначен

5

5

5

для записи и хранения относительных отсчетов для всех каналов всех трактов. При общем числе каналов, равном 128, емкость блока 1 памяти равна 128 слов. с Счетчик 6 формирует адрес области буферной памяти (номер канала).

Вычисление текущих адресов осуществляет арифметико-логический блок 2. Операция блока 2 формируется блоком 8 и зависит от состояния входов 13 и 14 устрой0 ства. В таблице приведен пример операций блока 2 при различных состояниях входов 13 и 14, на которые подаются коды принимаемых и передаваемых данных. Здесь С - состояние счетчика 5; В - состояние выхода блока 1 памяти; А - состояние выхода регистра 3. Коды задаются состоянием четырех старших разрядов данных и разделяют передаваемые и принимаемые данные на команды, сообщения и т.д.

В циклах чтения блок 2 выполняет

0 операцию над состоянием счетчика 5 и состоянием выхода блока 1 памяти. В циклах записи блок 2 выполняет операцию над состоянием счетчика 5 и состоянием регистра 3.

В исходном состоянии в циклах записи в блок 1 памяти постоянно записывается состояние счетчика 5 и обеспечивается самоинициализация устройства. Импульс записи проходит через элемент И 4 на вход записи-чтения блока 1 памяти. В циклах чтения из блока 1 памяти считывается значение, записанное в, блок 1 памяти в том же канальном интервале предыдущего цикла. В этом случае блок 2 выполняет операцию С-В-1, в результате чего в регистр 3 загружается и на выходе 11 устройства

5 для всех каналов формируется код нуля (в этом случае ).

При поступлении по любому из каналов пакета сообщения, начинающегося кодом «Начало и заканчивающегося кодом «Ко- нец устройство в соответствующем канале обеспечивает последовательное увеличение текущего адреса на единицу. При поступлении кода «Начало устройство формирует код «О, при поступлении первого слова сообщения - код «1, при поступлении второго слова сообщения - код «2 и т.д. При передаче пакета сообщения устройство последовательно увеличивает значение текущего адреса на единицу для соответствующего канала. Передача кода «Конец вызывает инициализацию текущего адреса путем разрешения записи в блок 1 памяти состояния счетчика 5.

В режиме передачи команд после вывода одной команды изменение текущего адреса для соответствующего канала . не производится. А в буферной памяти команда заменяется на код «Речь/данные. Увеличение текущего адреса на единицу осуществляется лишь при поступлении по соответствующему приемному каналу кода «Подтверж0

0

5

управляющих сигналов соединены соответственно с установочным входом и входом задания режима работы арифметико-логического блока, третий выход формировадение, подтверждающего выполнение пере- соединен с первым информационным входом данной команды. арифметико-логического блока, информаци- Принимаемые и передаваемые коды по- онный выход которого соединен с инфор- ступают на входы 13 и 14 устройства. В мационным входом регистра, выход которого зависимости от принимаемых и передаваемых 5 является выходом адресов слов устройства, кодов, а также от состояния управляющих первый и второй выходы формировате/тя входов (цикл записи/чтения, прием-передача), блок 8 формирует код операции для арифметико-логического блока 2 согласно приведенной таблице.

Устройство может быть использовано в теля управляющих сигналов соединен с пер- качестве многоканального счетчика, объе-вым входом элемента И., выход которого

диняющего функции К счетчиков (К - числоподключен к входу записи-чтения блока

каналов).памяти, вход сброса второго счетчика являВ этом случае блок 8 выполняется вется первым установочным входом уствиде,показанном на фиг. 3. Здесь вход 13 15 ройства, первый и второй входы за- -Дания режима работы формирователя

управляющих сигналов являются одноименными входами устройства, счетный вход второго счетчика и первый так. -.товый вход формировататя управляющих

любого из К счетчиков, соответствующего 20 сигналов объединены и являются синхро- каналу, во временном интервале которогонизирующим входом устройства, отличающееся тем, что, с целью упрощения устройства и расширения области его применения за счет увеличения разрядности фор- 25 мируемых адресов, оно ,содержит мультиплексор, первый и второй информационные входы которого подключены соответственно к выходам регистра и блока памяти, управляющий вход мультиплексора,

.второй вход элемента И и вход записи

Сигнал на входе 13 обеспечивает ини- 30 регистра подключены к синхронизирующему циализацию канального счетчика для дан-входу устройства, вход чтения регистра и

ного канала. На выходе 11 устройства ввход выборки блока памяти объединены

данном канальном интервале формируетсяи являются входом выборки устройства,

код нуля, который формируется также в дан-выход мультиплексора подключен к второму

ном- канальном интервале следующихинформационному входу арифметико-логициклов, пока на входе 14 не появится 35 ческого блока, управляющий выход которого сигнал для изменения состояния данногоявляется выходом окончания цикла устройства, информационный выход ариУ метико- логического блока соединен с информацион - -...,ным входом блока памяти, адресный вход

В последующих циклах в данном каналь-которого подключен к информационному

ном интервале формируемый код не меняетсявыходу второго счетчика, выход младщего

разряда и выход переноса второго счетчика соединены соответственное вторым тактовым входом формирователя управляющих сигналов и счетным входом первого счетчика, Устро йство для формирования адресов 45 установочный вход которого является вторым буферной памяти, содержащее блок памяти,установочным входом устройства, выход пеарифметико-логический блок, регистр, пер-реноса первого счетчика является выходом

вый и второй счетчики, формировательокончания работы устройства, информационуправляющих сигналов и элемент И, причем ный выход второго счетчика является вы- информационный выход первого счетчикаходом адресов каналов устройства.

выполняет функцию сброса состояния любого из К счетчиков, соответствующего каналу, во временном интервале которого пода,н сигнал сброса (логическая «1). Вход 14 выполняет функцию счетного входа

подан сигнал счета (логический «О). В таблице, на фиг. 3 приведены состояния входов и операции арифметико-логического блока 2.

На фиг. 4 показан пример изменения состояния одного (А) и двух (В) канальных счетчиков. Во временной диаграмме выделены только один (А) и два (В) временных канальных интервала.

счетчика. В результате в данном канальном интервале в следующем цикле будет формироваться код, увеличенный на единицу.

до появления на входе 14 сигнала изменения состояния данного канального счетчика.

Формула изобретения

управляющих сигналов соединены соответственно с установочным входом и входом задания режима работы арифметико-логического блока, третий выход формировасоединен с первым информационным входом арифметико-логического блока, информаци- онный выход которого соединен с инфор- мационным входом регистра, выход которого является выходом адресов слов устройства, первый и второй выходы формировате/тя

теля управляющих сигналов соединен с пер- вым входом элемента И., выход которого

70 J L

I i- - -njiJTJiJTnj Jb лтгитл

Канал

О 7

npuet fibiu I Передающий канал нанал

Цикл Цикл чтения записи

JL П

ЧИ

11

18

Фиг.З

31 О 7

13 j-L w

17

J1.

3 ъпJггlJггuгrlЛJгrLЛJтгlЛJ Jгr JlJ

КанпА i 2 IT

25лг1ггшлллл лп лл г пп п гиь

| Устройство для формирования адресов буферной памяти | 1986 |

|

SU1434495A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для формирования адресов буферной памяти | 1986 |

|

SU1510009A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-08-23—Публикация

1987-12-24—Подача