е 8ых

Изобретение относится к области техники хранения цифровой информации и может быть использовано в оптических внешних запоминающих устройствах (ВЗУ) с дисковым носителем информации.

В подобных устройствах длина пути перемещения определяется количеством позиционных интервалов, подсчитываемых при движении позиционирующего механизма. Основными требованиями, предъявляемыми к позиционирующим механизмам при использовании в ВЗУ, являются точность и быстродействие, которые удовлетворяются путем выбора оптимального закона управления.

В устройствах с так называемым треугольным законом управления скорость равноускоренного (равнозамедленного) движения позиционирующего механизма определяется выражением

V- v2aS,(1)

где а - численное значение ускорения (замедления) при движении

S - текущее значение длины пути разгона или торможения.

Так как для данного закона движения а const, то выражение (1) может быть представлено в виде

V К (2)

где К V2a .

Из выражения (2) следует, что для обеспечения равноускоренного движения позиционирующего механизма управляющее воздействие должно регулироваться по закону

U К VS.(3)

Известно устройство, обеспечивающее формирование сигнала управления скоростью в соответствии с выражением(3), которое содержит цифроаналоговый преобразователь цифрового кода, вес которого равен величине требуемого перемещения позиционирующего механизма и функциональный преобразователь, обеспечивающий преобразование выходного сигнала цифроаналогового преобразователя по закону

VUBX((4)

где UBX выходное напряжение ЦАП, пропорциональное величине требуемого перемещения позиционирующего механизма;

К- коэффициент, характеризующий параметры движения (конкретные для определенного устройства скорость и ускорение).

В указанном устройстве формирование сигнала управления скоростью осуществляется преобразователем, работающим в аналоговом режиме. Использование этого режима снижает точность формирования

сигнала управления скоростью и надежность работы устройства вследствие того, что преобразователю присущи недостатки аналоговой техники, а именно дрейф нулевого уровня, восприимчивость к температурным условиям и флуктуациям напряжения электропитания и т.д.

Известно также устройство, которое содержит последовательно соединенные преобразователь кодов и цифроаналоговый преобразователь. В устройстве осуществляется формирование цифрового сигнала управления скоростью с последующим преобразованием в напряжение. В процессе работы данного устройства на вход преобразователя кодов поступает цифровой код числа М, соответствующий величине перемещения позиционирующего механизма. Код М преобразуется в код N по закону

N К VM, (5)

где К - коэффициент увеличения разрядности.

Данное устройство позволяет значительно повысить точность формирования

сигнала управления скоростью и надежность работы устройства за счет сокращения количества элементов аналоговой схемотехники.

Недостатком устройства является то,

что на участке разгона параметры движения позиционирующего механизма не контролируются, а движение в соответствии с оптимальным законом скорости поддерживается только на участке торможения.

Разгон осуществляется подачей на исполнительный механизм максимального по амплитуде напряжения, соответствующего максимальной скорости позиционирования. Возникающее при этом перерегулирование снижает точность работы системы позиционирования. Значительные по величине перепады ускорения, возникающие в фазе разгона, приводят к необходимости усложнения конструкции позиционирующего

механизма.

Наиболее близким по технической сущности к предлагаемому является устройство для формирования скорости движения позиционирующего механизма, содержащее

блок управления, включающий последовательно соединенные блок счетчика разности и задатчик скорости перемещения, цифроаналоговый преобразователь.

Известное устройство позволяет осуществить управление скоростью позиционирующего механизма при разгоне с использованием принципа обратной связи, что позволяет осуществлять разгон и торможение каретки позиционирующего механизма в соответствии с выбранным оптимальным законом управления. Плавный разгон каретки позволяет устранить значительные по амплитуде скачки ускорения и вызванные этими скачками механические удары, что приводит к повышению точности работы устройства позиционирования.

Недостатком известного устройства является то, что реализация оптимального закона управления приводит к увеличению временных затрат при формировании блоком управления дискретных значений кодов скорости, что приводит к снижению быстродействия всего устройства.

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство для формирования сигналов скорости движения позиционирующего механизма, содержащее блок формирования управляющих сигналов, вход которого соединен с внешней шиной разности адресов, цифроаналоговый преобразователь, выходную шину, внешние шины занесения разности адресов и декремента разности адресов, введены блок оперативного запоминающего устройства и блок прямого доступа к памяти. Первый и второй управляющие входы блока прямого доступа к памяти соединены соответственно с шинами занесения разности адресов и декремента разности адресов. Выход блока прямого доступа к памяти подключен через цифроаналоговый преобразователь к выходной шине. При этом блок формирования управляющих сигналов выполнен в виде связанных между собой двунаправленными шинами микропроцессора, постоянного запоминающего устройства и блок ввода-вывода. Вход блока ввода-вывода является входом блока формирования управляющих сигналов, выходы которого, являющиеся выходами микропроцессора, связаны двунаправленными шинами с входами блока оперативного запоминающего устройства и блока прямого доступа к памяти.

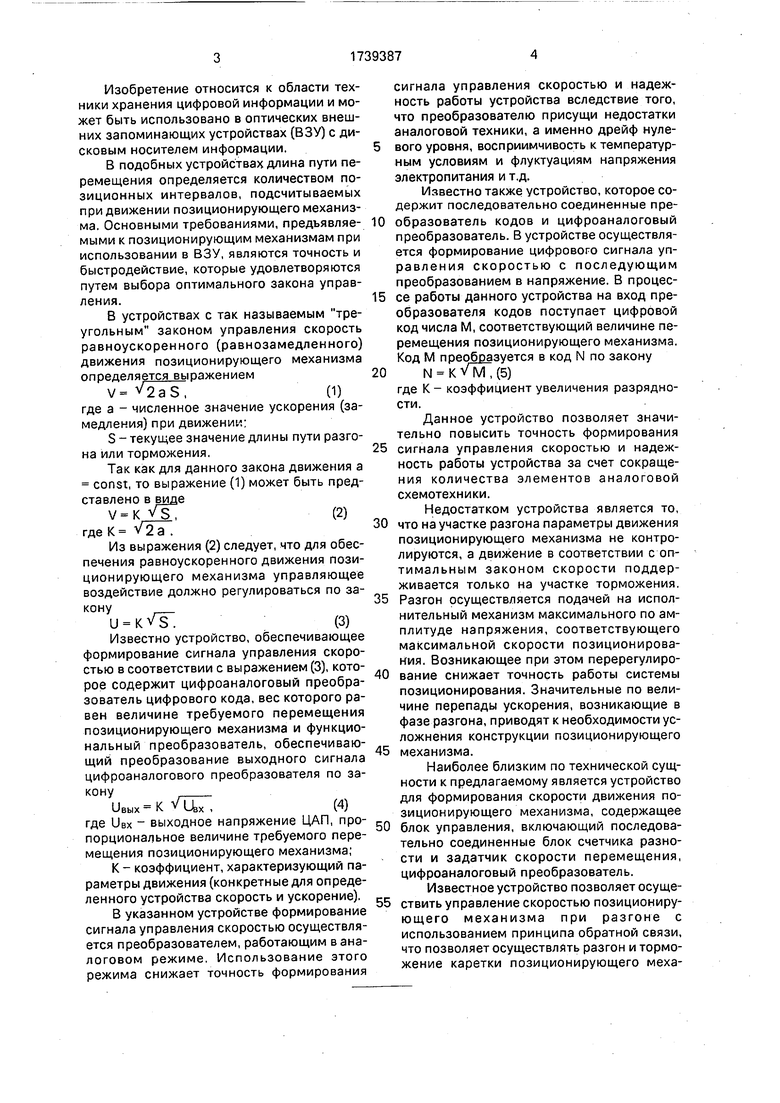

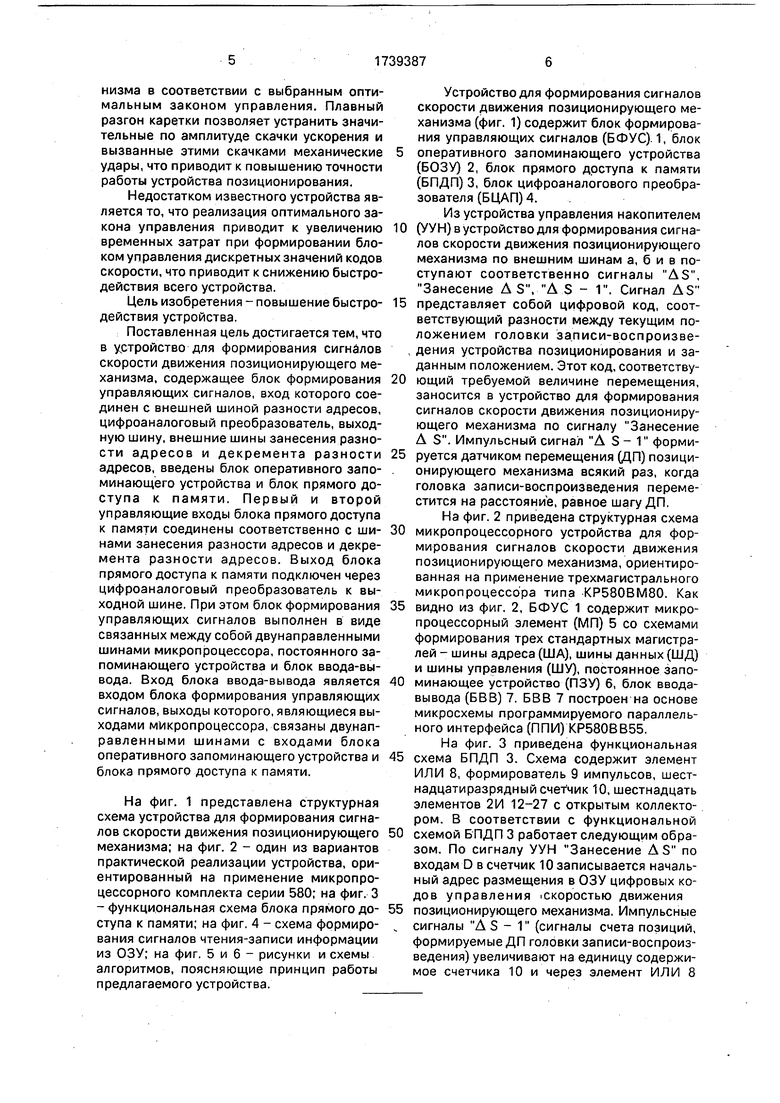

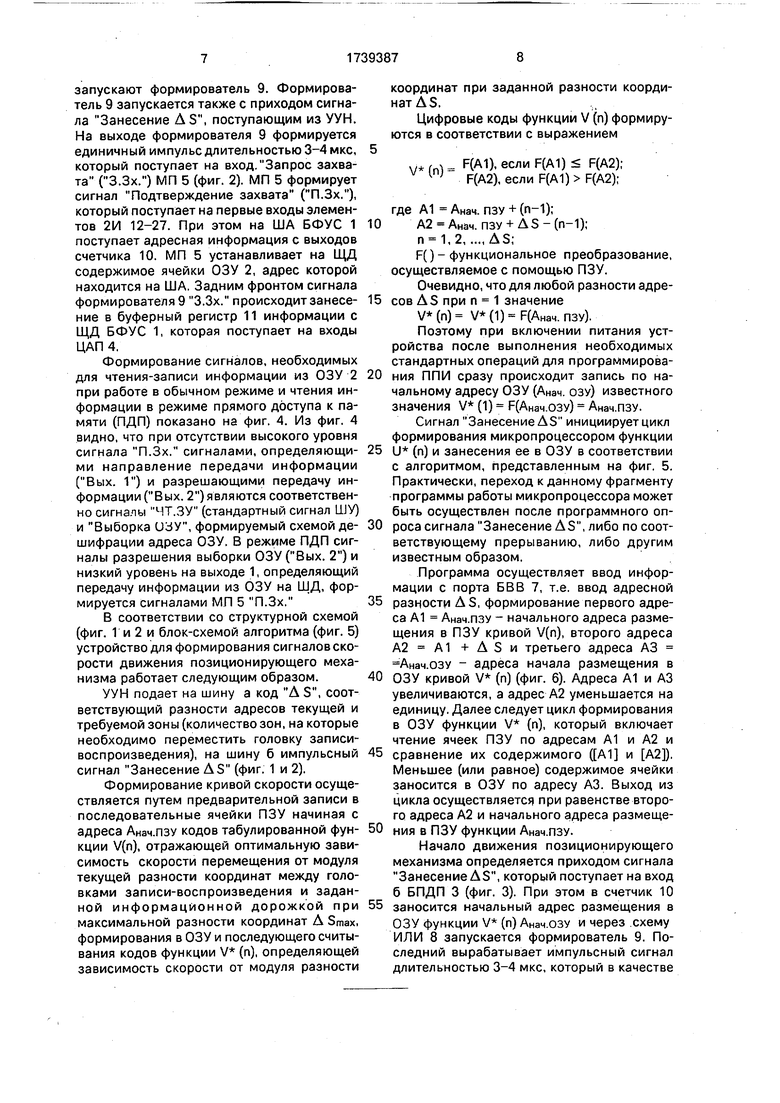

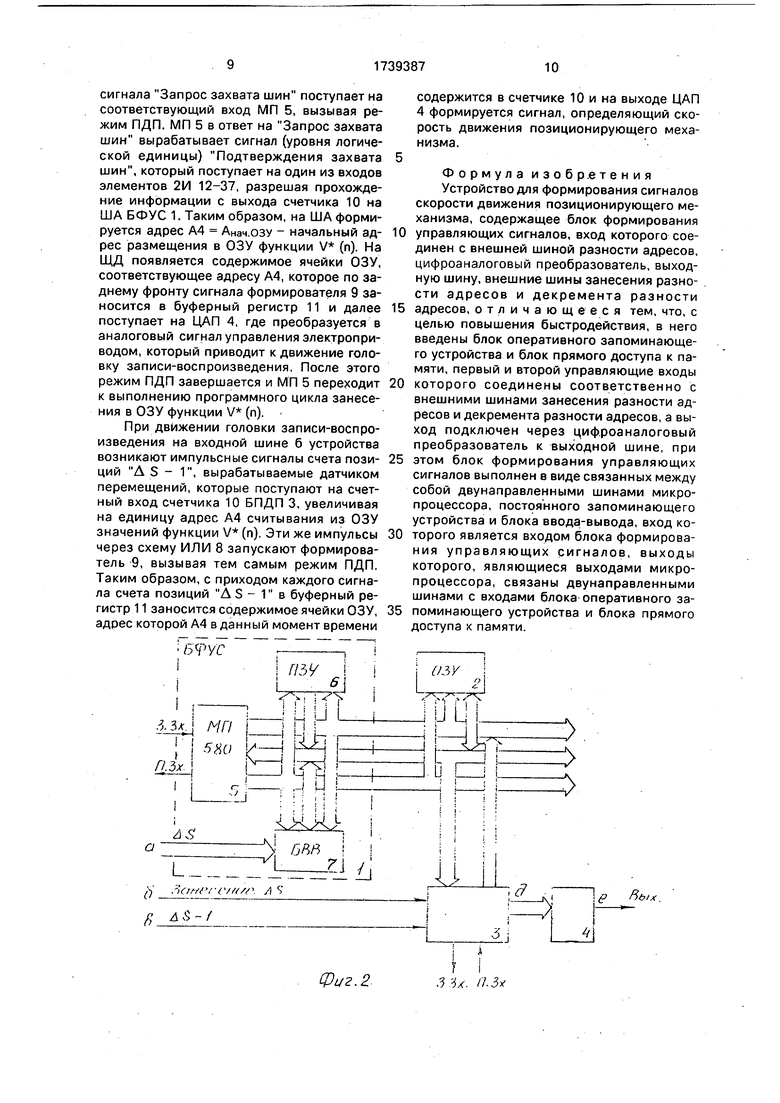

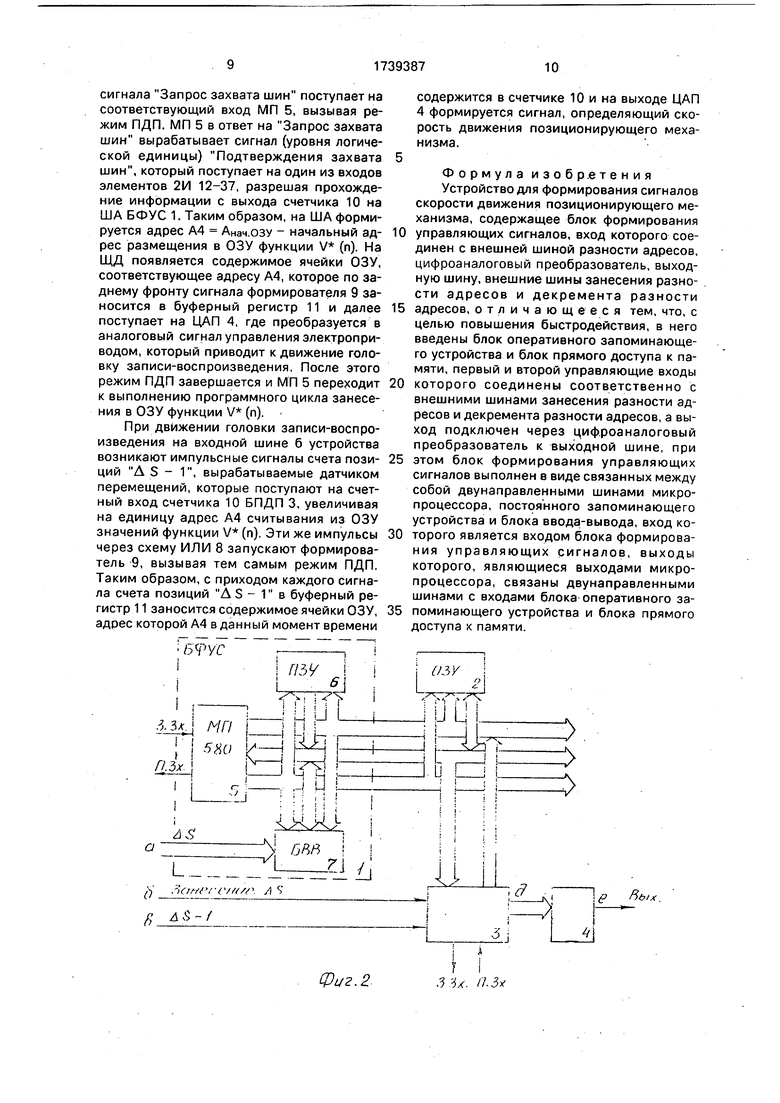

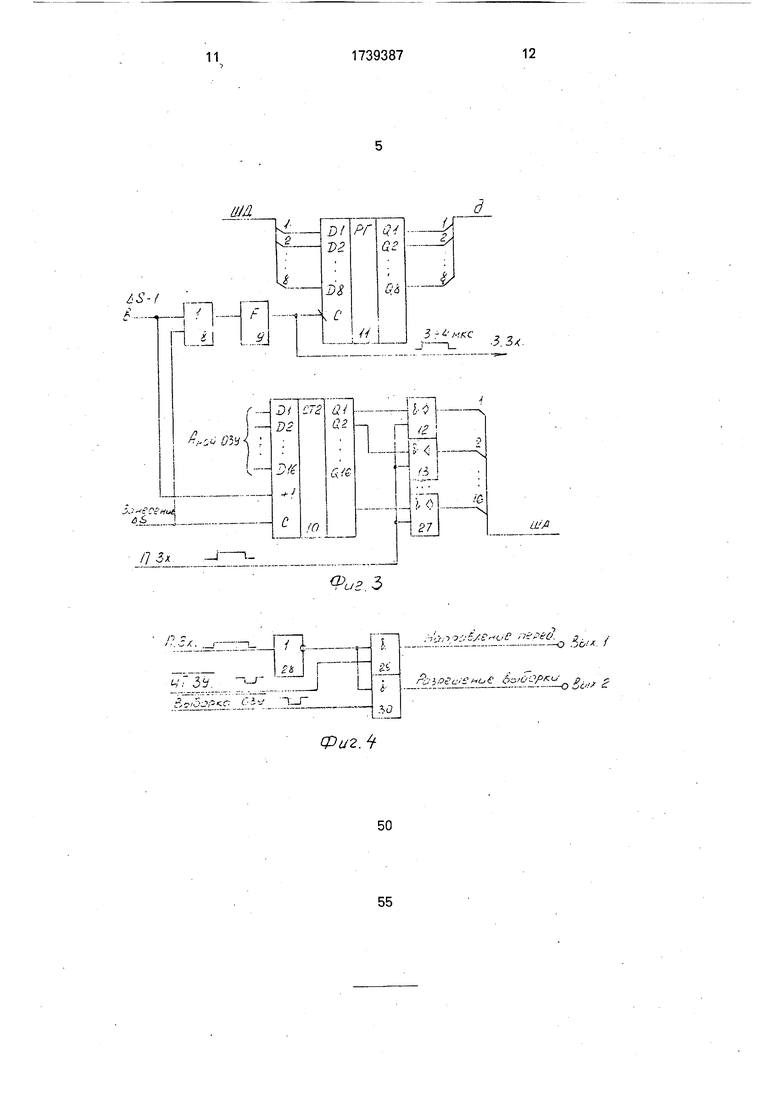

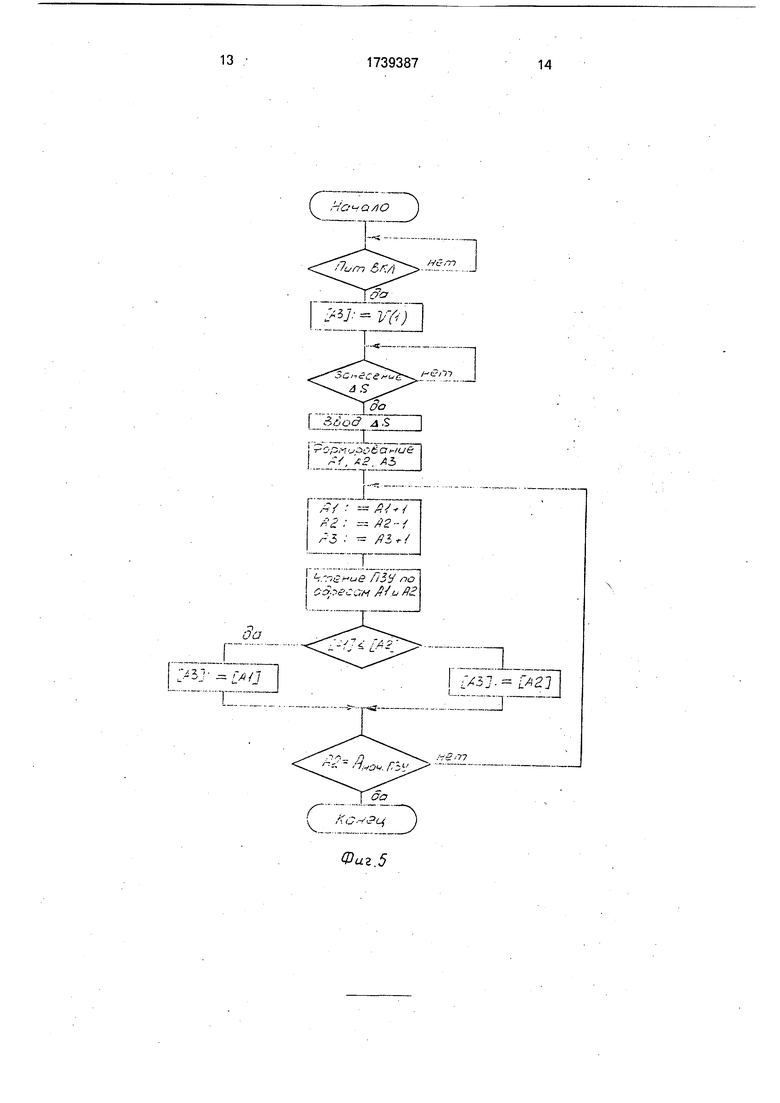

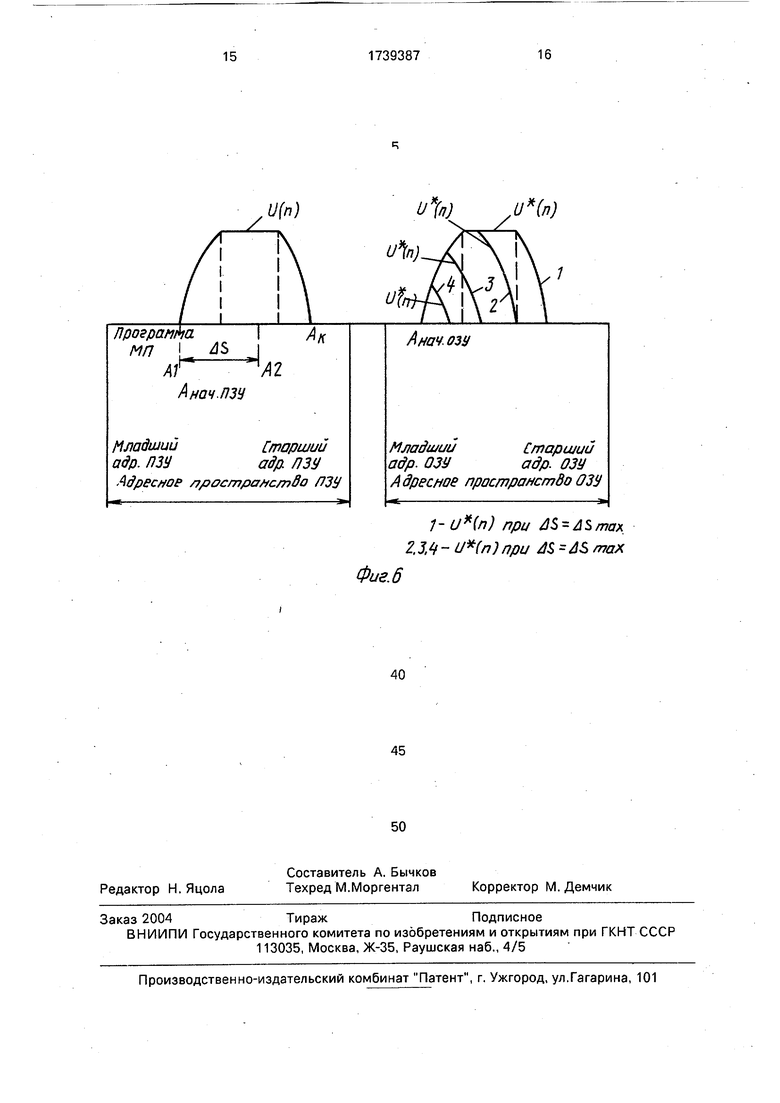

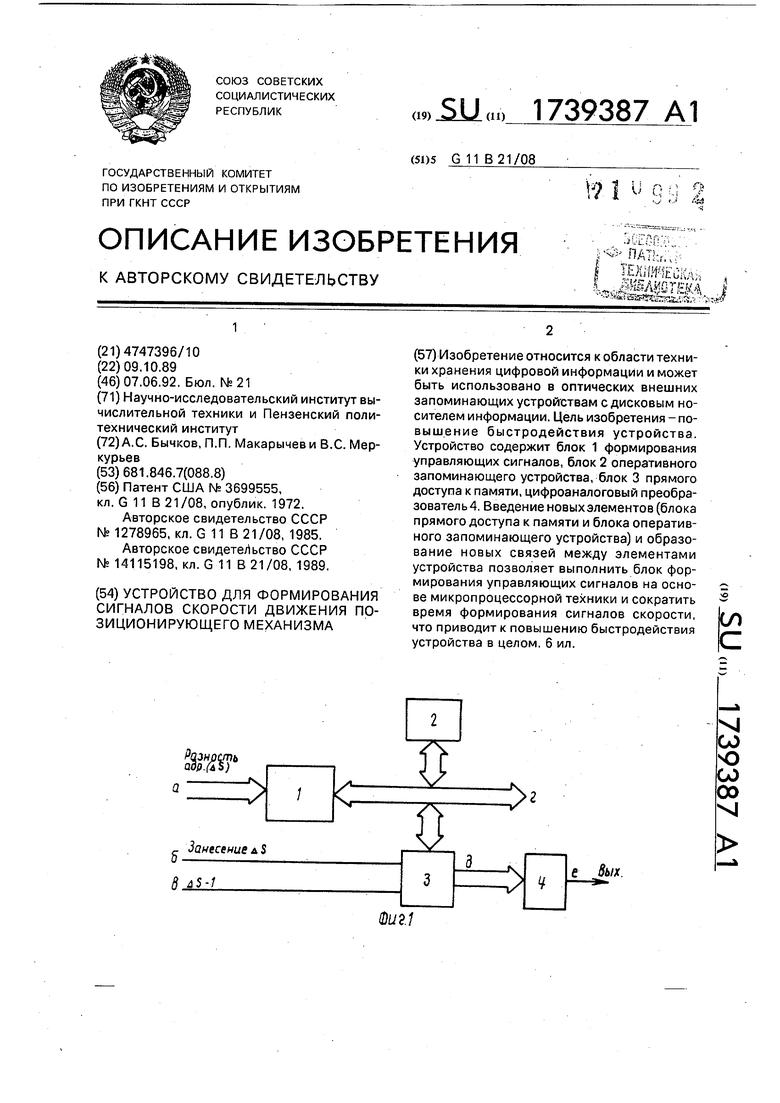

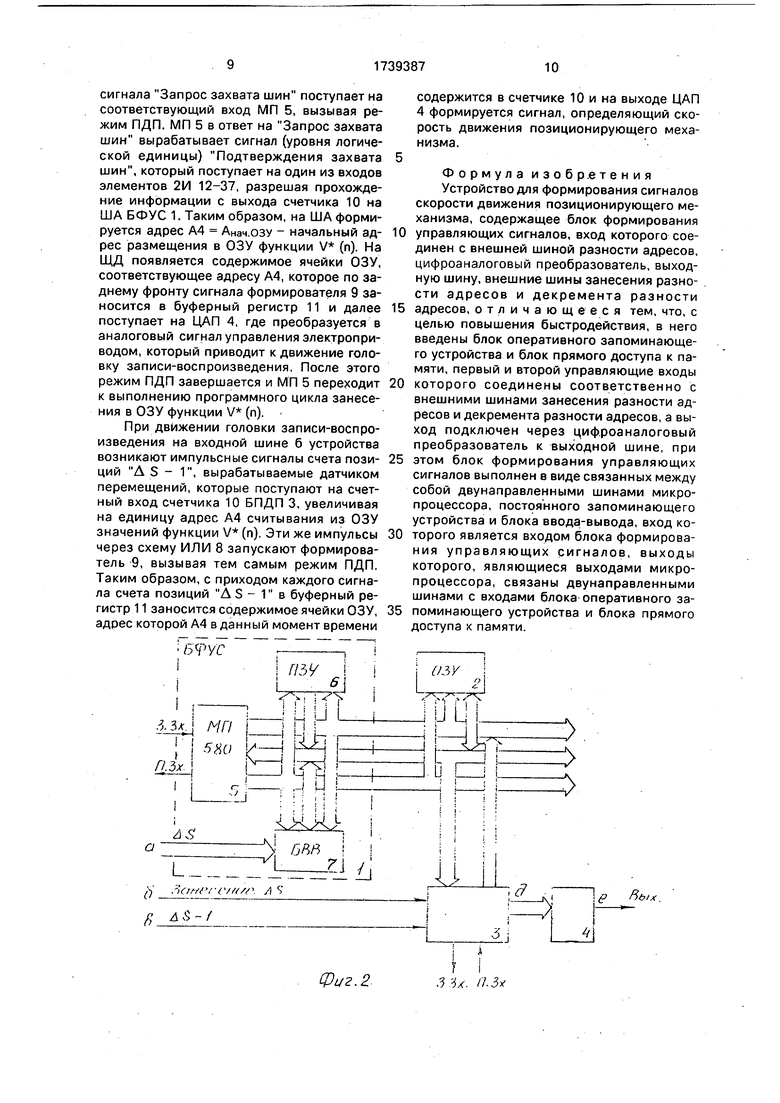

На фиг. 1 представлена структурная схема устройства для формирования сигналов скорости движения позиционирующего механизма; на фиг. 2 - один из вариантов практической реализации устройства, ориентированный на применение микропроцессорного комплекта серии 580; на фиг. 3 - функциональная схема блока прямого доступа к памяти; на фиг. 4 - схема формирования сигналов чтения-записи информации из ОЗУ; на фиг. 5 и 6 - рисунки и схемы алгоритмов, поясняющие принцип работы предлагаемого устройства.

Устройство для формирования сигналов скорости движения позиционирующего механизма (фиг. 1) содержит блок формирования управляющих сигналов (БФУС) 1, блок

оперативного запоминающего устройства (БОЗУ) 2, блок прямого доступа к памяти (БПДП) 3, блок цифроаналогового преобразователя (БЦАП) 4.

Из устройства управления накопителем

(УУН) в устройство для формирования сигналов скорости движения позиционирующего механизма по внешним шинам а, б и в поступают соответственно сигналы AS, Занесение AS, A S - 1. Сигнал AS

представляет собой цифровой код, соответствующий разности между текущим положением головки записи-воспроизве- , дения устройства позиционирования и заданным положением. Этот код, соответствующий требуемой величине перемещения, заносится в устройство для формирования сигналов скорости движения позиционирующего механизма по сигналу Занесение A S. Импульсный сигнал A S - 1 формируется датчиком перемещения (ДП) позиционирующего механизма всякий раз, когда головка записи-воспроизведения переместится на расстояние, равное шагу ДП. На фиг. 2 приведена структурная схема

микропроцессорного устройства для формирования сигналов скорости движения позиционирующего механизма, ориентированная на применение трехмагистрального микропроцессора типа КР580ВМ80. Как

видно из фиг. 2, БФУС 1 содержит микропроцессорный элемент (МП) 5 со схемами формирования трех стандартных магистралей - шины адреса (ША), шины данных (ШД) и шины управления (ШУ), постоянное запоминающее устройство (ПЗУ) 6, блок ввода- вывода (БВВ) 7. БВВ 7 построен на основе микросхемы программируемого параллельного интерфейса (ППИ) КР580ВВ55.

На фиг. 3 приведена функциональная

схема БПДП 3. Схема содержит элемент ИЛИ 8, формирователь 9 импульсов, шестнадцатиразрядный счетчик 10, шестнадцать элементов 2И 12-27 с открытым коллектором. В соответствии с функциональной

схемой БПДП 3 работает следующим образом. По сигналу УУН Занесение AS по входам D в счетчик 10 записывается начальный адрес размещения в ОЗУ цифровых кодов управления .скоростью движения

позиционирующего механизма. Импульсные сигналы A S - 1 (сигналы счета позиций, формируемые ДП головки записи-воспроизведения) увеличивают на единицу содержимое счетчика 10 и через элемент ИЛИ 8

запускают формирователь 9. Формирователь 9 запускается также с приходом сигнала Занесение AS, поступающим из УУН. На выходе формирователя 9 формируется единичный импульс длительностью 3-4 мкс, который поступает на вход. Запрос захвата (З.Зх.) МП 5 (фиг. 2). МП 5 формирует сигнал Подтверждение захвата (П.Зх.). который поступает на первые входы элементов 2И 12-27. При этом на ША БФУС 1 поступает адресная информация с выходов счетчика 10. МП 5 устанавливает на ЩД содержимое ячейки ОЗУ 2, адрес которой находится на ША. Задним фронтом сигнала формирователя 9 З.Зх. происходит занесе- ние в буферный регистр 11 информации с ЩД БФУС 1, которая поступает на входы ЦАП4.

Формирование сигналов, необходимых для чтения-записи информации из ОЗУ 2 при работе в обычном режиме и чтения информации в режиме прямого доступа к памяти (ПДП) показано на фиг. 4. Из фиг. 4 видно, что при отсутствии высокого уровня сигнала П.Зх. сигналами, определяющи- ми направление передачи информации (Вых. 1) и разрешающими передачу информации (Вых. 2)являются соответственно сигналы ЧТ.ЗУ (стандартный сигнал ШУ) и Выборка УЗУ, формируемый схемой де- шифрации адреса ОЗУ. В режиме ПДП сигналы разрешения выборки ОЗУ (Вых. 2) и низкий уровень на выходе 1, определяющий передачу информации из ОЗУ на ЩД, формируется сигналами МП 5 П.Зх.

В соответствии со структурной схемой (фиг, 1 и 2 и блок-схемой алгоритма (фиг. 5) устройство для формирования сигналов скорости движения позиционирующего механизма работает следующим образом.

УУН подает на шину а код A S, соответствующий разности адресов текущей и требуемой зоны (количество зон, на которые необходимо переместить головку записи- воспроизведения), на шину б импульсный сигнал Занесение AS (фиг. 1 и 2).

Формирование кривой скорости осуществляется путем предварительной записи в последовательные ячейки ПЗУ начиная с адреса Анач.пзу кодов табулированной фун- кции V(n), отражающей оптимальную зависимость скорости перемещения от модуля текущей разности координат между головками записи-воспроизведения и заданной информационной дорожкой при максимальной разности координат A Smax, формирования в ОЗУ и последующего считывания кодов функции V (п), определяющей зависимость скорости от модуля разности

координат при заданной разности координат AS.

Цифровые коды функции V (п) формируются в соответствии с выражением

V

(п р(А1)- если F(A1) F(A2); F(A2), если F(A1) F(A2);

где А1 Анач. ПЗУ + ();

А2 АНач. пзу + Д5-(п-1);

п 1, 2AS;

F() - функциональное преобразование, осуществляемое с помощью ПЗУ.

Очевидно, что для любой разности адресов AS при п 1 значение

V (П) V (1) - Р(Анач. ПЗУ).

Поэтому при включении питания устройства после выполнения необходимых стандартных операций для программирования ППИ сразу происходит запись по начальному адресу ОЗУ (Анач. ОЗУ) известного

Значения V (1) Р(АНач.ОЗУ) Анач.ПЗУ.

Сигнал Занесение AS инициирует цикл формирования микропроцессором функции U (п) и занесения ее в ОЗУ в соответствии с алгоритмом, представленным на фиг. 5. Практически, переход к данному фрагменту программы работы микропроцессора может быть осуществлен после программного опроса сигнала Занесение AS, либо по соответствующему прерыванию, либо другим известным образом.

Программа осуществляет ввод информации с порта БВВ 7, т.е. ввод адресной разности AS, формирование первого адреса А1 Анач.пзу - начального адреса размещения в ПЗУ кривой V(n), второго адреса А2 А1 + A S и третьего адреса A3 АНач.озу - адреса начала размещения в ОЗУ кривой V (п) (фиг. 6). Адреса А1 и A3 увеличиваются, а адрес А2 уменьшается на единицу. Далее следует цикл формирования в ОЗУ функции V (п), который включает чтение ячеек ПЗУ по адресам А1 и А2 и сравнение их содержимого (А1 и А2). Меньшее (или равное) содержимое ячейки заносится в ОЗУ по адресу A3. Выход из цикла осуществляется при равенстве второго адреса А2 и начального адреса размещения В ПЗУ ФУНКЦИИ Анач.ПЗУ.

Начало движения позиционирующего механизма определяется приходом сигнала Занесение AS, который поступает на вход б БПДП 3 (фиг. 3). При этом в счетчик 10 заносится начальный адрес размещения в ОЗУ функции V (п) Анач ОЗУ и через схему ИЛИ 8 запускается формирователь 9. Последний вырабатывает импульсный сигнал длительностью 3-4 мкс, который в качестве

сигнала Запрос захвата шин поступает на соответствующий вход МП 5, вызывая режим ПДП. МП 5 в ответ на Запрос захвата шин вырабатывает сигнал (уровня логической единицы) Подтверждения захвата шин, который поступает на один из входов элементов 2И 12-37, разрешая прохождение информации с выхода счетчика 10 на ША БФУС 1. Таким образом, на ША формируется адрес А4 АНЭЧ.ОЗУ - начальный ад- рее размещения в ОЗУ функции V (п). На ЩД появляется содержимое ячейки ОЗУ, соответствующее адресу А4, которое по заднему фронту сигнала формирователя 9 заносится в буферный регистр 11 и далее поступает на ЦАП 4, где преобразуется в аналоговый сигнал управления электроприводом, который приводит к движение головку записи-воспроизведения. После этого режим ПДП завершается и МП 5 переходит к выполнению программного цикла занесения в ОЗУ функции V (п).

При движении головки записи-воспроизведения на входной шине б устройства возникают импульсные сигналы счета пози- ций Д S - 1, вырабатываемые датчиком перемещений, которые поступают на счетный вход счетчика 10 БПДП 3, увеличивая на единицу адрес А4 считывания из ОЗУ значений функции V (п). Эти же импульсы через схему ИЛИ 8 запускают формирователь 9, вызывая тем самым режим ПДП. Таким образом, с приходом каждого сигнала счета позиций AS - 1 в буферный регистр 11 заносится содержимое ячейки ОЗУ, адрес которой А4 в данный момент времени

содержится в счетчике 10 и на выходе ЦАП 4 формируется сигнал, определяющий скорость движения позиционирующего механизма.

Формула изобр.етения Устройство для формирования сигналов скорости движения позиционирующего механизма, содержащее блок формирования управляющих сигналов, вход которого соединен с внешней шиной разности адресов, цифроаналоговый преобразователь, выходную шину, внешние шины занесения разности адресов и декремента разности адресов, отличающееся тем, что, с целью повышения быстродействия, в него введены блок оперативного запоминающего устройства и блок прямого доступа к памяти, первый и второй управляющие входы которого соединены соответственно с внешними шинами занесения разности адресов и декремента разности адресов, а выход подключен через цифроаналоговый преобразователь к выходной шине, при этом блок формирования управляющих сигналов выполнен в виде связанных между собой двунаправленными шинами микропроцессора, постоянного запоминающего устройства и блока ввода-вывода, вход которого является входом блока формирования управляющих сигналов, выходы которого, являющиеся выходами микропроцессора, связаны двунаправленными шинами с входами блока оперативного запоминающего устройства и блока прямого доступа к памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления скоростью движения позиционирующего механизма | 1987 |

|

SU1515198A1 |

| Многоканальный преобразователь кода в напряжение | 1988 |

|

SU1571765A1 |

| Способ многоканального аналого-цифрового преобразования и многоканальный аналого-цифровой преобразователь | 1986 |

|

SU1451858A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1257848A1 |

| УСТРОЙСТВО ДЛЯ ПРОВЕРКИ АППАРАТУРЫ РЕЛЕЙНОЙ ЗАЩИТЫ И ПРОТИВОАВАРИЙНОЙ АВТОМАТИКИ | 1987 |

|

RU1695806C |

| Устройство для ввода и вывода цветной графической информации | 1985 |

|

SU1315964A1 |

| Способ определения места повреждения линий электропередачи и связи и устройство для его осуществления | 1986 |

|

SU1348756A1 |

| УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ | 1991 |

|

RU2020608C1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1287290A1 |

| Система управления автоматической трансмиссией транспортного средства | 1989 |

|

SU1731661A1 |

Изобретение относится к области техники хранения цифровой информации и может быть использовано в оптических внешних запоминающих устройствам с дисковым носителем информации. Цель изобретения -повышение быстродействия устройства. Устройство содержит блок 1 формирования управляющих сигналов, блок 2 оперативного запоминающего устройства, блок 3 прямого доступа к памяти, цифроаналоговый преобразователь 4. Введение новыхэлементов (блока прямого доступа к памяти и блока оперативного запоминающего устройства) и образование новых связей между элементами устройства позволяет выполнить блок формирования управляющих сигналов на основе микропроцессорной техники и сократить время формирования сигналов скорости, что приводит к повышению быстродействия устройства в целом. 6 ил. сл

AS

L

Л| да i vl7 /

Ь -2 ///// л

R 4S-/

Фиг. 2

u, f-Jf .,. „

& f

f X Of О - ptazi a-- 3/3 c - tf T

if

«|-rr TJ

H.

bvi L

Ј f

, Ј

rf

г

fT

P

2L

.

«|-rTJ

.

vi L

() IV

0/

r.

У

f- ЪС

cd fd

|9f

pn 7J, C

I

r

-KQ

V

//

51

J 1 ЈG

t-

L r.h

у /-.97

-/c/

Z

;c7

2/7/7

A8C6CAL

U

-cp,--v3ctar/ue А2 АЪ

да

з

нет

нОпч

Фиг 5

/

U(n)

Программа МП Л5 AT

А на ч ПЗУ

МладшийСтарший

адр. ПЗУадр. ПЗУ

Адресное л/эострамс/пво ЛЗУ

U (л)

Аначозу

МладшийСтарший

адр. ОЗУадр. ОЗУ

Адресное пространство ОЗУ

l-U(n) при dS JSsnax 2.3А- U(nlпри Д$ J5 max

Фиг. 6

| Патент США Ms 3699555, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

| Устройство для регулирования скорости движения позиционирующего механизма | 1985 |

|

SU1278965A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Авторское свидетельство СССР № 14115198, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-06-07—Публикация

1989-10-09—Подача