Изобретение относится к вычислительной и ггифровой измерительной технике и может быть использовано для преобразования и 1фровых величин в аналоговые.

Цель изобретения - повышение точности за счет улучшения линейности характеристики преобразования.

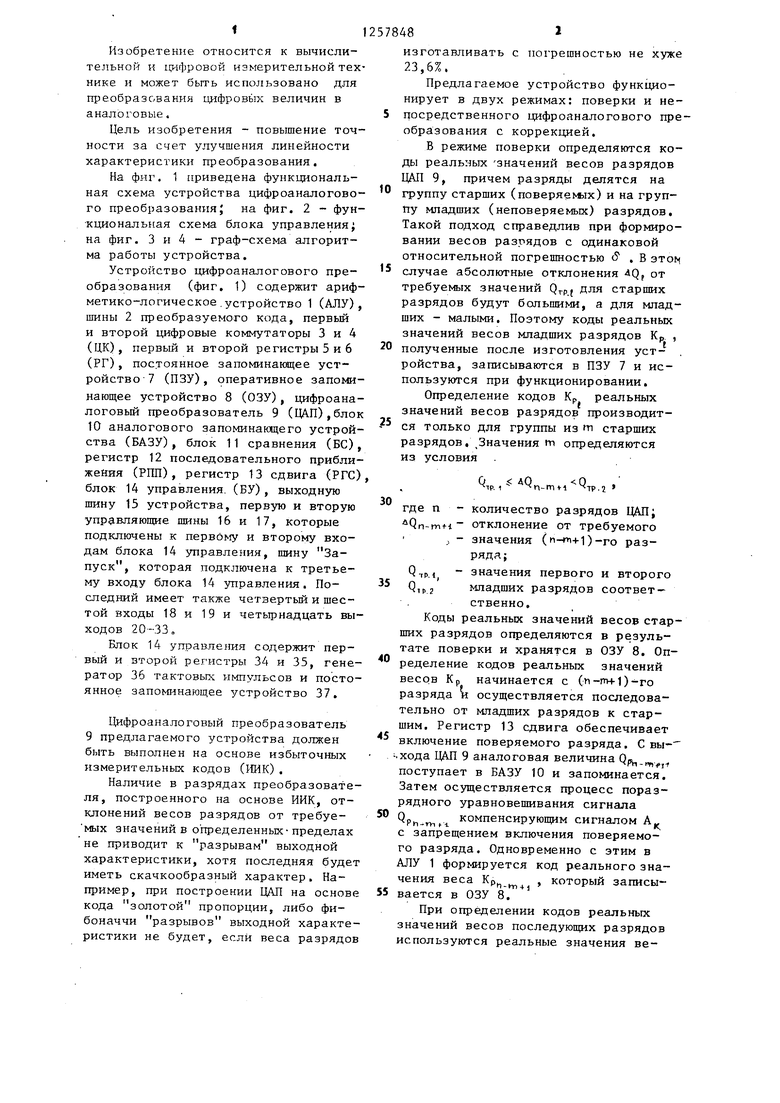

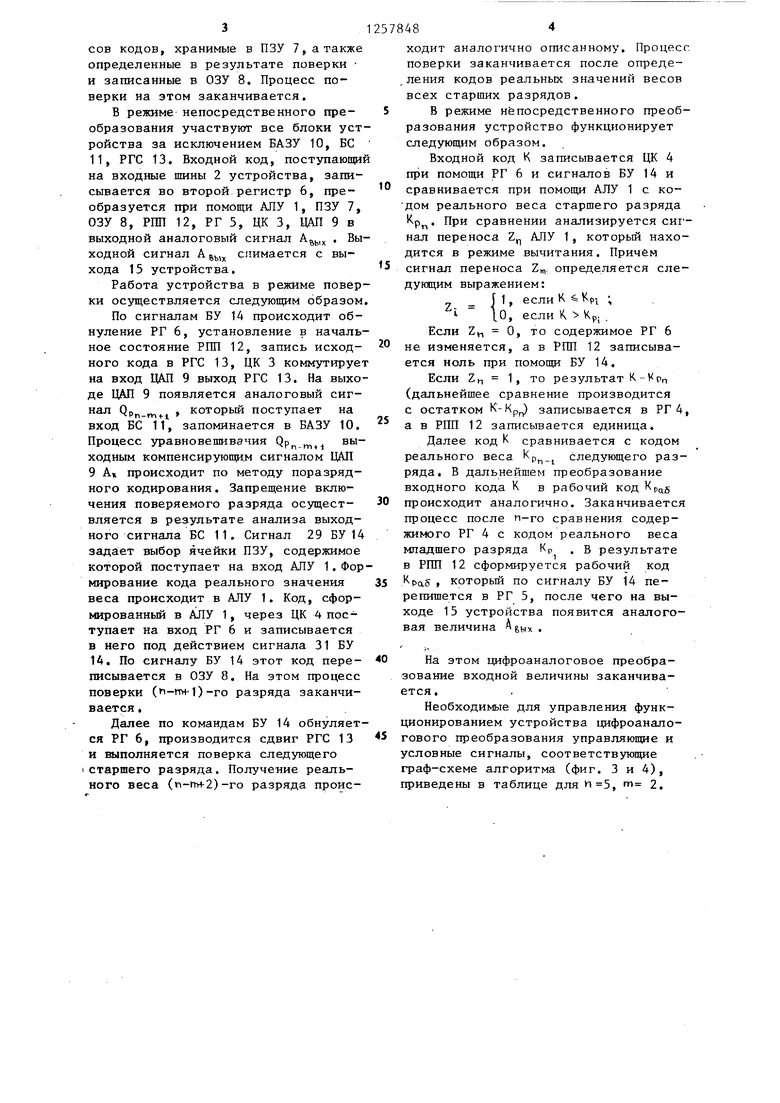

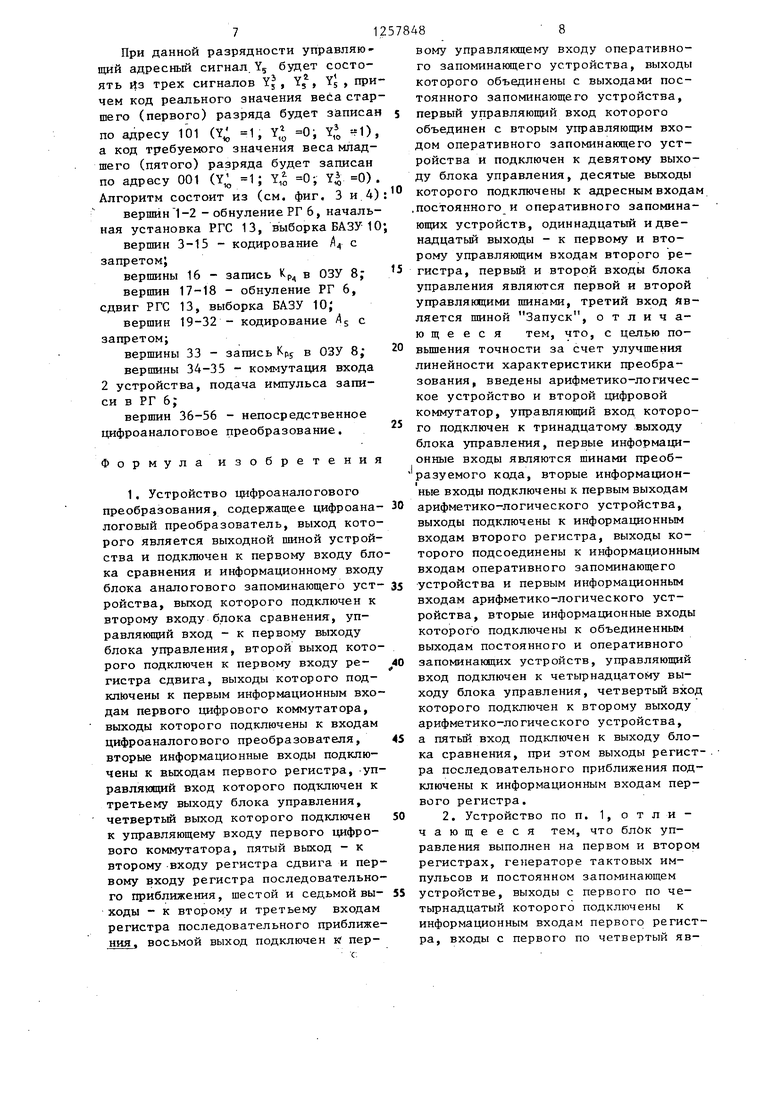

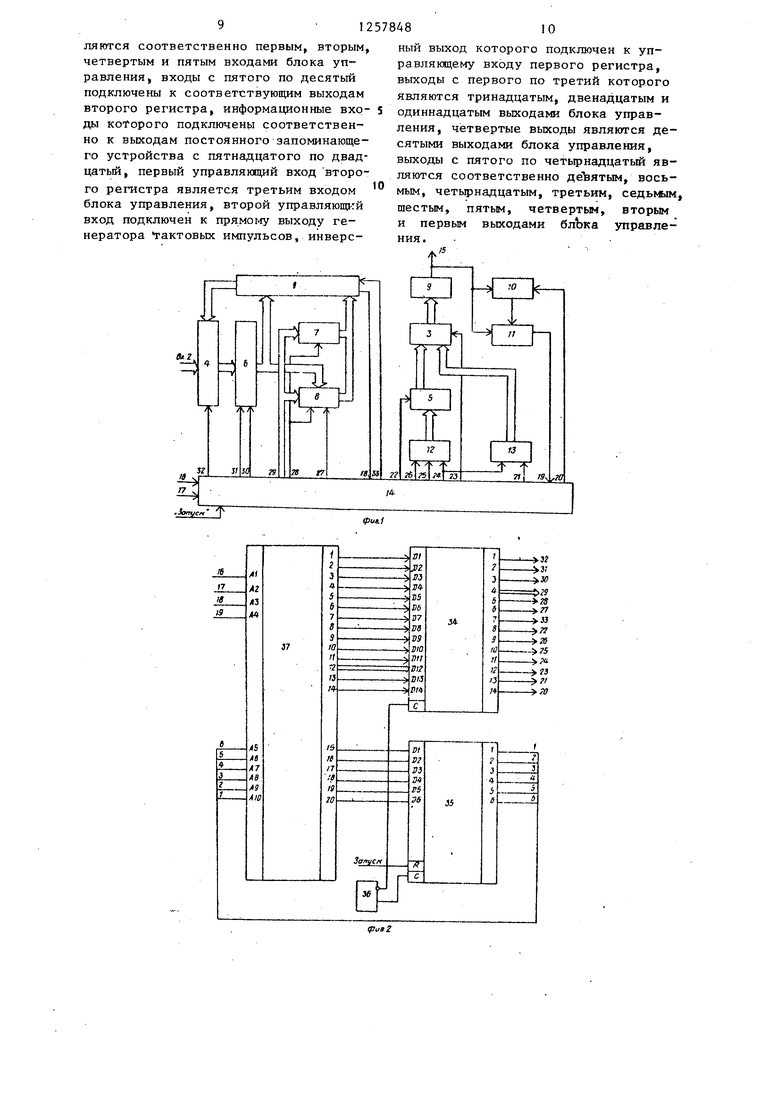

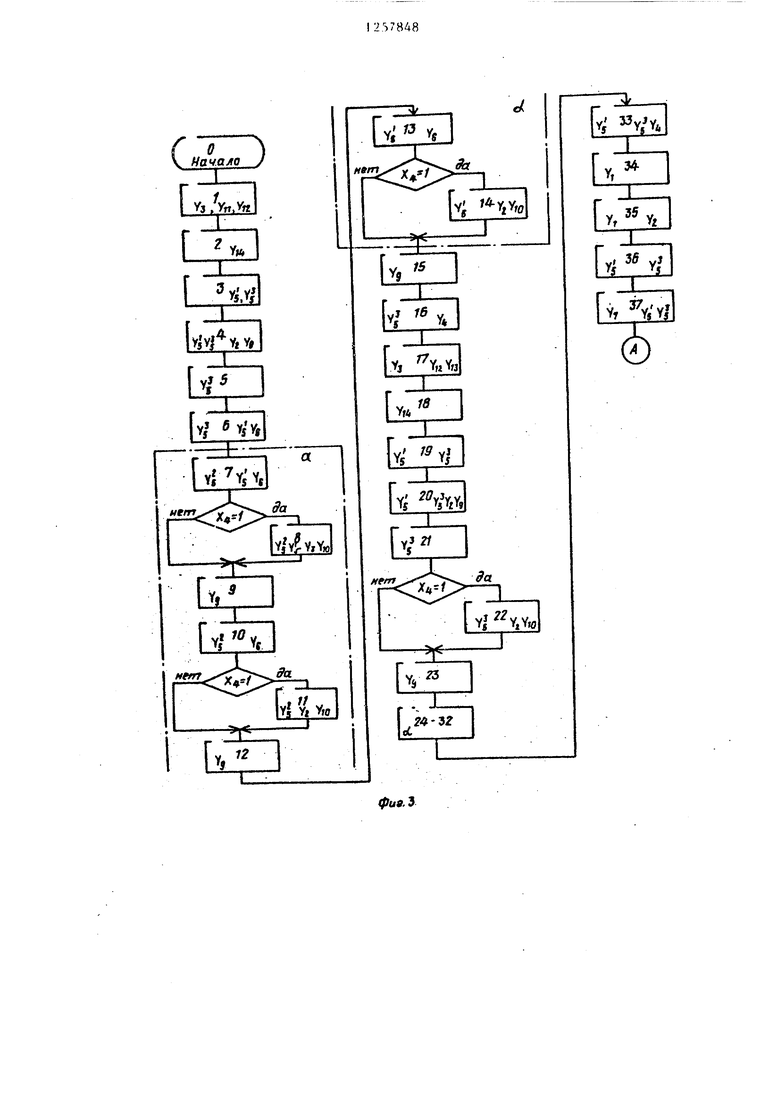

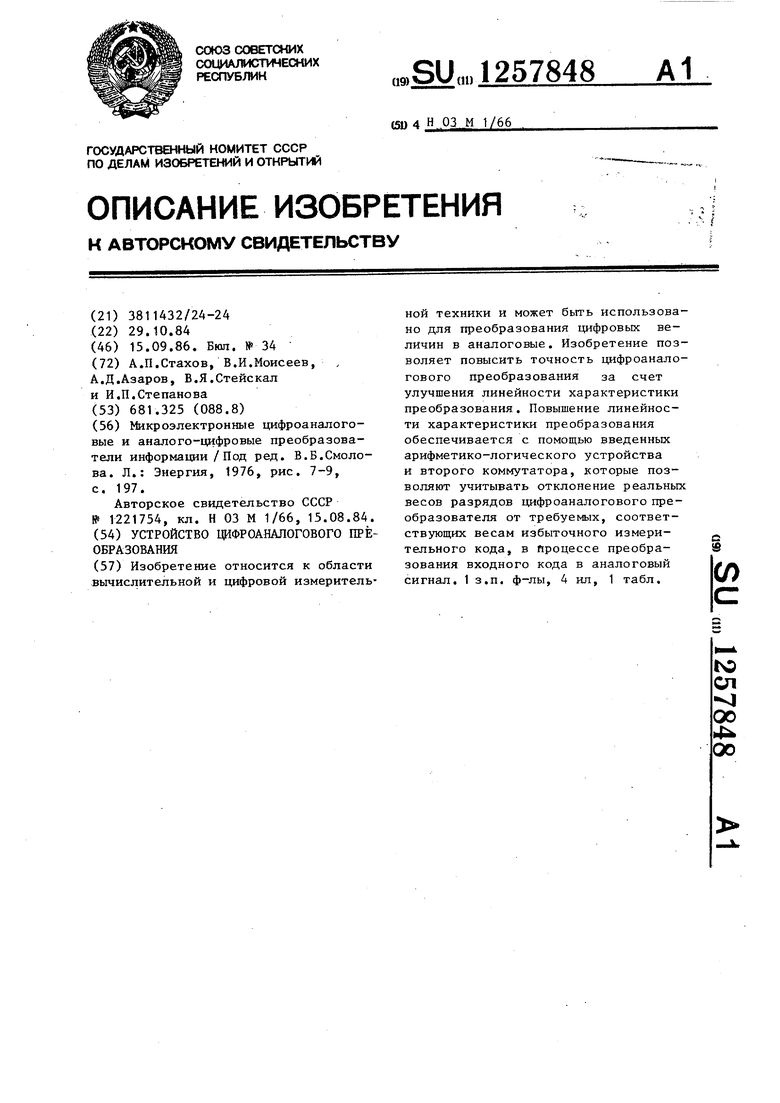

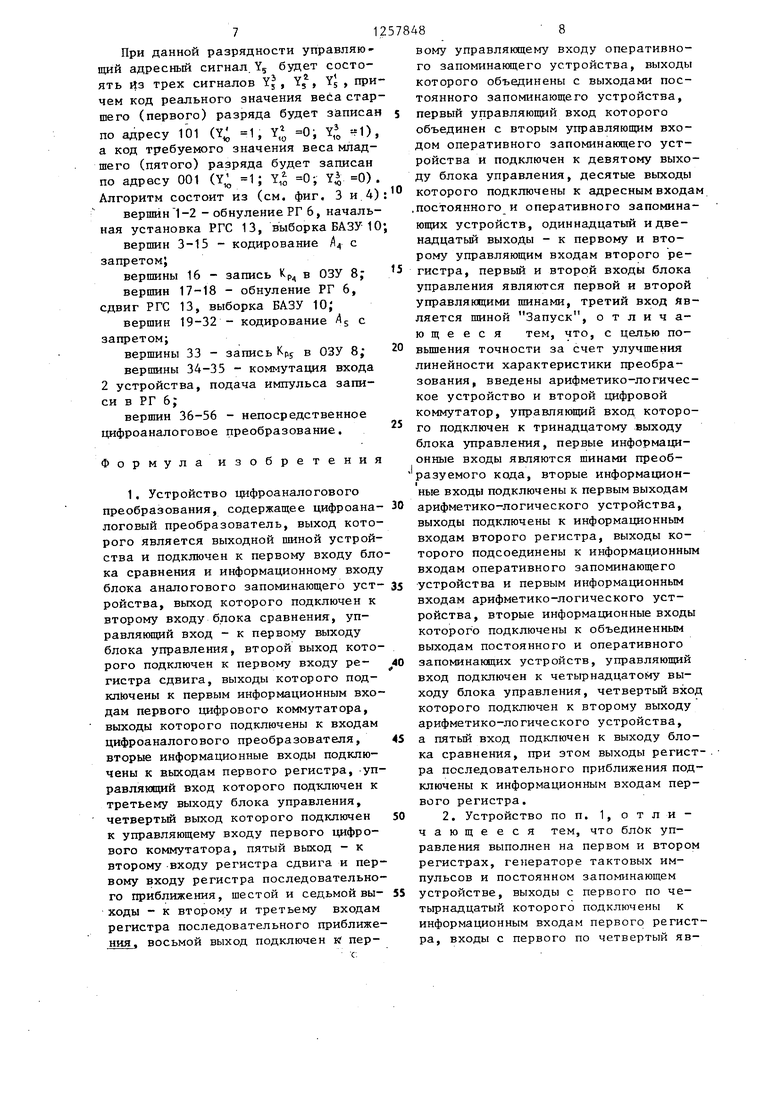

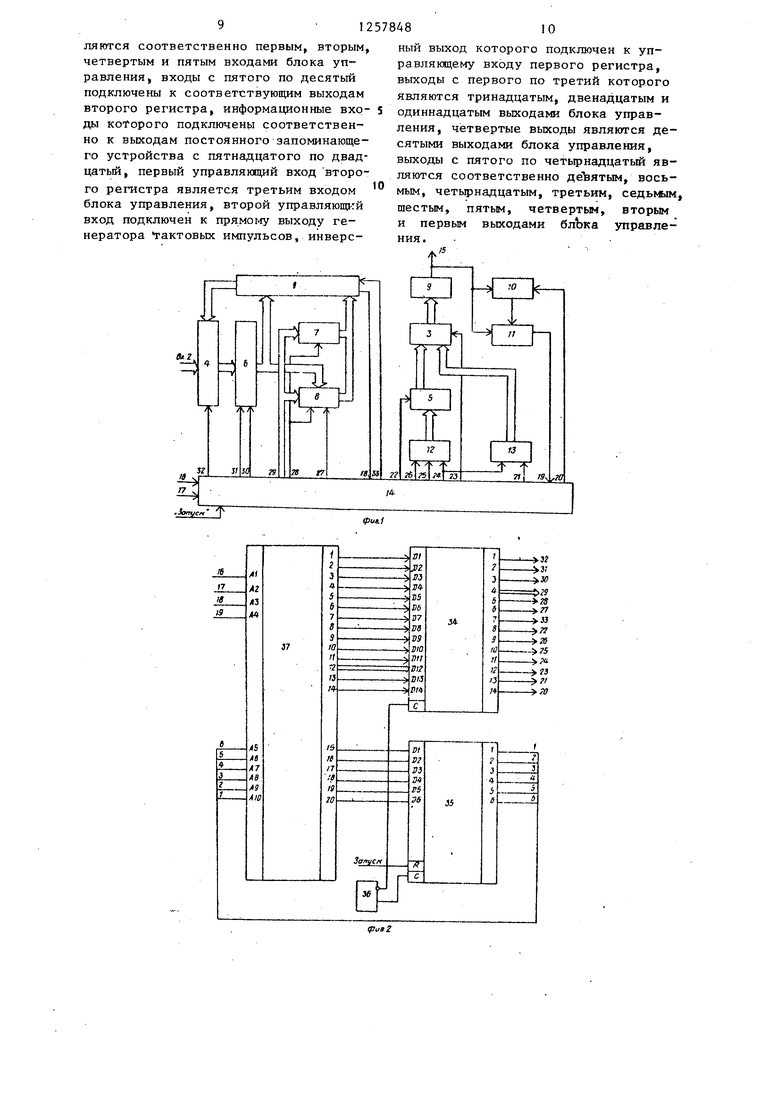

На фиг. 1 приведена функциональная схема устройства цифроаналогового преобразования; на фиг. 2 - фун- кциональная схема блока управления; на фиг. 3 и 4 - граф-схема алгоритма работы устройства.

Устройство цифроаналогового преобразования (фиг. 1) содержит арифметико-логическое .устройство 1 (АЛУ), шины 2 преобразуемого кода, первьш и второй цифровые коммутаторы 3 и 4 (ЦК), первый и второй регистры 5 и 6 (РГ), постоянное запоминаюцее устройство 7 (ПЗУ), оперативное запоминающее устройство 8 (ОЗУ), цифроана- логовый преобразователь 9 (ЦА11),блок 10 аналогового запоминающего устройства (БАЗУ), блок 11 сравнения (БС), регистр 12 последовательного приближения (РПП), регистр 13 сдвига (РГС) блок 14 управления. (БУ) , выходную шину 15 устройства, первую и вторую управляющие шины 16 и 17, которые подключены к первому и второму входам блока 14 управления, шину Запуск, которая подключена к третьему входу блока 14 управления. Последний имеет также четвертьм и шестой входы 18 и 19 и четырнадцать выходов 20-33„

Блок 14 управления содержит первый и второй регистры 34 и 35, генератор 36 тактовых импульсов и постоянное запоминающее устройство 37.

Цифроаналоговый преобразователь 9 предлагаемого устройства должен быть выполнен на основе избыточных измерительных кодов (ШК) .

Наличие в разрядах преобразователя, построенного на основе ИИК, отклонений весов разрядов от требуе- мых значений в о пределенных- пределах не приводит к разрывам выходной характеристики, хотя последняя будет иметь скачкообразный характер. Например, при построении ЦДЛ на основе кода золотой пропорции, либо фи- боначчи разрывов выходной характеристики не будет, если веса разрядов

изготавливать с погрешностью не хуже 23,6%.

Предлагаемое устройство функционирует в двух режимах: поверки и нецосредственного цифроаналогового преобразования с коррекцией.

В режиме поверки определяются коды реальньпс значений весов разрядов ЦАП 9, причем разряды делятся на

группу старших (поверя из1х) и на группу мпадших (неповеряемых) разрядов. Такой подход справедлив при формировании весов разрядов с одинаковой относительной погрешностью . В STONI

случае абсолютные отклонения 4Qj от требуемых значений для старших разрядов будут большими, а для младших - малыми. Поэтому коды реальных значений весов младших разрядов Кр ,

полученные после изготовления устройства, записываются в ПЗУ 7 и используются при функционировании.

Определение кодов Кр реальных значений весов разрядов производится только для группы из И1 старших разрядов. ,Значения m определяются из условия

1р. 1 n-mti тр.2

где п - количество разрядов ЦАП; Qn-mti отклонение от требуемого ,, - значения ()-го разряда;

- значения первого и второго Q,P2 младших разрядов соответственно.

Коды реальных значений весов старших разрядов определяются в результате поверки и хранятся в ОЗУ 8. Определение кодов реальных значений весов Кр начинается с (n-m+D-ro разряда и осуществляется последовательно от младших разрядов к старшим. Регистр 13 сдвига обеспечивает включение поверяемого разряда. С вы- -.хода ЦАП 9 аналоговая величина Qp,,.., поступает в БАЗУ 10 и запоминается. Затем осуществляется процесс поразрядного уравновешивания сигнала . компенсирующим сигналом А„ с запрещением включения поверяемого разряда. Одновременно с этим в АЛУ 1 формируется код р1еального значения веса Кр| , который записы- вается в ОЗУ 8.

При определении кодов реальных значений весов последующих разрядов используются реальные значения ве

3

сов кодов, хранимые в ПЗУ 7, а также определенные в результате поверки - и записанные в ОЗУ 8. Процесс поверки на этом заканчивается.

В режиме непосредственного преобразования участвуют все блоки устройства за исключением БАЗУ 10, БС 11, РГС 13, Входной код, поступающи на входные шины 2 устройства, записывается во второй регистр 6, преобразуется при помощи АЛУ 1, ПЗУ 7, ОЗУ 8, РПП 12, РГ 5, ЦК 3, ЦДЛ 9 в выходной аналоговый сигнал Ag,, . Выходной сигнал А 5, слимается с выхода 15 устройства.

Работа устройства в режиме поверки осуществляется следующим образом

По сигналам БУ 14 происходит обнуление РГ 6, установление в начальное состояние РПП 12, запись исходного кода в РГС 13, ЦК 3 коммутирует на вход ЦАП 9 выход РГС 13. На выходе ЦЛП 9 появляется аналоговый сигнал Qp , который поступает на вход БС 11, запоминается в БАЗУ 10. Процесс уравновешивания Qpr,nm ходным компенсирующи.м сигналом ЦАП 9 А происходит по методу поразрядного кодирования. Запрещение включения поверяемого разряда осуществляется в результате анализа выходного сигнала БС 11. Сигнал 29 БУ 14 зада:ет выбор ячейки ПЗУ, содержимое которой поступает на вход АЛУ 1. Формирование кода реального значения веса происходит в АЛУ 1. Код, сформированный в АЛУ 1, через ЦК 4 поступает на вход РГ 6 и записывается в него под действием сигнала 31 БУ 14. По сигналу БУ 14 этот код переписывается в ОЗУ 8. На этом процесс поверки (п-гм-1)-го разряда заканчивается ,

Далее по командам БУ 14 обнуляется РГ 6, производится сдвиг РГС 13 и выполняется поверка следующего I старшего разряда. Получение реального веса (г -гм-2)-го разряда проис484

ходит аналогично опнсанному. Процесс поверки заканчивается после определения кодов реальных значений весов всех старших разрядов.

В режиме непосредственного преобразования устройство функционирует следующим образом.

Входной код К записывается ЦК 4 при помощи РГ 6 и сигналов БУ 14 и сравнивается при помощи АЛУ 1 с ко- дом реального веса старшего разряда Кр. При сравнении анализируется сиг - нал переноса Z АЛУ 1, который находится в режиме вычитания. Причем сигнал переноса Z определяется следующим выражением:

7 1 Ь если К, 6: Кр1 ; i ID, если К Кр; . Если Z о, то содержимое РГ 6 не изменяется, а в РШ1 12 записывается ноль при помощи БУ 14.

Если Zfi 1, то результат (дальнейшее сравнение производится с остатком К-Кр„) записывается в РГ 4,

а В РПП 12 записывается единица.

Далее код сравнивается с кодом реального веса ,-, следующего разряда, В дальнейшем преобразование входного кода К в рабочий код Кр происходит аналогично. Заканчивается процесс после п-го сравнения содержимого РГ 4 с кодом реального веса

младшего разряда

Kt

В результате

в РПП 12 сформируется рабочий код который по сигналу БУ 14 перепишется в РГ 5, после чего на выходе 15 устройства появится аналоговая величина А g,j,,x .

На этом цифроаналоговое преобразование входной величины заканчивается.

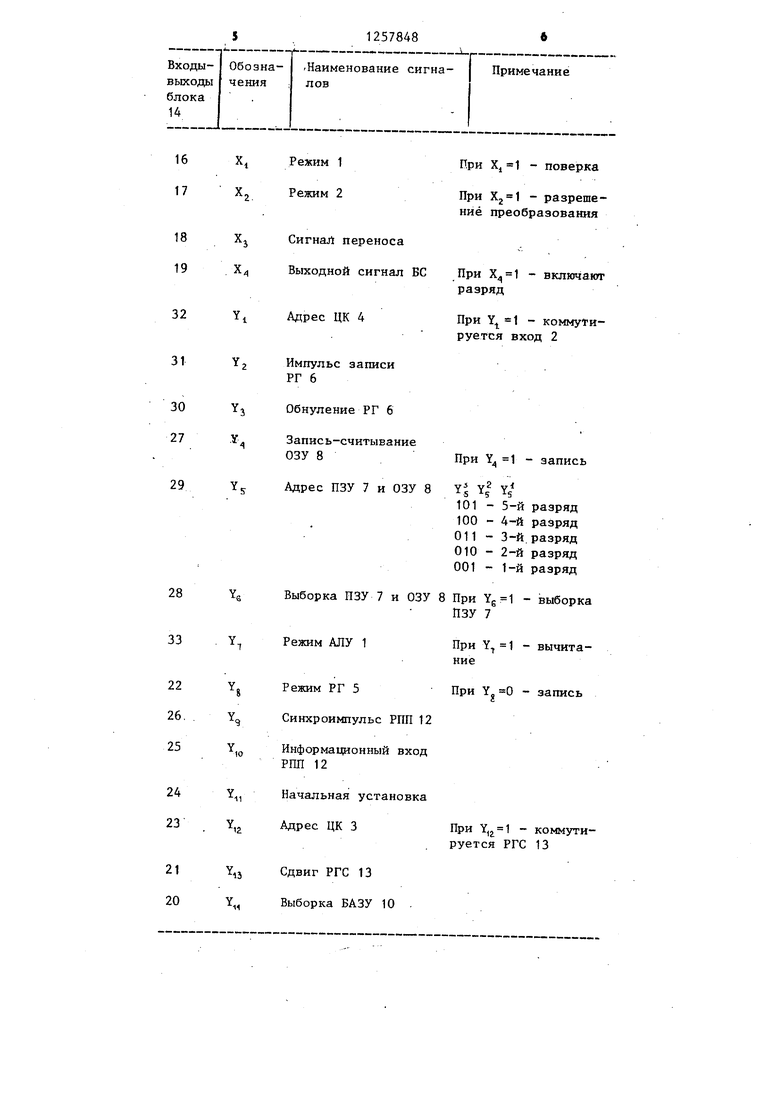

Необходимые для управления функционированием устройства цифроаналогового преобразования управляющие и условные сигналы, соответствующие граф-схеме алгоритма (фиг. 3 и 4), приведены в таблице для , т 2.

Адрес ЦК 4

Импульс записи РГ 6

Обнуление РГ 6

Запись-считывание ОЗУ 8

Адрес ПЗУ 7 и ОЗУ 8

8

YO

ч

1г

4j

Выборка ПЗУ 7 и ОЗУ 8 Режим АЛУ 1

Режим РГ 5 Синхроимпульс РПП 12

Информационный вход РПП 12

Начальная установка Адрес ЦК 3

Сдвиг РГС 13 Выборка БАЗУ 10 .

разряд

При Y 1 - коммутируется вход 2

При Y 1 - запись

Y| Y| YS

101 - 5-й разряд 100 - 4-й разряд 011 - 3-й разряд 010 - 2-й разряд 001 - 1-й разряд

При - выборка ПЗУ 7

При Y 1 - вычитание

При Y. 0 - запись

При Y, 1 - коммутируется РГС 13

71257848

При данной разрядности управляющий адресный сигнал 5 будет состоять из трех сигналов Y, , Yj , причем код реального значения веса старшего (первого) разряда будет записан s по адресу 101 (Y 1, Y, 0; Yf -1), а код требуемого значения веса младшего (пятого) разряда будет записан по адресу 001 (Y; 1; Y, 0; Y 0).

вому управляющему входу оперативного запоминакяцего устройства, выходы которого объединены с выходами постоянного запоминающего устройства, первый управляющий вход которого объединен с вторым управляющим входом оперативного запоминающего устройства и подключен к девятому выходу блока управления, десятые выходы

Алгоритм состоит из (см. фиг. 3 и 4): которого подключены к адресным входам

вершин 1-2-обнуление РГ 6, началь- .постоянного и оперативного запомина- ная установка РГС 13, выборка БАЗУ 10;

вершин 3-15 - кодирование Ац с запретом;

верщины 16 - запись Кр в ОЗУ 8j

верщнн 17-18 - обнуление РГ 6, сдвиг РГС 13, выборка БАЗУ 10;

верщин 19-32 - кодирование AS с запретом;

верщины 33 - запись Kpj в ОЗУ 8;

вершины 34-35 - коммутация входа 2 устройства, подача импульса записи в РГ 6;

вершин 36-56 - непосредственное цифроаналоговое преобразование.

20

ющих устройств, одиннадцатый и двенадцатый выходы - к первому и второму управляющим входам второго ре- 15 гистра, первый и второй входы блока управления являются первой и второй управляющими щинами, третий вход Является шиной Запуск, отличающееся тем, что, с целью по- вьш1ения точности за счет улучшения линейности характеристики преобразования, введены арифметико-логическое устройство и второй цифровой коммутатор, управляющий вход которого подключен к тринадцатому выходу блока управления, первые информационные входы являются шинами преобразуемого кода, вторые информационные входы подключены к первым выходам

25

Формула изобретения

1. Устройство цифроаналогового

преобразования, содержащее цифроана- 30 арифметико-логического устройства, логовый преобразователь, выход кото- выходы подключены к информационным рого является выходной шиной устройства и подключен к первому входу блока сравнения и информационному входу блока аналогового запоминающего уст- 35 устройства и первым информационным ройства, выход которого подключен к входам арифметико-логического уст- второму входу блока сравнения, управляющий вход - к первому выходу блока управления, второй выход которого подключен к первому входу ре- 40 запоминающих устройств, управляющий гистра сдвига, выходы которого под- вход подключен к четырнадцатому выключены к первым информационным входам первого цифрового коммутатора, выходы которого подключены к входам

входам второго регистра, выходы которого подсоединены к информационным входам оперативного запоминающего

ройства, вторые информационные входы которого подключены к объединенным выходам постоянного и оперативного

ходу блока управления, четвертьй вход которого подключен к второму выходу арифметико-логического устройства, цифроаналогового преобразователя, 45 а пятый вход подключен к выходу бло- вторые информационные входы подклю- ка сравнения, при этом выходы регистчены к выходам первого регистра, -управляющий вход которого подтшючен к третьему выходу блока управления, четвертый выход которого подключен к управляющему входу первого цифрового коммутатора, пятый выход - к

2. Устройство по п. 1, о т л и - чающееся тем, что блик управления выполнен на первом и втором регистрах, генераторе тактовых импульсов и постоянном запоминающем

второму входу регистра сдвига и первому входу регистра последовательного приближения, шестой и седьмой вы- 55 устройстве, выходы с первого по че- ходы - к второму и третьему входам тырнадцатый которого подключены к регистра последовательного приближе- ния, восьмой выход подключен и перинформационным входам первого регист ра, входы с первого по четвертый яввому управляющему входу оперативного запоминакяцего устройства, выходы которого объединены с выходами постоянного запоминающего устройства, первый управляющий вход которого объединен с вторым управляющим входом оперативного запоминающего устройства и подключен к девятому выходу блока управления, десятые выходы

.постоянного и оперативного запомина-

0

ющих устройств, одиннадцатый и двенадцатый выходы - к первому и второму управляющим входам второго ре- 5 гистра, первый и второй входы блока управления являются первой и второй управляющими щинами, третий вход Является шиной Запуск, отличающееся тем, что, с целью по- вьш1ения точности за счет улучшения линейности характеристики преобразования, введены арифметико-логическое устройство и второй цифровой коммутатор, управляющий вход которого подключен к тринадцатому выходу блока управления, первые информационные входы являются шинами преобразуемого кода, вторые информационные входы подключены к первым выходам

5

арифметико-логического устройства, выходы подключены к информационным устройства и первым информационным входам арифметико-логического уст- запоминающих устройств, управляющий вход подключен к четырнадцатому вывходам второго регистра, выходы которого подсоединены к информационным входам оперативного запоминающего

арифметико-логического устройства, выходы подключены к информационным устройства и первым информационным входам арифметико-логического уст- запоминающих устройств, управляющий вход подключен к четырнадцатому выройства, вторые информационные входы которого подключены к объединенным выходам постоянного и оперативного

ра последовательного приближения подключены к информационным входам первого регистра.

2. Устройство по п. 1, о т л и - чающееся тем, что блик управления выполнен на первом и втором регистрах, генераторе тактовых импульсов и постоянном запоминающем

устройстве, выходы с первого по че- тырнадцатый которого подключены к

устройстве, выходы с первого по че- тырнадцатый которого подключены к

информационным входам первого регистра, входы с первого по четвертый являготся соответственно первым, вторым, четвертым и пятым входами блока управления, входы с пятого по десятый подключены к соответствующим выходам второго регистра, информационные вхр- ды которого подключены соответственно к выходам постоянного запоминающего устройства с пятнадцатого по двадцатый, первый управляющий вход второго регистра является третьим входом блока управления, второй управляюпц гй вход подключен к прямо1 у выходу генератора тактовых импульсов, инверсА;

ный выход которого подключен к управляющему входу первого регистра, выходы с первого по третий которого являются тринадцатым, двенадцатым и одиннадцатым выходами блока управления, четвертые выходы являются десятыми выходами блока управления, выходы с пятого по четырнадцатый являются соответственно деЪятым, восьмым, четырнадцатым, третьим, седьмым шестым, пятым, четвертым, вторым и первым выходами блЪка управления.

фил

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифроаналогового преобразования | 1984 |

|

SU1248072A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1216827A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1221754A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1750060A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1257847A1 |

| Устройство цифроаналогового преобразования | 1986 |

|

SU1405117A1 |

| Устройство аналого-цифрового преобразования | 1985 |

|

SU1288914A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1790030A1 |

| Цифроаналоговый преобразователь | 1984 |

|

SU1216829A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1702525A1 |

Изобретение относится к области вычислительной и цифровой измерительной техники и может быть использовано для преобразования цифровых величин в аналоговые. Изобретение позволяет повысить точность цифроанало- гового преобразования за счет улучшения линейности характеристики преобразования. Повышение линейности характеристики преобразования обеспечивается с помощью введенных арифметико-логического устройства и второго коммутатора, которые позволяют учитывать отклонение реальных весов разрядов цифроаналогового преобразователя от требуемых, соответствующих весам избыточного измерительного кода, в Процессе преобразования входного кода в аналоговый сигнал. 1 з.п. ф-лы, 4 ил, 1 табл. § (Л ю ел 00 4;; СХ)

Составитель В.Пелзшиков Редактор М.Петрова Техред Л.СердюковаКорректор Е.Сирохман

Заказ 6358 Тираж 816Подписное

ВЕШИПИ Государственного комитета СССР . по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

.Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Микроэлектронные цифроанапого- вые и аналого-цифровые преобразователи информации / Под ред | |||

| В.Б.Смоло- ва | |||

| Л.: Энергия, 1976, рис | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Способ утилизации отработанного щелока из бучильных котлов отбельных фабрик | 1923 |

|

SU197A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1221754A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-09-15—Публикация

1984-10-29—Подача