которого соединены соответственно с четвертым, третьим и вторым выходами блока интерполирования, первый выход которого соединен с седьмым входом схемы формирования дискретных приращений, восьмой вход которой соединен с восьмым выходом блока управления, первая и вторая выходные информационные шины которого соединены соответственно с второй входной информационной шиной блока преобразования и с первой входной шиной второго ЗУ. вторая входная шина которого обьединена с третьей выходной информационной шиной блока управления и соединена с первой входной шиной регистрирующего устройства, вторая входная шина которого соединена с информационным выходом второго ЗУ, первый и второй входы которой соединены с первым и вторым выходами схемы формирования дискретных приращений соответственно, а третий, четвертый пятый и шестой - с соответствующими выходами блока преобразования, седьмой выход блока управления соединен с первым входом блока выделения экстремума второй выход которой соединен с восьмым входом блока масштабирования, третий пятый и седьмой выходы которого соединены соответственно с вторыми, третьим и четвертым входами блока преобразования,

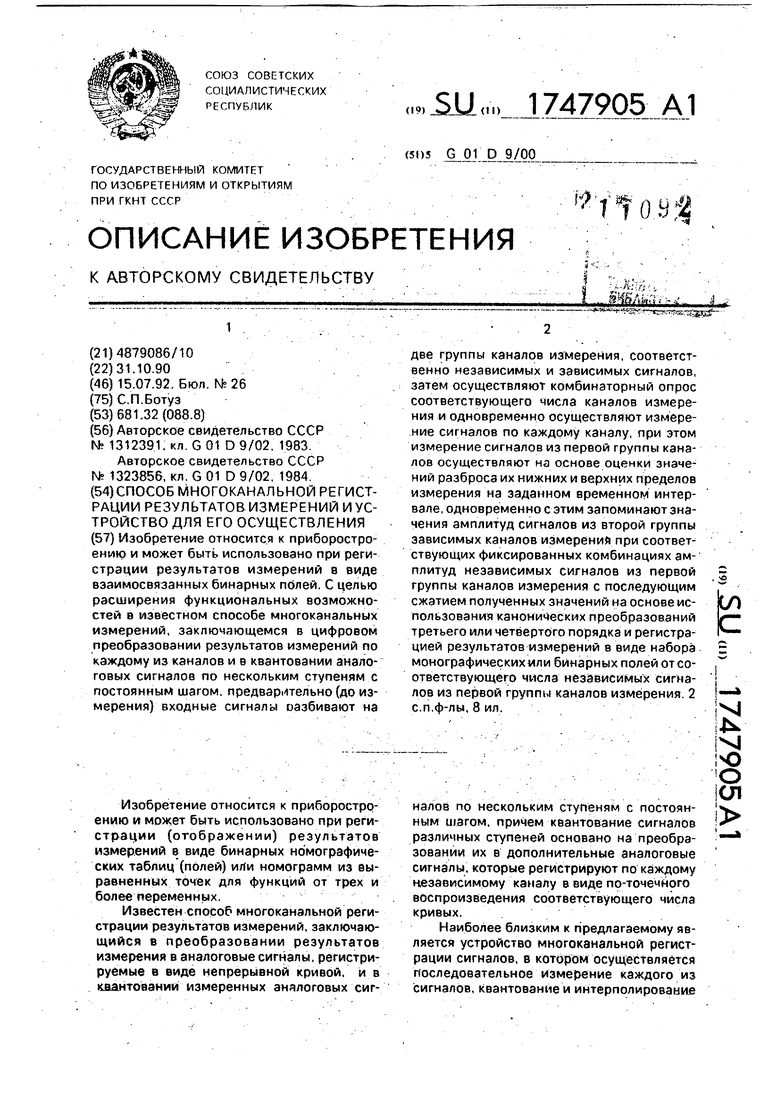

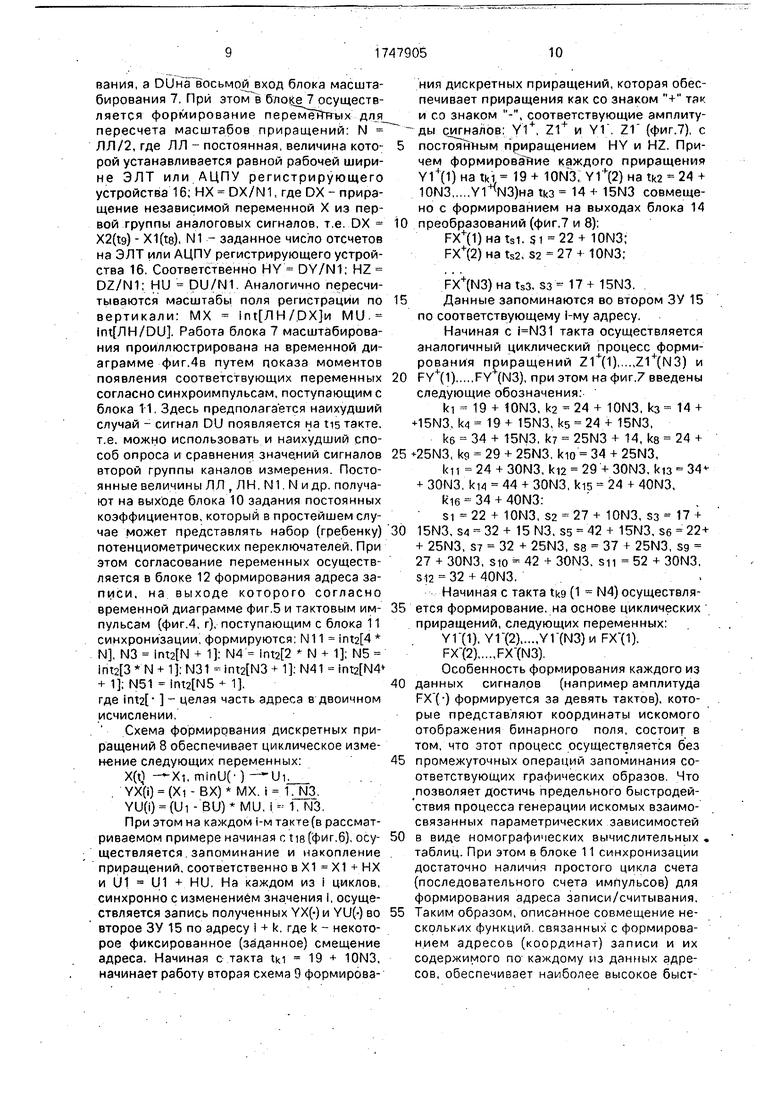

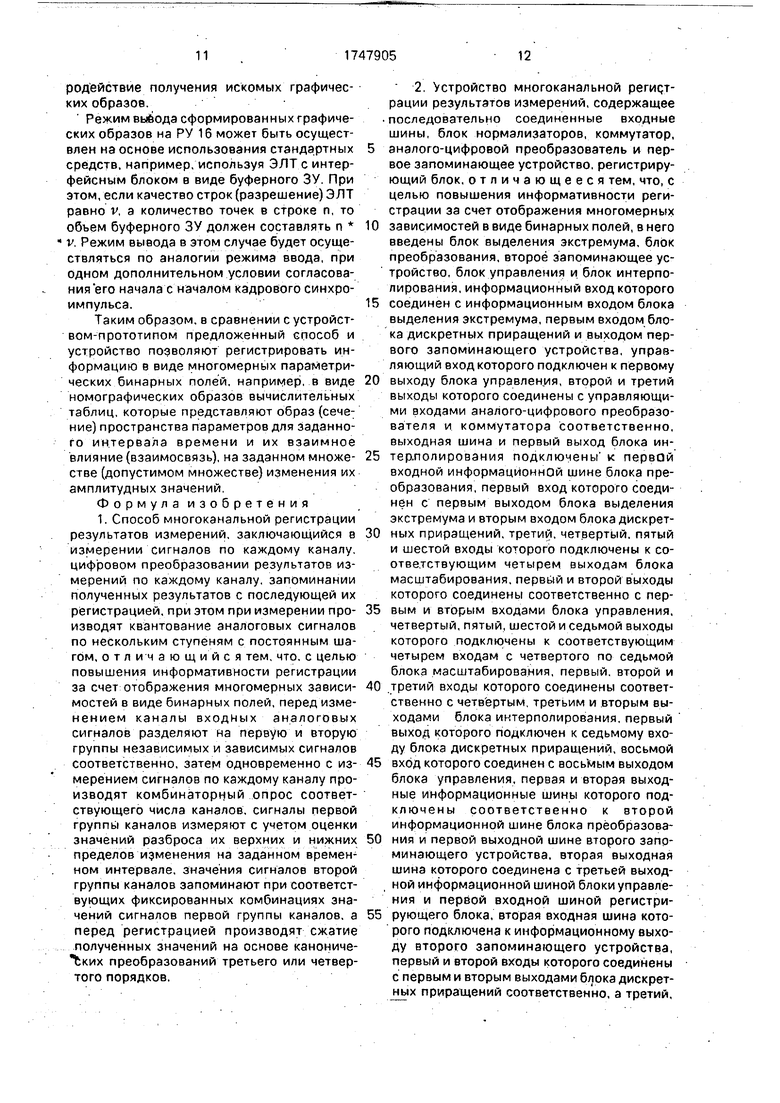

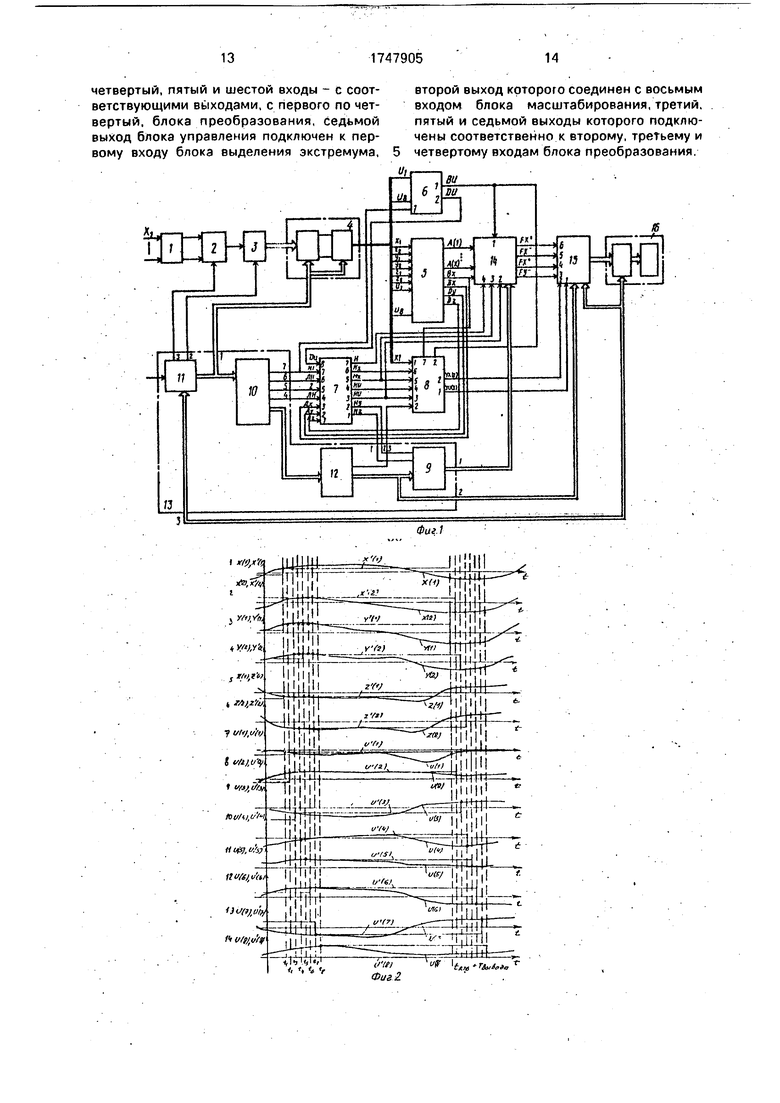

На фиг.1 представлен пример блок-схемы устройства, на фиг.2 - 8 - временные диаграммы поясняющие работу устройства.

Устройство (фиг 1) содержит блок 1 нормирующих устройств коммутатор 2. АЦП 3 первое ЗУ 4, блок 5 интг-р юлирования блок 6 выделения экстремума, блок 7 масштабирования, первая схема 8 формирования дискретных приращений, вторую схему 9 дискретных приращений, блок 10 задания постоянных коэффициентов, блок 11 синхронизации, схему 12 формирования адреса записи,блок 13 управления, блок 14 преобразования, второе ЗУ 15 и регистрирующее устройство 16.

Регистрацию результатов измерений согласно предложенному способу осуществляют следующим образом

Разбиваем аналоговые сигналы на входах нормирующего устройст ва (НУ) 1 на две группы. При этом для определенности будем полагать, что первая группа сигналов характеризует независимые процессы, например первая группа сигналов представляет набор наблюдаемых возмущающих воздействий - X

Х {Х(1), Х(2} Y(1). Y(2) Z(1). Z(2)} n 3

Вторая группа аналоговых сигналов представляет реакцию исследуемого объекта на данный набор возмущающих воздействий, т.е. вторая группа каналов измерений характеризует группу зависимых сигналов

О {U(i): i

Следовательно, в первой группе будут 0 три независимых канала измерений, а во второй - зависимых каналов измерений. При этом согласно предложенному способу будем хранить соответствующие оценки верхних и нижних значений по каж- 5 дому каналу, т.е. измерение по каждому каналу осуществляют одновременно по верхнему и нижнему допустимому пределам:

Х(1Ь НптХ1(т),илиХ(1) Xirmn(t),

Х(2) - supXi(t), или Х(2) Ximax(t)

Vt.0

аналогично

25Y(1) infX1{t), или Y(1)Y,min(t)

Перед началом каждого цикла регистрации, например в момент to, формируется

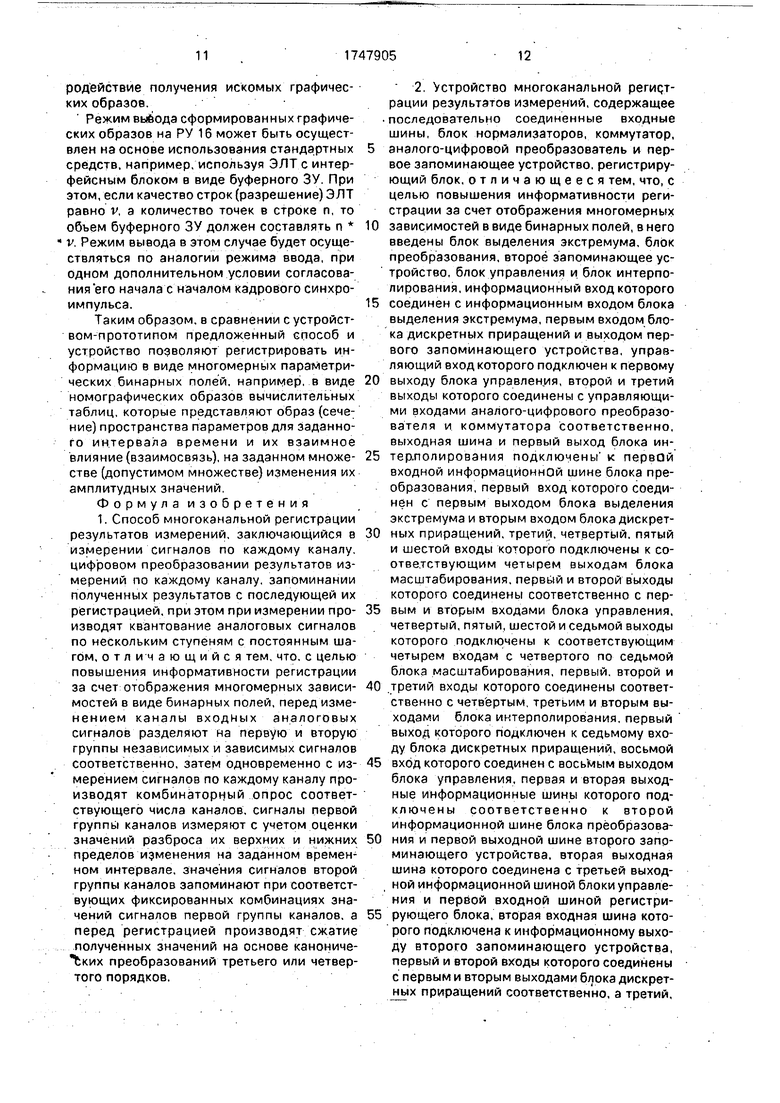

сигнал общего сброса на все регистры памяти и обработки сигналов измерений (этот процесс не показан). На первом временном интервале осуществляется опрос следующих каналов НУ1 (фиг.1, 2 ).первый канал

НУ1 из первой группы независимых аналоговых сигналов, на который поступает в данном случае - Х(1): третий канал Y(1) и пятый - Z(1). Одновременно из второй группы каналов опрашивается первый канал, в предложенном примере седьмой по порядку НУ 1 (фиг.1), на который подается для измерения аналоговый сигнал U(1) Измеренные на данном такте ti значения после аналого- цифрового преобразования в блоке 3 запоминают в первом ЗУ 4 например, в регистрах буферной памяти. На такте 12 осуществляют опрос второю, третьего, пятого и восьмого каналов. На такте t3 осуществляется опрос первого, третьего, шестого и девятого каналов На такте Т4 осуществляют , опрос второго, третьего, шестого и десятого каналов.

Для рассматриваемого примера этот процесс комбинаторного опроса каналов

аналоговых сигналов из разных групп и запоминание значений амплитуд сигналов завершается за восемь тактов. При этом описанная последовательность операций реализована на основе фиксации верхних {Х(2). Y(2). 2(2)} и нижних {Х{1). Y(1). Z(1)}

границ изменения амплитуд сигналов первой группы каналов измерения

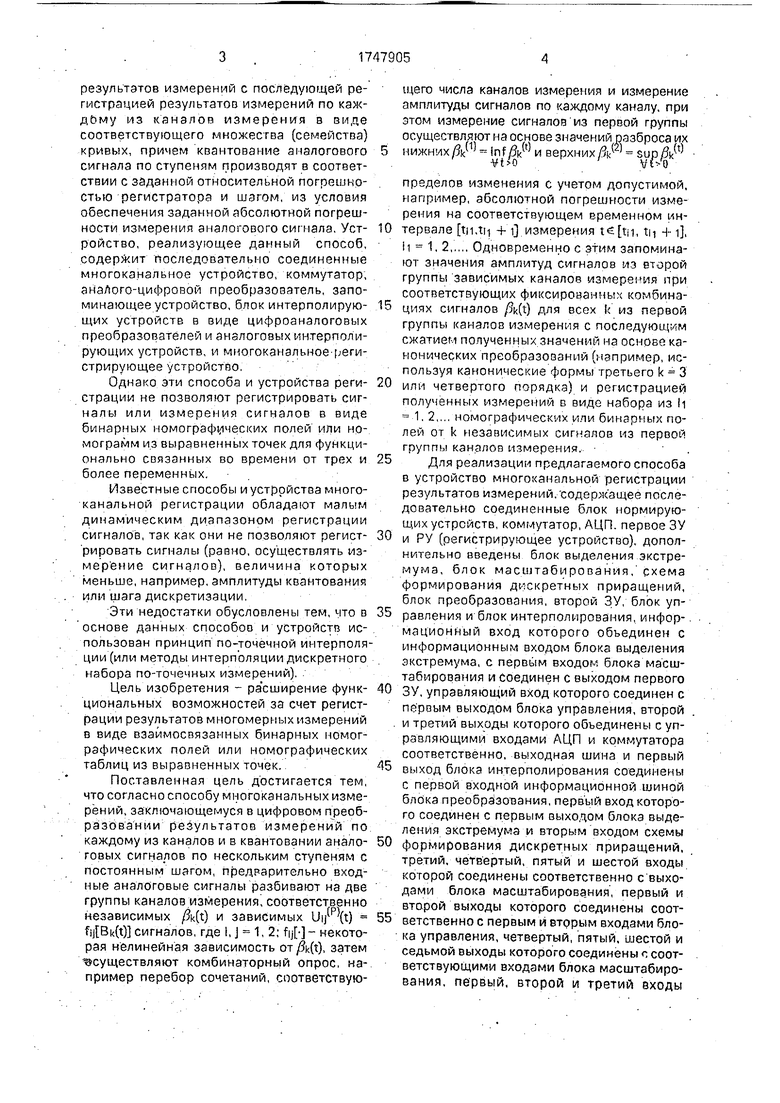

Описанную последовательность опроса в предложенной реализации обеспечивает блок 13 управления согласно временной ди- 5 аграмме, приведенной на фиг.2. Эту процедуру в данном случае обеспечивает блок 11 синхронизации за восемь тактов, Здесь для простоты пояснений полагаем, что значе; ния амплитуд возмущающих воздействий X 10 и реакции исследуемого процесса U з {U(l);

I ТГ2П}, для всех t претерпевает

незначительные изменения, как показано на фиг.2, каждый из регистрируемых сигналов в соответствующем сочетании запоми- 15 нается на соответствующем такте опроса

(см.Х (1), Х (2). Y (1). Y (2), Z (1). Z (2)U (8) и

сохраняется до-начала следующего tkie режима комбинаторного опроса каналов. При этом комбинаторика процедуры (или страте- 20 гия) опроса каждого последующего цикла измерений будет зависеть не только от того, каковы претерпели изменения соответствующие измеряемые переменные по каждому из каналов, но и непосредственно от резуль- 25 татов последующего отображения на регистрирующем устройстве 16.

Так, вышеописанный пример последовательности операций позволяет по каждому из входов второй группы каналов 30 измерения получить значения комбинаторных оценок следующего вида:

Ul(1) fJi(X(1). Y (1).Z (1)) U (2)

f,2(x (2). Y (1). Z (D).35

u (3)fj3(X (1). Y (1),Z (2)),,. . U {8)

f,8(Xl(2).Y (2),Z1(2))

40

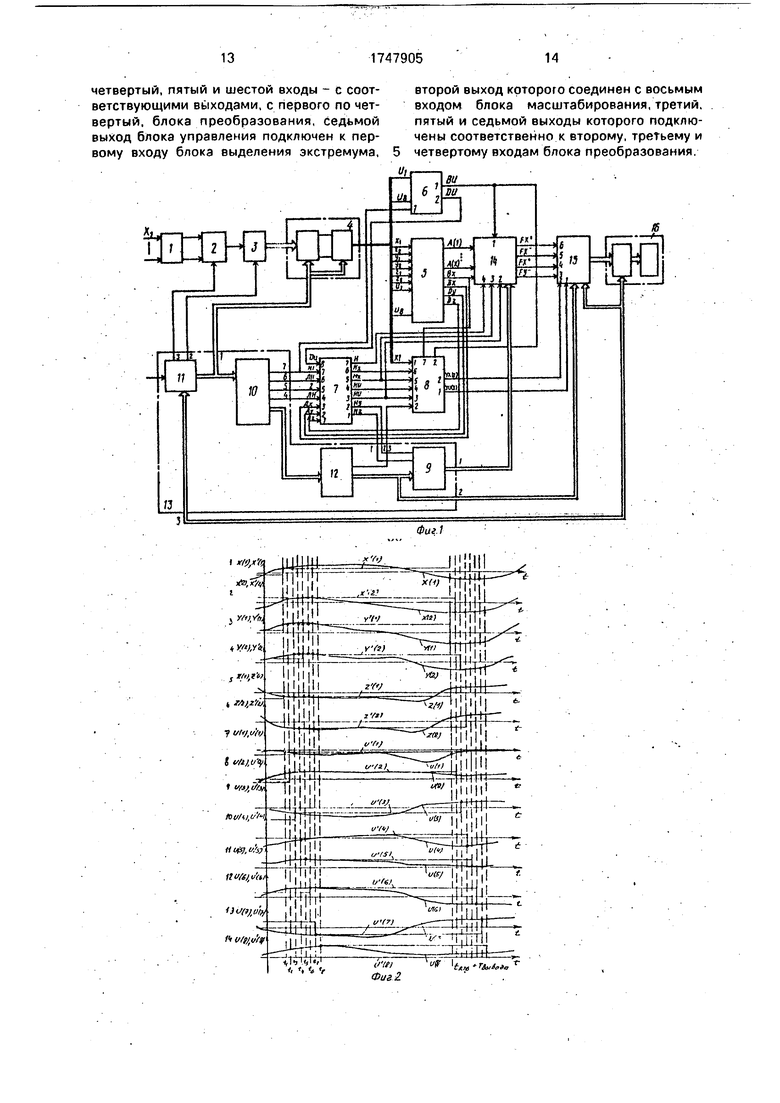

При этом на такте te (фиг.З) на первом выходе блока 5 будет сформирован сигнал, равный ВХ х (1) (фиг 1) На такте tg на втором, третьем и четвертом выходах блока 5 будут сформированы соответственно 45 DX( ) X (2) - X (1). DY () Y (2) - Y (1) и DZ(-) l(2)- г (1)Для простоты изложения опускаем описание очевидных промежуточных операций и их синхронизацию, так как приведенные примеры реализации используют блоки 50 со стандартными элементарными операциями. В рассматриваемом примере реализации блока 5 на его информационных выходах будут сформированы следующие сигналы (фиг.З) на такте tia:55

А(1) U (8) + U (3) - U (4 -U (7) - (-) - DY(-) DZ(-)

на такте tis

A(2) TU1 (1), A(3)

-TU2 + (1), A(4) TU3-TP4 Y(1).

на такте tie: А(5) ТР1 (1)(1)-t

(1)Z(1), A(6) TP2 - (1) - (1) +

-iTP4 X(1)Z(1),

A(7) TP3 - (1) - (1) + (1)Y(1).

на такте tie:

A(8) U (1) - (1) - (1) -TP3 Z(1) + (1)Y(1) + (1)Z(1)+ + (1)Z(1) - (1)Y(1)Z(1). где TU1 u (6) + Uf (1) - U (2) (3):

TU2 - U (7) + U (1) - U (5) - U (3);

Tua-u w + u w-u pj-u p):

TUT UT1/();

TU2 UT2/(DY DZ);

TU3 UT3/(DX DZ),

TP1 (U (2)-U (1)/DX;

TP2 (U(5)-U (1))/DY.

TP3 (U (3)-U1(1))/DZ,

TP4 (U (8) + U1(3)-UI(4)-U1(7)-TU1)/DXJ DY DZ).

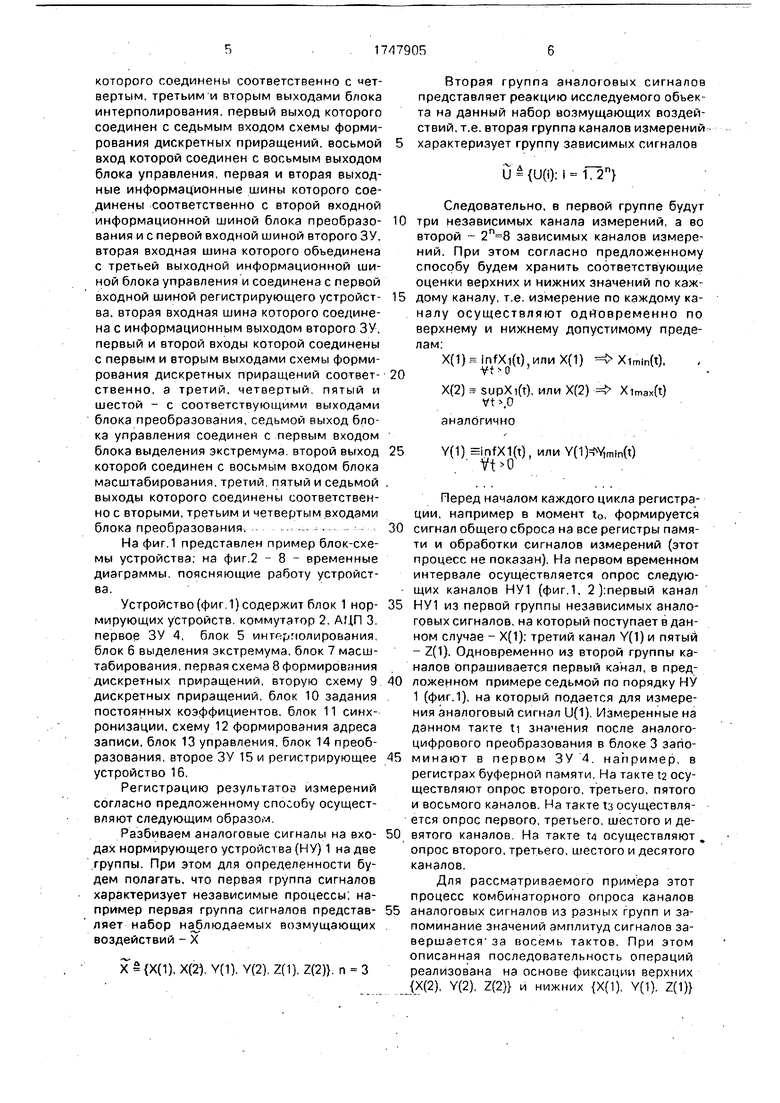

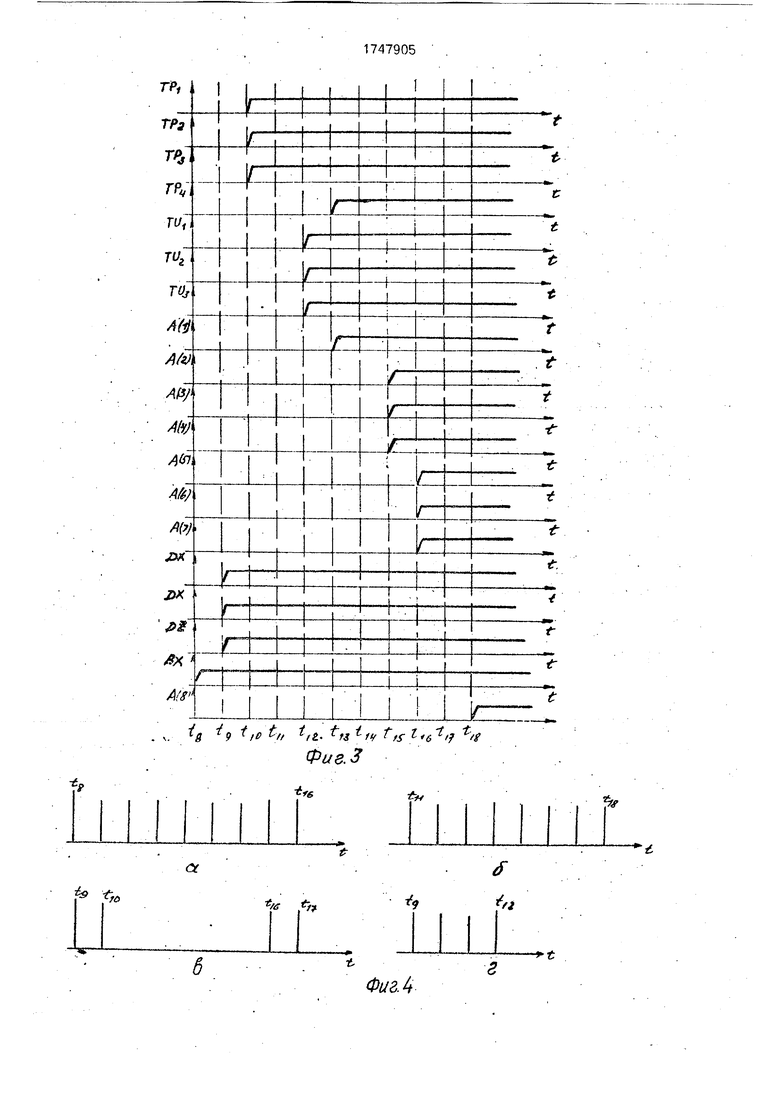

В рассматриваемом примере реализации устройства вышеуказанные значения А(1)А(8) получают в блоке 5 на базе тактовых импульсов, поступающих с блока 11 синхронизации блока управления согласно временным диаграммам (фиг.4а, б).

Работа блока 5 иллюстрирует параллельно-последовательное совмещение операций преобразования с операциями, непосредственно обслуживающими процесс обработки по каждому каналу измерения. Это позволяет повысить быстродействие при формировании соответствующих значений А(1),...А(8), которые поступают на соответствующие входы блока 14 преобразования. Одновременно (начиная с такта te) в блоке б осуществляется процедура определения мах U( ) и мин U( ). Соответственно на первом выходе блока 6 получают BUc Умин на такте ti3 (фиг, 15). а на втором выходе DU (Умах - имин) на tis такте.

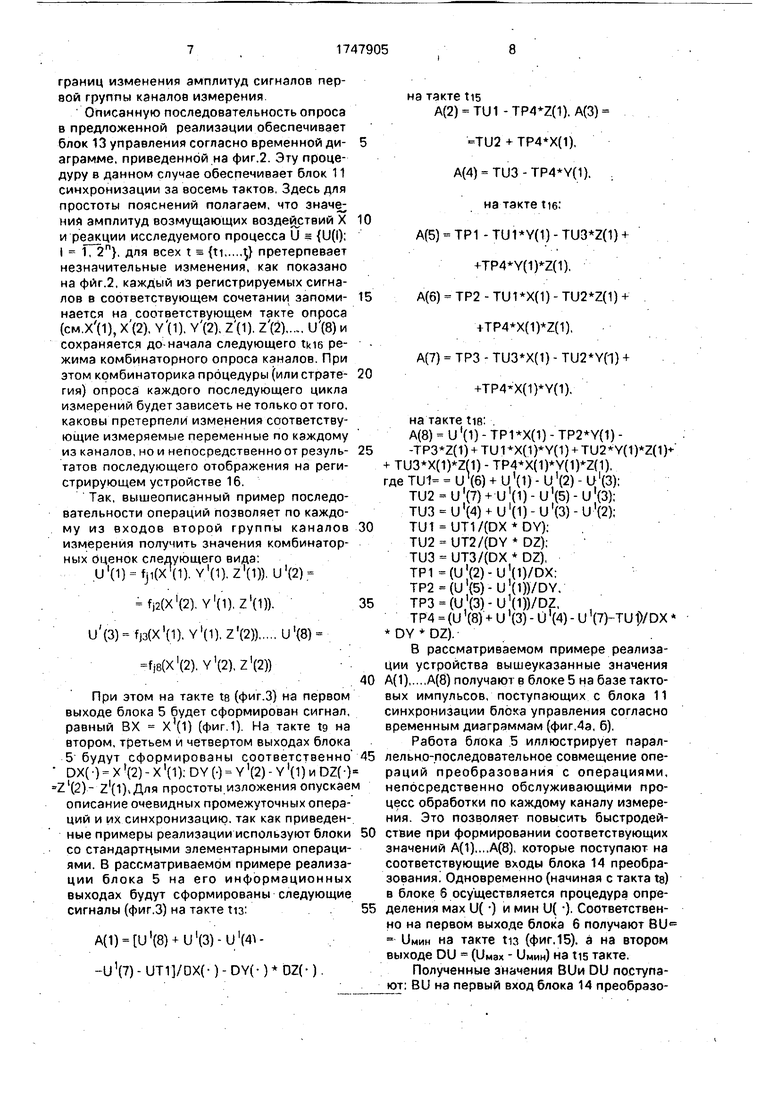

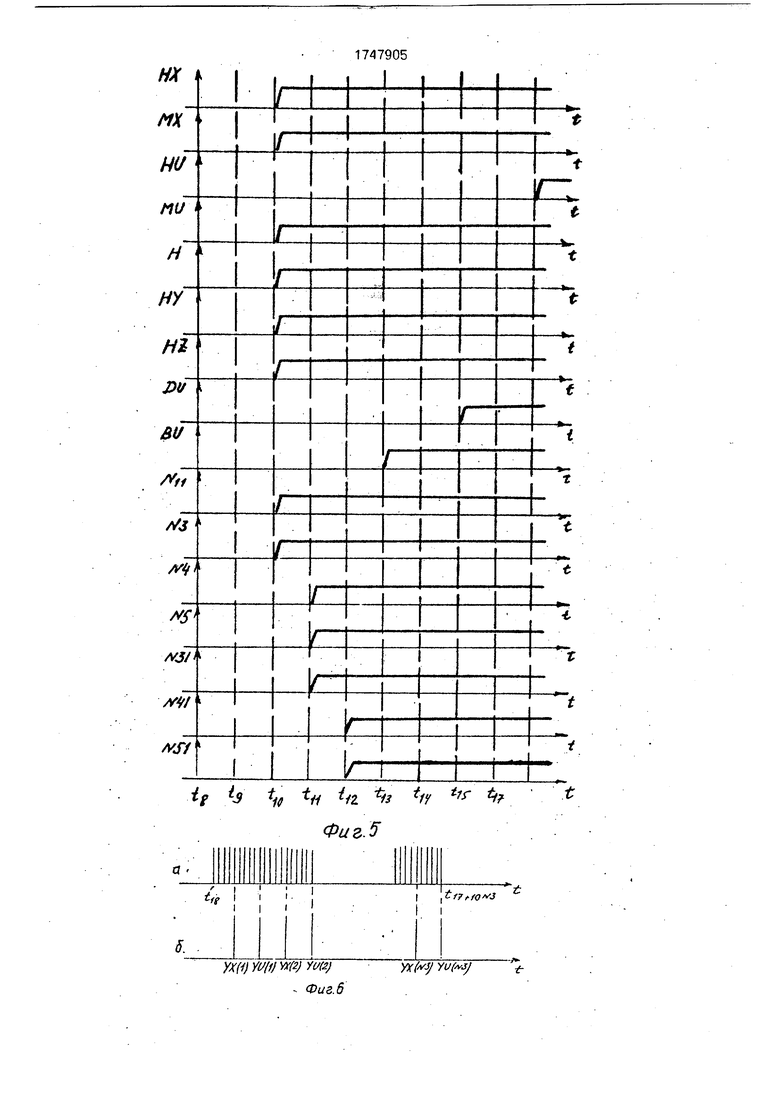

Полученные значения BUn DU поступают: BU на первый вход блока 14 преобразования, а ОУнаГвосьмой вход блока масштабирования 7. При этом в блоке 7 осуществляется формирование перемёГйтлых для пересчета масштабов приращений: N Л Л/2, где Л Л - постоянная, величина которой устанавливается равной рабочей шири- не ЭЛТ или АЦПУ регистрирующего устройства 16; НХ DX/N1, где DX - приращение независимой переменной X из первой группы аналоговых сигналов, т.е. DX X2(tg) - X1(te), N1 - заданное число отсчетов на ЭЛТ или АЦПУ регистрирующего устройства 16. Соответственно HY DY/N1; HZ DZ/N1; HU DU/IM1 Аналогично пересчитываются масштабы поля регистрации по вертикали: MX - 1ш ЛН/ОХ и MU int|7lH/DU. Работа блока 7 масштабирования проиллюстрирована на временной диаграмме фиг.4в путем показа моментов появления соответствующих переменных согласно синхроимпульсам, поступающим с блока 11. Здесь предполагается наихудший случай - сигнал DU появляется на tis такте, т.е. можно использовать и наихудший способ опроса и сравнения значений сигналов второй группы каналов измерения. Постоянные величины ЛЛ , ЛН. N1 N и др. получают на выходе блока 10 задания постоянных коэффициентов, который в простейшем случае может представлять набор (гребенку) потенциометрических переключателей. При этом согласование переменных осуществляется в блоке 12 формирования адреса записи, на выходе которого согласно временной диаграмме фиг.5 и тактовым импульсам (фиг.4, г), поступающим с блока 11 синхронизации, формируются: N11 N, N3 + N4 N + 1, N5 N + N31 - + N41 + N51 + 1. где - целая часть адреса в двоичном исчислении.

Схема формирования дискретных приращений 8 обеспечивает циклическое изменение следующих переменных:

Щ . mlnU(-) --111.

YX{i) (Xi - BX) MX, i 1.JJ3.

YU(i) (Ui - BU) MU, i - 1, N3.

При этом на каждом i-м такте (в рассматриваемом примере начиная с tie (фиг.6), осуществляется запоминание и накопление приращений, соответственно в Х1 Х1 + НХ и U1 U1 + HU. На каждом из i циклов, синхронно с изменением значения I, осуществляется запись полученных YX(«) и YU(-) во второе ЗУ 15 по адресу i + к. где k - некоторое фиксированное (заданное) смещение адреса. Начиная с такта tki 19 + 10N3, начинает работу вторая схема 9 формирова0

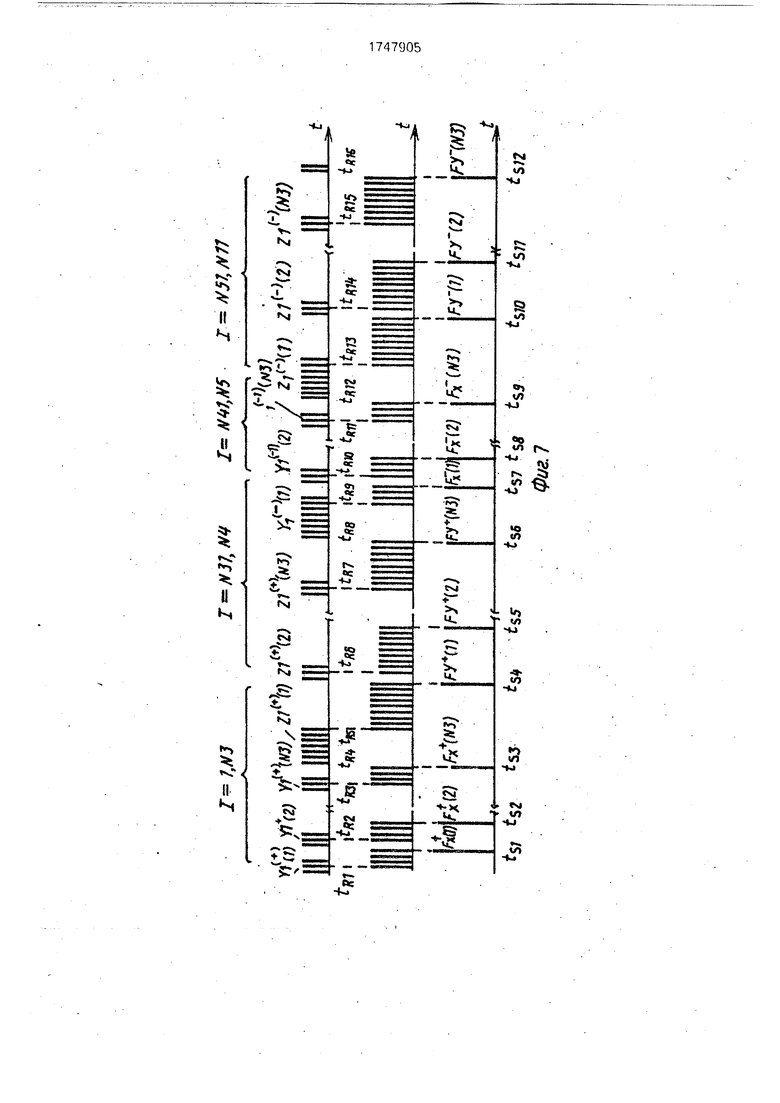

ния дискретных приращений, которая обеспечивает приращения как со знаком + так- и со знаком -, соответствующие амплитуды сигналов: Y1+, Z1+ и Y1. Z1 (фиг.7), с постоянным приращением HY и HZ. Причем формирование каждого приращения Y14(1) на tki - 19 + 10N3, Y1+(2) на tk2 24 + 10N3YI NSJna tk3 14 + 15N3 совмещено с формированием на выходах блока 14 преобразований (фиг.7 и 8):

FX(1) на tsi. 51 22+ 10N3;

FX+(2) на tS2, S2 27 + 10N3;

FX+(N3) на tS3, зз 17 + 15N3. Данные запоминаются во втором ЗУ 15 по соответствующему i-му адресу.

Начиная с такта осуществляется аналогичный циклический процесс формирования приращений Z1+(1)Z1+(N3) и

FY (1)FY (N3), при этом на фиг,7 введены

следующие обозначения:

ki 19 + 10N3, k2 24 + 10N3, k3 14 + +15N3, k4 19 + 15N3, ks 24 + 15N3,

ke 34 + 15N3, k 25N3 + 14, ks 24 + +25N3, kg 29 + 25N3, kio 34 + 25N3,

kn 24 + 30N3, ki2 29 + 30N3, kn 34 + 30N3, ku 44 + 30N3, kis 24 + 40N3, kie 34 + 40N3:

si 22 + 10N3, S2 - 27 + 10N3, S3 - 17 + 15N3, S4 32 + 15 N3, ss 42 + 15N3, se 22+ + 25N3, s 32 + 25N3, S8 37 f 25N3, sg 27 + 30N3, sio - 42 + 30N3. sn 52 + 30N3, S12 32 + 40N3.

Начиная с такта tk9 (1 N4) осуществля- ется формирование, на основе циклических приращений, следующих переменных:

YT(1), Y1(2)Y1(N3)n FX (1).

FX(2)FX(N3).

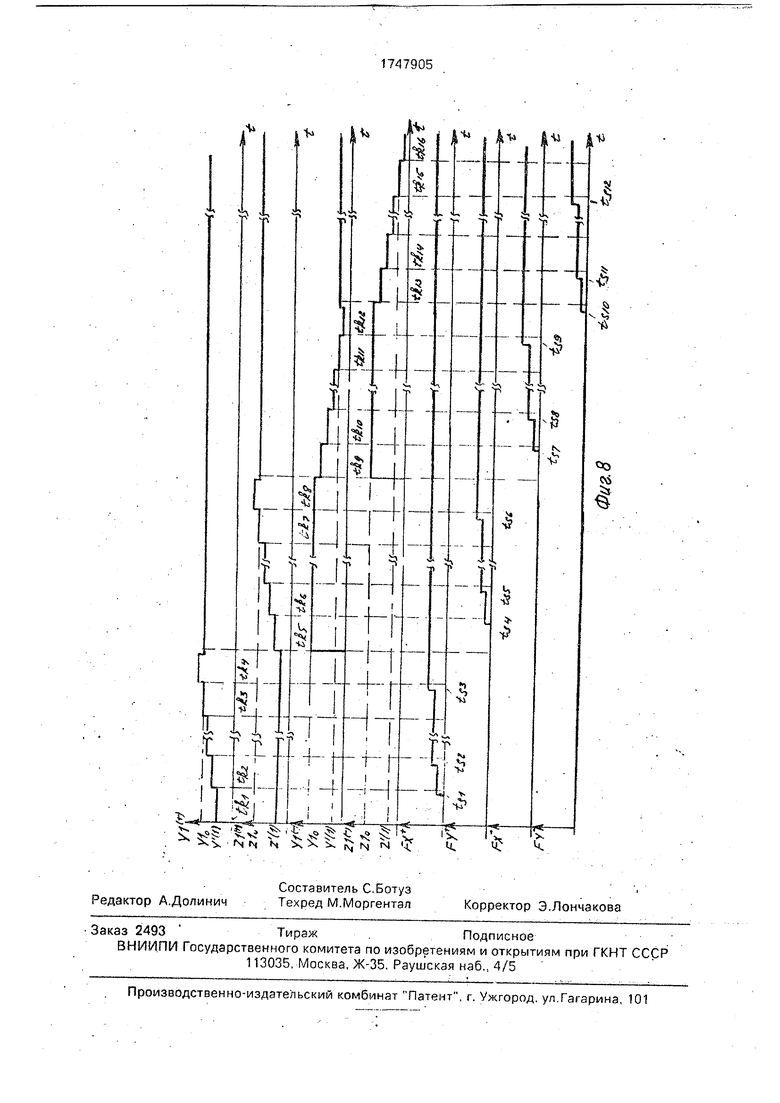

Особенность формирования каждого из данных сигналов (например амплитуда FX () формируется за девять тактов), которые представляют координаты искомого отображения бинарного поля, состоит в том, что этот процесс осуществляется без промежуточных операций запоминания соответствующих графических образов. Что дозволяет достичь предельного быстродействия процесса генерации искомых взаимосвязанных параметрических зависимостей в виде номографических вычислительных « таблиц. При этом в блоке 11 синхронизации достаточно наличия простого цикла счета (последовательного счета импульсов) для формирования адреса записи/считывания. Таким образом, описанное совмещение нескольких функций связанных с формированием адресов (координат) записи и их содержимого по каждому из данных адресов, обеспечивает наиболее высокое быстродействие получения искомых графических образов.

Режим вывода сформированных графических образов на РУ 16 может быть осуществлен на основе использования стандартных средств, например, используя ЭЛТ с интерфейсным блоком в виде буферного ЗУ. При этом, если качество строк (разрешение) ЭЛТ равно V, а количество точек в строке п, то объем буферного ЗУ должен составлять п V. Режим вывода в этом случае будет осуществляться по аналогии режима ввода, при одном дополнительном условии согласования его начала с началом кадрового синхроимпульса.

Таким образом, в сравнении с устройством-прототипом предложенный способ и устройство позволяют регистрировать информацию в виде многомерных параметрических бинарных полей, например, в виде номографических образов вычислительных таблиц, которые представляют образ (сечение) пространства параметров для заданного интервала времени и их взаимное влияние (взаимосвязь), на заданном множестве (допустимом множестве) изменения их амплитудных значений.

Формулаизобретения 1. Способ многоканальной регистрации результатов измерений, заключающийся в измерении сигналов по каждому каналу, цифровом преобразовании результатов измерений по каждому каналу, запоминании полученных результатов с последующей их регистрацией, при этом при измерении производят квантование аналоговых сигналов по нескольким ступеням с постоянным шагом, отличающийся тем, что, с целью повышения информативности регистрации за счет отображения многомерных зависимостей в виде бинарных полей, перед изменением каналы входных аналоговых сигналов разделяют на первую и вторую группы независимых и зависимых сигналов соответственно, затем одновременно с измерением сигналов по каждому каналу производят комбинаторный опрос соответствующего числа каналов, сигналы первой группы каналов измеряют с учетом оценки значений разброса их верхних и нижних пределов изменения на заданном временном интервале, значения сигналов второй группы каналов запоминают при соответствующих фиксированных комбинациях значений сигналов первой группы каналов, а перед регистрацией производят сжатие полученных значений на основе канониче- ских преобразований третьего или четвертого порядков.

2. Устройство многоканальной регисдрации результатов измерений, содержащее

последовательно соединенные входные

шины, блок нормализаторов, коммутатор,

аналого-цифровой преобразователь и первое запоминающее устройство, регистрирующий блок, отличающееся тем, что, с целью повышения информативности регистрации за счет отображения многомерных

0 зависимостей в виде бинарных полей, в него введены блок выделения экстремума, блок преобразования, второе запоминающее устройство, блок управления и блок интерполирования, информационный вход которого

5 соединен с информационным входом блока выделения экстремума, первым входом блока дискретных приращений и выходом первого запоминающего устройства, управляющий вход которого подключен к первому

0 выходу блока управления, второй и третий выходы которого соединены с управляющими входами аналого-цифрового преобразователя и коммутатора соответственно, выходная шина и первый выход блока ин5 терлолирования подключены к первой входной информационной шине блока преобразования, первый вход которого соединен с первым выходом блока выделения экстремума и вторым входом блока дискрет0 ных приращений, третий, четвертый, пятый и шестой входы которого подключены к соответствующим четырем выходам блока масштабирования, первый и второй выходы которого соединены соответственно с пер5 вым и вторым входами блока управления, четвертый, пятый, шестой и седьмой выходы которого подключены к соответствующим четырем входам с четвертого по седьмой блока масштабирования, первый, второй и

0 третий входы которого соединены соответственно с четвертым, третьим и вторым выходами блока интерполирования, первый выход которого подключен к седьмому входу блока дискретных приращений, восьмой

5 вход которого соединен с восьмым выходом блока управления, первая и вторая выходные информационные шины которого подключены соответственно к второй информационной шине блока преобразова0 ния и первой выходной шине второго запоминающего устройства, вторая выходная шина которого соединена с третьей выходной информационной шиной блоки управления и первой входной шиной регистри5 рующего блока, вторая входная шина которого подключена к информационному выходу второго запоминающего устройства, первый и второй входы которого соединены с первым и вторым выходами блока дискрет- ных приращений соответственно, а третий.

четвертый, пятый и шестой входы - с соответствующими выходами, с первого по четвертый, блока преобразования, седьмой выход блока управления подключен к первому входу блока выделения экстремума.

второй выход которого соединен с восьмым входом блока масштабирования, третий, пятый и седьмой выходы которого подключены соответственно к второму, третьему и четвертому входам блока преобразования.

ч. 8 9 11 t t (Ј H tit/ fff lie, 1 t/g

Фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ РЕГИСТРАЦИИ СОСТОЯНИЯ ПАРАМЕТРОВ КОНТЕЙНЕРА ПО ПУТИ ЕГО СЛЕДОВАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2006 |

|

RU2325621C1 |

| СПОСОБ ИНТЕРАКТИВНОГО ПОИСКА В РАСПРЕДЕЛЕННЫХ ВЫЧИСЛИТЕЛЬНЫХ СЕТЯХ И ИНФОРМАЦИОННО-ПОИСКОВАЯ СИСТЕМА ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2006 |

|

RU2329533C2 |

| СПОСОБ РАСПРЕДЕЛЕННОГО МОНИТОРИНГА КОНТЕЙНЕРОВ И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2007 |

|

RU2329470C1 |

| СПОСОБ ГЕНЕРАЦИИ И ПРИЕМА СООБЩЕНИЙ О НЕСАНКЦИОНИРОВАННОМ ДОСТУПЕ К СОДЕРЖИМОМУ КОНТЕЙНЕРА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2006 |

|

RU2344484C2 |

| СПОСОБ ГЕНЕРАЦИИ БАЗ ЗНАНИЙ ДЛЯ СИСТЕМ ВЕРИФИКАЦИИ ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ РАСПРЕДЕЛЕННЫХ ВЫЧИСЛИТЕЛЬНЫХ КОМПЛЕКСОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2006 |

|

RU2364930C2 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1339890A1 |

| Контроллер измерительного преобразователя | 1988 |

|

SU1541632A1 |

| Устройство для определения оптимальных траекторий | 1983 |

|

SU1223240A1 |

| СПОСОБ И УСТРОЙСТВО ОПРЕДЕЛЕНИЯ КООРДИНАТ ИСТОЧНИКОВ РАДИОИЗЛУЧЕНИЙ | 2012 |

|

RU2510044C1 |

| Контроллер измерительного преобразователя | 1987 |

|

SU1462357A1 |

6

Фиг. 4

i {3 u « {iz Ъз /у «

Фиг.5

4f

I I I I I I

yxft w/tj УХ® У cry

- Фиг 6

| tt7ff()ff3

I I

t

УХ fry YV(J/

HJ

«л

I

CD

I

Авторы

Даты

1992-07-15—Публикация

1990-10-31—Подача