ТИ

сл

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля по модулю умножения комплексных чисел | 1986 |

|

SU1386997A1 |

| Устройство для умножения двоичных чисел | 1990 |

|

SU1765839A1 |

| Устройство для умножения двоичных чисел | 1988 |

|

SU1532918A1 |

| Устройство для умножения двоичных чисел | 1988 |

|

SU1587498A1 |

| Устройство для умножения | 1987 |

|

SU1522194A1 |

| Устройство для контроля умножения двоичных чисел по модулю три | 1988 |

|

SU1774337A1 |

| Устройство для умножения двоичных чисел | 1988 |

|

SU1509877A1 |

| Арифметическое устройство для быстрого преобразования Фурье | 1986 |

|

SU1327120A1 |

| Устройство для контроля по модулю три умножения комплексных чисел | 1987 |

|

SU1434438A1 |

| Устройство для умножения двоичных чисел | 1987 |

|

SU1439579A1 |

Устройство относится к области вычислительной техники и позволяет перемножать два комплексных числа. Цель изобретения - сокращение аппаратурных затрат - достигается за счет использования только двух блоков умножения. Устройство для умножения содержит семь регистров 1-7, блок 8 управления, два коммутатора 9, 10, два блока 12, 13 умножения, два блока 13, 14 сложения и два элемента И 15, 16. Особенностью устройства является отсутствие преобразователей кода при приеме и выдаче данных на входах и вьГходах устройства. Сомножители подаются на входы устройства в последовательном коде. 2 ил.

f

VI сл

4 00

Изобретение относится к вычислительной технике и может быть использовано в цифровых устройствах для выполнения операции умножения комплексных чисел.

Цель изобретения - сокращение аппаратурных затрат.

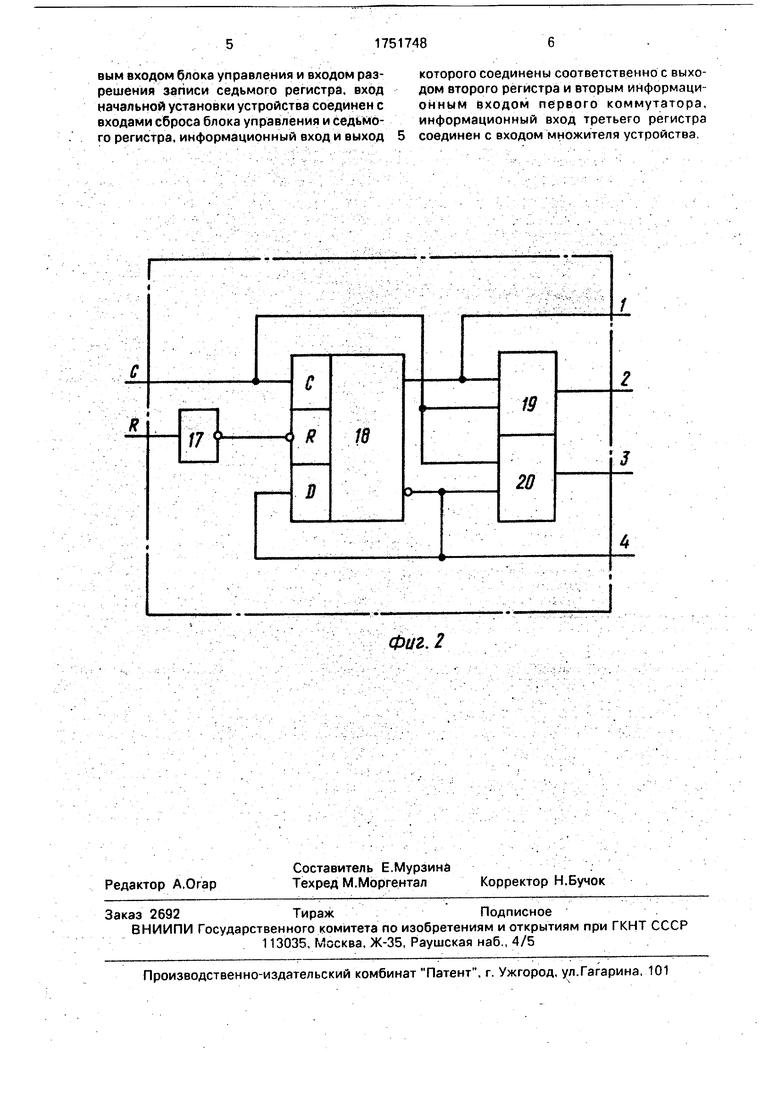

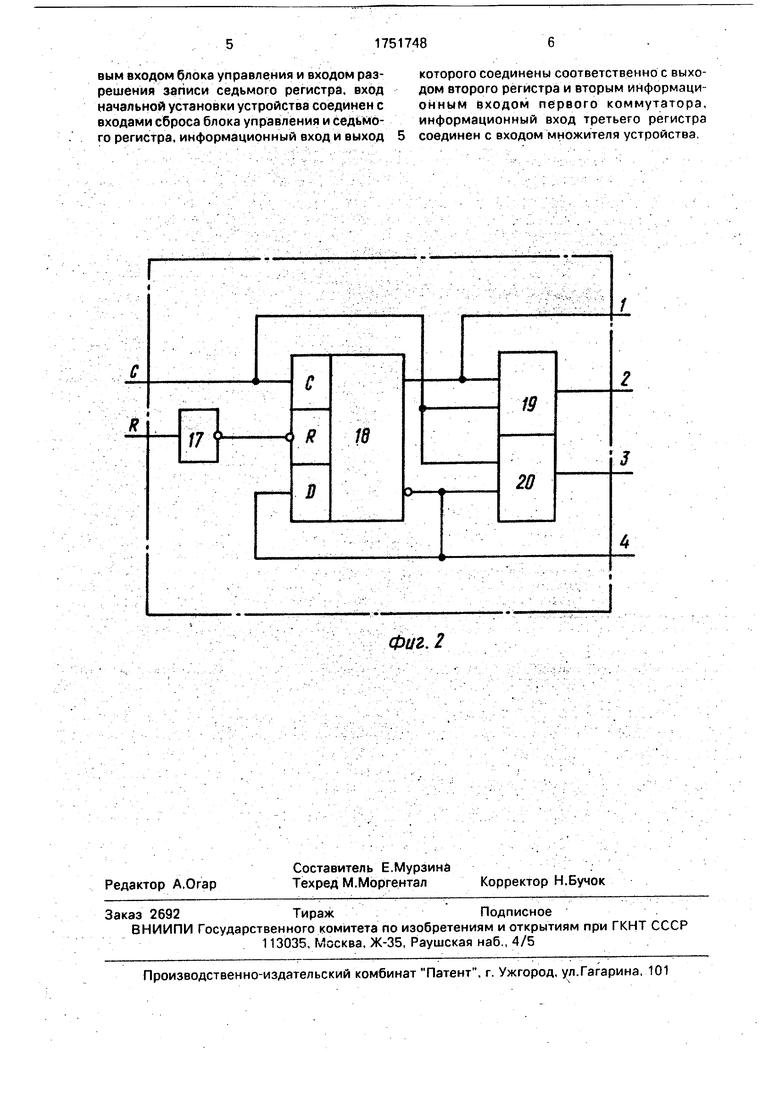

На фиг. 1 приведена функциональная схема устройства; на фиг 2 - функциональная схема блока управления.

Устройство для умножения (фиг. 1) содержит регистры 1-7, блок 8 управления, коммутаторы 9 и 10, блоки 11 и 12 умножения, блоки 13 и 14 сложения, элементы И 15 и 16.

Блок управления (фиг. 2) образуют элемент НЕ 17, триггер 18 и элементы И 19 и 20.

Устройство работает следующим образом,

В начальный момент времени на вход начальной установки устройства приходит сигнал, устанавливающий устройство в исходное состояние, т.е. обнуляет все регистры множимого и множителя и триггер в блоке 8 управления.

После начальной установки на входы множимого /5 и множителя V устройства параллельно поступают соответственно множимое и множитель, причем сначала их действительные части, а затем мнимые. Под действием тактовых импульсов они продвигаются по соответствующим цепочкам регистров множимого и множителя. Таким образом, в начальный момент времени под действием тактового импульса в первые регистры множимого и множителя записываются действительные части и Vi соответственно множимого и множителя. Со следующим тактовым импульсом они продвигаются во вторые регистры и. т. д., а в первые с этим же тактовым импульсом записываются мнимые части fa и V2 соответственно множимого и множителя

В первом блока 11 умножения перемножаются сначала действительные, а затем мнимые части множимого и множителя.

Одновременно с мнимыми частями во втором блоке 12 умножения начинают перемножаться действительная часть Умножителя и мнимая часть fh, множимого, а в следующем такте - действительная часть Д| множимого и мнимая часть V2 множителя.

Таким образом, с выхода первого блока 11 умножения на вход первого блока 13 сложения поступают составляющие действительной части результата V1 и fa V2, с выхода второго блока 12 умножения на вход второго блока 14 сложения поступают составляющие мнимой части результата

/fc V1 и V2 Через второй коммутатор 10 на выход устройства выдается результат в виде последовательности действительной и мнимой частей

Управляет работой устройства блок 8

управления, который вырабатывает управляющие сигналы для коммутаторов 9 и 10 элементов И 15 и 16

Формула изобретения

Устройство для умножения комплексных чисел, содержащее первый и второй блоки умножения, первый и второй блоки сложения и с первого по шестой регистры, входы разрешения записи которых соединены с тактовым входом устройства, вход начальной установки которого соединен с входами сброса первого, второго третьего и четвертого регистров, выходы первого и второго блоков умножения соединены соответственно с первыми входами первого и второго блоков сложения, отличающее- с я тем, что, с целью сокращения аппаратурных затрат, в него введены седьмой регистр, два коммутатора, блок управления и два

элемента И, выходы которых соединены соответственно с вторыми входами первого и второго блоков сложения, вход множимого устройства соединен с информационным входом первого регистра, выход которого

соединен с информационным входом второго регистра, первым информационным входом первого коммутатора и первым входом первого блока умножения, второй вход которого соединен с выходом третьего регистра и информационным входом четвертого регистра, выход которого соединен с первым входом второго блока умножения, второй вход которого соединен с выходом первого коммутатора, управляющий вход

которого соединен с первым выходом блока управления, управляющим входом второго коммутатора и первым входом первого элемента И, второй вход которого соединен с выходом пятого регистра, информационный

вход которого соединен с инверсным выходом первого блока сложения и первым информационным входом второго коммутатора, второй информационный вход которого соединен с выходом второго блока

сложения и информационным входом шестого регистра, выход которого соединен с первым входом второго элемента И. входы сброса пятого и шестого регистров соединены соответственно с вторым и третьим выходами блока управления, четвертый выход которого соединен с вторым входом второго элемента И, выход второго коммутатора соединен с выходом результата устройства, тактовый вход которого соединен с тактовым входом блока управления и входом разрешения записи седьмого регистра, вход начальной установки устройства соединен с входами сброса блока управления и седьмого регистра, информационный вход и выход 5 соединен с входом множителя устройства

лп Г

17

которого соединены соответственно с выходом второго регистра и вторым информационным входом первого коммутатора, информационный вход третьего регистра

19

3

о-

20

Фиг. 2

| Устройство для умножения комплексных чисел | 1986 |

|

SU1388851A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

| Каляев А | |||

| В | |||

| Многопроцессорные системы с программируемой архитектурой, М.: Радио и связь, 1984, с | |||

| Затвор для дверей холодильных камер | 1920 |

|

SU182A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1992-07-30—Публикация

1990-07-02—Подача