Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении систем обработки данных с повышенной достоверностью.

Целью изобретения является повышение быстродействия устройства.

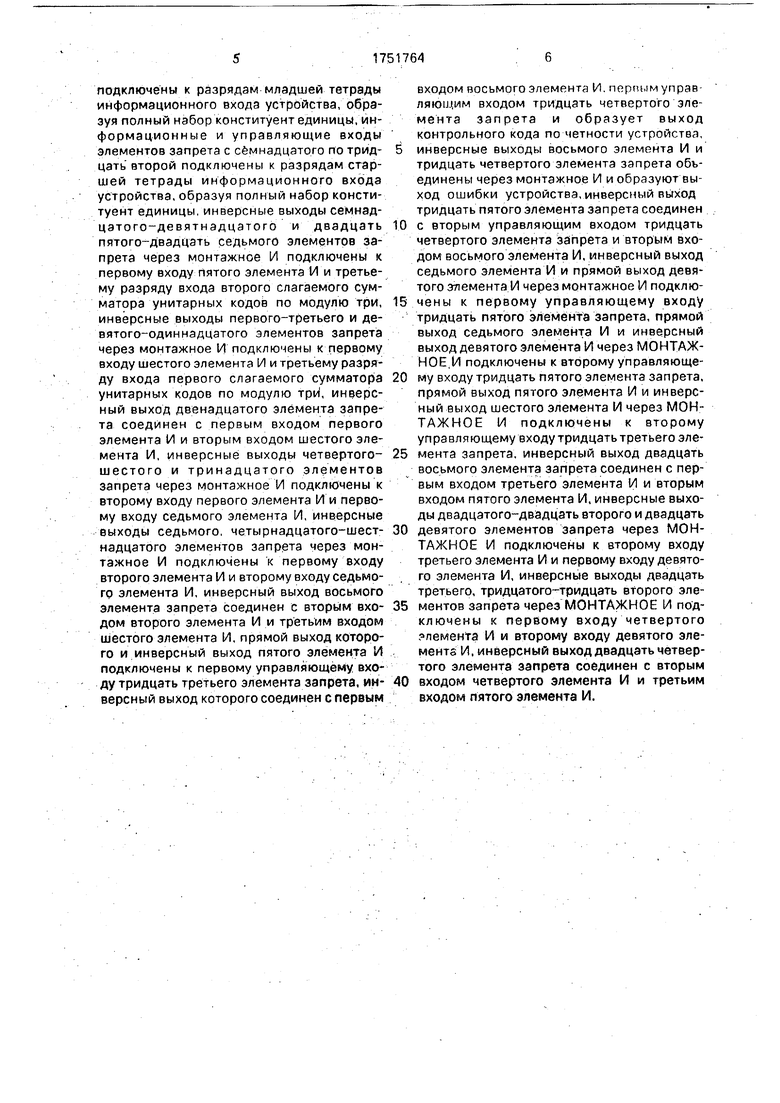

На фиг.1 приведена функциональная схема устройства; на фиг.2 - пример схемного решения сумматора унитарных кодов по модулю три.

Устройство (фиг.1) содержит элементы запрета 1-35, элементы И 36-44, сумматор 45 унитарных кодов по модулю три, информационный вход 46 устройства, выход 47 ошибки и выход 48 контрольного кода по четности устройства, выход 49 контрольного кода по модулю три устройства.

Сумматор 45 унитарных кодов по модулю три (фиг,2) содержит элементы запрета 50-58 и элементы И 59-61,

Устройство предназначено для контроля восьмиразр ядного слова.

Устройство работает следующим образом.

Контролируемое число поступает на информационный вход 46 устройства. Элементы запрета 1-16 и элементы И 37, 38 образуют сумматор унитарных кодов по модулю три, на выходе которого формируется инверсное значение контрольного кода по модулю три младшей тетрады контролируемого слова.

Элементы запрета 17-32 и элементы И 40, 41 образуют сумматор унитарных кодов по модулю три, на выходах которого формируется инверсное значение контрольного кода по модулю три старшей тетрады контролируемого слова.

Совокупности элементов запрета 1-16 и элементов запрета 17-32 представляют собой дешифраторы шестнадцать из четырех с инверсными выходами.

С помощью элементов И 36, 39 и элемента запрета 35 формируется контрольный код по четности контролируемого слова, который поступает на выход 48 устройства.

С помощью элемента запрета 33 и элементов И 42, 43 формируется предсказанный код четности путем вычисления, заключающегося в выделении инверсных значений кодов сумматоров унитарных кодов по модулю три, значения кодов на выходе которых совпадают с инверсными значениями контрольных кодов по четности тетрад контролируемого слова. Формирование предсказанного кода четности Fn ч определяется уравнением

.-- -гРпч К11 -K21 + Ki2 -K22,

где Ki1 2 - инверсное значение кода на выходе сумматора унитарных кодов младшей

(старшей) тетрады, значение на L-м выходе которого совпадает с инверсными значениями контрольных кодов по четности тетрад контролируемого слова.

С помощью элемента запрета 34 и элемента И 44 производится сравнение предсказанного кода четности с полученным. При несовпадении этих кодов на выходе ошибки 47 устройства формируется сигнал единичного уровня, свидетельствующий об

ошибке в устройстве.

Следует отметить, что объединение выходов нескольких элементов реализует логическую функцию И.

Формула изобретения

Устройство для контроля информации по модулю, содержащее шесть элементов И и сумматор унитарных кодов по модулю три, причем выходы первого и второго элементов И соединены соответственно с первым и вторым разрядами входа перого слагаемого сумматора унитарных кодов по модулю три, выход которого является выходом контрольного кода по модулю три устройства,

выходы третьего и четвертого элементов И соединены соответственно с первым и вторым разрядами входа второго слагаемого сумматора унитарных кодов по модулю три. отличающееся тем, что, с целью повышения быстродействия устройства, в него введены седьмой-девятый элементы

И и тридцать пять элементов запрета, причем информационные и управляющие входы элементов запрета с первого по шестнадцатый

подключены к разрядам младшей тетрады информационного входа устройства, образуя полный набор конституент единицы, ин- формационные и управляющие входы элементов запрета с семнадцатого по тридцать второй подключены к разрядам старшей тетрады информационного входа устройства, образуя полный набор консти- туент единицы, инверсные выходы семнад- цэтого-девятнадцатого и двадцать пятого-двадцать седьмого элементов запрета через монтажное И подключены к первому входу пятого элемента И и третьему разряду входа второго слагаемого сумматора унитарных кодов по модулю три, инверсные выходы первого-третьего и де- вятого-одиннадцатого элементов запрета через монтажное И подключены к первому входу шестого элемента И и третьему разряду входа первого слагаемого сумматора унитарных кодов по модулю три, инверсный выход двенадцатого элемента запрета соединен с первым входом первого элемента И и вторым входом шестого элемента И, инверсные выходы четвертого- шестого и тринадцатого элементов запрета через монтажное И подключены к второму входу первого элемента И и первому входу седьмого элемента И, инверсные выходы седьмого, четырнадцатого-шест- надцатого элементов запрета через монтажное И подключены к первому входу второго элемента И и второму входу седьмого элемента И, инверсный выход восьмого элемента запрета соединен с вторым входом второго элемента И и третьим входом шестого элемента И, прямой выход которого и инверсный выход пятого элемента И подключены к первому управляющему входу тридцать третьего элемента запрета, инверсный выход которого соединен с первым

входом восьмого элемента И. перпым управ ляющим входом тридцать четвертого элемента запрета и образует выход контрольного кода по четности устройства,

инверсные выходы восьмого элемента И и тридцать четвертого элемента запрета объединены через монтажное И и образуют выход ошибки устройства, инверсный выход тридцать пятого элемента запрета соединен

с вторым управляющим входом тридцать четвертого элемента запрета и вторым входом восьмого элемента И, инверсный выход седьмого элемента И и прямой выход девятого элемента I/I через монтажное И подключены к первому управляющему входу тридцать пятого элемента запрета, прямой выход седьмого элемента И и инверсный выход девятого элемента И через МОНТАЖНОЕ И подключены к второму управляющему входу тридцать пятого элемента запрета, прямой выход пятого элемента И и инверсный выход шестого элемента И через МОН- ТАЖНОЕ И подключены к второму управляющему входу тридцать третьего элемента запрета, инверсный выход двадцать восьмого элемента запрета соединен с первым входом третьего элемента И и вторым входом пятого элемента И, инверсные выходы двадцэтого-двадцать второго и двадцать

девятого элементов запрета через МОНТАЖНОЕ И подключены к второму входу третьего элемента И и первому входу девятого элемента И, инверсные выходы двадцать третьего, тридцатого-тридцать второго элементов запрета через МОНТАЖНОЕ И под- ключены к первому входу четвертого элемента И и второму входу девятого элемента И, инверсный выход двадцать четвертого элемента запрета соединен с вторым

входом четвертого элемента И и третьим входом пятого элемента И.

#

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля информации по модулю | 1989 |

|

SU1751763A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Устройство для сложения-вычитания чисел с плавающей запятой | 1989 |

|

SU1656526A2 |

| Сумматор в знакоразрядной позиционно-остаточной системе счисления | 1986 |

|

SU1383349A1 |

| Операционный модуль | 1984 |

|

SU1406592A1 |

| УСТРОЙСТВО ДЛЯ ПРИВЕДЕНИЯ ФУНКЦИЙ К МУЛЬТИПЛИКАТИВНОМУ АЛГОРИТМУ ВЫЧИСЛЕНИЙ | 1990 |

|

RU2028659C1 |

| Последовательный сумматор кодов с иррациональными основаниями | 1987 |

|

SU1439577A1 |

| Преобразователь параллельного унитарного кода в дифференциально-разностный код | 1988 |

|

SU1647907A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1137541A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при обработке данных с повышенной достоверностью. Цель изобретения - повышение быстродействия устройства. Устройство содержит элементы запрета 1-35, элементы И 36-44, сумматор 45 унитарных кодов по модулю три. Контролируе

| Устройство для формирования остатка по модулю три | 1982 |

|

SU1084799A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Бетонный полый камень | 1925 |

|

SU2366A1 |

Авторы

Даты

1992-07-30—Публикация

1989-11-17—Подача