Изобретение относится к вычислительной технике, в частности к запоминающим устройствам.

Целью изобретения является упрощение устройства.

На чертеже представлена функциональная Јхёма предлагаемого устройства.

Запоминающее устройство с контролем цепей коррекции ошибок содержит регистр 1 контрольных разрядов, выходной регистр 2, блок 3 анализа синдрома, блок А коррекции, коммутатор 5 данных, входной регистр 6, блок 7 кодирования, регистр 8 расстояния, блок 9 синхронизации, элемент И 10, двоичный счетчик 11, элемент И 12 и накопитель 13.

На чертеже обозначены: 14 - входы начальной установки устройства; 15 - адресные входы устройства; 16 - информационные входы-выходы устройства.

Регистр 1 контрольных разрядов и выходной регистр 2 предназначены для приема информации с накопителя при считывании.

Блок 3 анализа синдрома выполняет проверку правильности считанного кода и определяет тип ошибки. Узел состоит из схемы формирования синдрома, дешифратора номера разряда и схемы формирования сигналов ошибки.

Блок 4 коррекции корректирует информацию в разряде, в котором обнаружена ошибка, и состоит из элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.

Коммутатор 5 данных предназначен для коммутации информации с выхода блока коррекции или регистра диагностики на двунаправленную магистраль данных.

Входной регистр б служит для приема информации с магистрали данных.

Блок 7 кодирования формирует в соответствии с кодом Хемминга контрольные разряды, которые поступают на вход накопителя 13. Блок кодирования может быть реализован на ИМС К555ВЖ1.

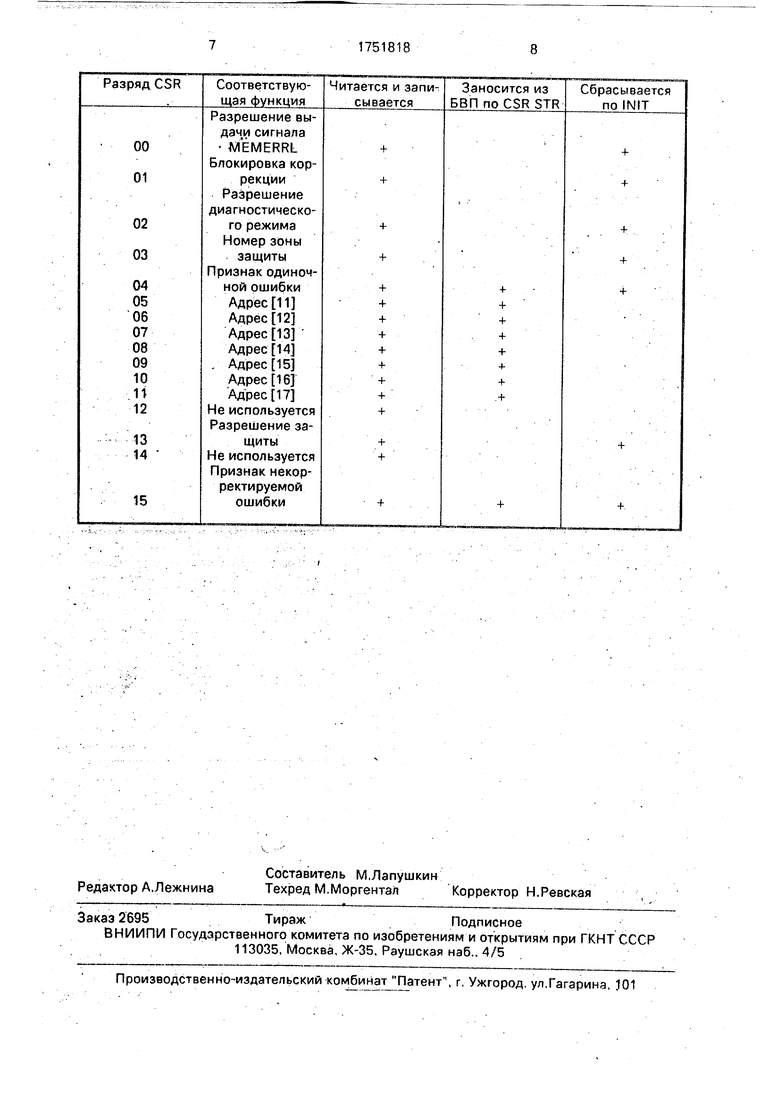

Регистр 8 состояния предназначен для переключения режимов работы и фиксации диагностической информации.

Форматы регистра состояния представлены в таблице.

Блок 9 синхронизации обеспечивает взаимодействие узлов запоминающего устройства и состоит из схемы анализа адреса, селектора запросов, дешифратора операций и регистра сдвига.

Счетчик 11 и два элемента И 10 и 12 предназначены для блокировки через обращение к накопителю в диагностическом режиме записи информации в регистр контрольных разрядов.

Устройство работает следующим образом.

В основном рабочем режиме регистр 8 состояния обнулен, на установочный вход

счетчика 11 поступает нулевой уровень, который устанавливает единичный уровень на инверсном выходе счетчика, разрешающий запись информации в регистр 1 контрольных разрядов одновременно с записью в

0 регистр 2 по управляющему сигналу с выхода блока 9 при считывании информации с накопителя 13. С выходов регистра 1 и 2 информация поступает на блок 3 анализа синдрома, который осуществляет свертку

5 входной информации по модулю 2 При наличии ошибки блок 3 анализа синдрома формирует код, который поступает на вход дешифратора. С выхода дешифратора сигнал, соответствующий номеру разряда, в ко0 тором обнаружена ошибка, поступает на вход блока 4 коррекции, на другой вход которого поступают данные с выхода регистра 2. С выхода блока 4 коррекции информация поступает на вход коммутатора 5 данных.

5При наличии ошибок блок анализа синдрома формирует также сигналы ошибки, которые заносятся-в регистр 8 состояния.

В диагностическом режиме работы по управляющему сигналу блока 9 синхронизэ0 ции разряд режима диагностики регистра 8 состояния устанавливается в единичное состояние, т.е. разрешается прохождение сигнала с выхода блока 9 синхронизации, стробирующего запись информации в ре5 гистр 2 через элемент И 12 Производится запись информации в регистр 1. Двоичный счетчик 11 изменяет свое состояние по окончании сигнала записи в регистр. Нулевой сигнал с инверсного выхода счетчика 11

0 блокирует прохождение сигнала с выхода блока 9 синхронизации на стробирующий вход регистра 1 контрольных разрядов. Таким образом, при 2п-1-м считывании информации с накопителя 13 (,2,3,..} после установки в

5 единичное состояние разряда регистра 8 состояния в регистр 1 контрольных разрядов записывается информация одновременно с занесением информации в регистр 2. При 2п- м считывании информации с накопителя 13

0 заносится только в регистр 2, информация в регистре 1 контрольных разрядов не изменяется и на вход блока 3 анализа синдрома поступает информационное слово, которое считано с накопителя 13 при 2п-м обращении,

5 и контрольное слово, которое считано с накопителя 13 при 2п-м обращении. Так как запись информации в накопитель 13 в режиме диагностики осуществляется так же, как в основном режиме, то в накопитель 13 записаны массивы информации, присчитывании которых в регистр 2 заносится информация, отличающаяся при 2п-1-м или 2(2 п)-м об ращениях соответственно в первом цикле на 1 разряд, во втором цикле - на 2 разряда и так далее, количество циклов зависит от количества корректируемых или фиксируемых ошибок, на которые могут реагировать используемые коды Хэмминга. При каждом 2п-м считывании с накопителя 13 в первом цикле в регистр 1 контроля будет занесен контрольный код предыдущего 2п-1-го считывания информации, отличной на один разряд от информации, занесенной при 2п- м считывании в регистр 2, поэтому блок 3 анализа синдрома при 2п-м обращении формирует сигнал однократной ошибки,

Информация с выхода блока 4 коррекции поступает на вход коммутатора 5 данных, с выхода которого по управляющим сигналам блока 9 синхронизации поступает на вход регистра 6. При правильной работе схем коррекции в первом цикле проверки в регистре 6 информация при 2п-м обращении к накопителю 13 будет равна информации при 2п-1-м обращении к накопителю м в регистр 8 состояния будет заноситься сигнал Однократная ошибка. При втором цикле проверки в каждом 2п-м считывании с накопителя 13 в регистр 8 состояния будет заноситься сигнал Двукратная ошибка. Формула изобретения Запоминающее устройство с контролем цепей коррекции ошибок, содержащее регистр контрольных разрядов, выходной регистр, блок анализа синдрома, блок коррекции, коммутатор данных, входной регистр, блок кодирования, регистр состояния, блок синхронизации, накопитель, информационные входы входного регистра соединены с информационными входами накопителя, входами блока кодирования, входами первой группы регистра состояния и выходами коммутатора данных и являются информационными входами-выходами устройства, информационные выходы входного регистра соединены с информационными входами первой группы коммутатора данных, первый и второй управляющие входы которого соединены соответственно с первым и вторым выходами блока синхронизации, третий выход которого соединен с уп равляющим входом блока кодирования, выходы которого соединены с входами контрольных разрядов накопителя, инфор- 5 мационные выходы которого соединены с информационными входами выходного регистра, информационные выходы которого соединены с информационными входами первой группы блока анализа синдрома и 0 входами первой группы блока коррекции, входы второй группы которого соединены с информационными выходами блока анализа синдрома, информационные входы второй группы которого соединены с выходами 5 регистра контрольных разрядов, входы которого соединены с выходами контрольных разрядов накопителя, управляющий вход которого соединен с четвертым выходом блока синхронизации, пятый выход которо0 го соединен с входом синхронизации входного регистра, выходы контрольных разрядов блока анализа синдрома соединены с входами второй группы регистра состояния, вход синхронизации которого

5 соединен с шестым выходом блока синхронизации, группа входов которого является входами задания начальных условий устройства, адресные входы накопителя - адресными входами устройства, выходы блока

0 коррекции соединены с входами второй группы коммутатора данных, входы третьей группы которого соединены с соответствующими выходами регистра состояния, седьмой выход блока синхронизации соединен с

5 входом синхронизации выходного регистра, отличающее с я тем, что, с целью упрощения устройства, в него введены двоичный счетчик, первый и второй элементы И, выход разрешения режима диагностики

0 регистра состояния соединен с первым входом первого элемента И и установочным входом двоичного счетчика, вход синхронизации которого соединен с выходом первого элемента И, второй вход которого соединен

5 с седьмым выходом блока синхронизации и первым входом второго элемента И, второй вход которого соединен с инверсным выходом двоичного счетчика, выход второго элемента И соединен с входом синхронизации

0 регистра контрольных разрядов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и коррекции ошибок | 1990 |

|

SU1783583A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Запоминающее устройство с исправлением ошибок | 1981 |

|

SU982098A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Запоминающее устройство | 1983 |

|

SU1246137A1 |

| Запоминающее устройство с контролем | 1989 |

|

SU1624535A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2008 |

|

RU2383104C2 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1265860A1 |

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

Изобретейие относится к вычислительной технике, в частности к запоминающим устройствам. Целью изобретения является упрощение устройства. Устройство содержит регистр 1 контрольных разрядов, выходной регистр 2, блок 3 анализа синдррма, блок 4 коррекции, коммутатор 5 данных, входной регистр 6, блок 7 кодирования, регистр 8 состояния, блок 9 синхронизации, первый 10 и второй 12 элементы И, двоичный счетчик 11 и накопитель 13. Устройство обнаруживаети исправляет ошибки в соответствии с применяемым кодом Хэемминга Устройство также позволяет проводить контроль цепей коррекции ошибок Отсутствие связей с выхода регистра состояния на вход блока кодирования позволяет упростить устройство 1 ил . 1 табл. N-f Ё сл 00 00

| Устройство для тестового контроля памяти | 1982 |

|

SU1083234A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Техническое описание | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство и работа | |||

| Устройство двукратного усилителя с катодными лампами | 1920 |

|

SU55A1 |

Авторы

Даты

1992-07-30—Публикация

1988-12-20—Подача