Изобретение относится к импульсной технике и может быть использовано в системах приемопередачи цифровой информации,

Целью изобретения является расширение области применения за счет возможности преобразования последовательного кода.

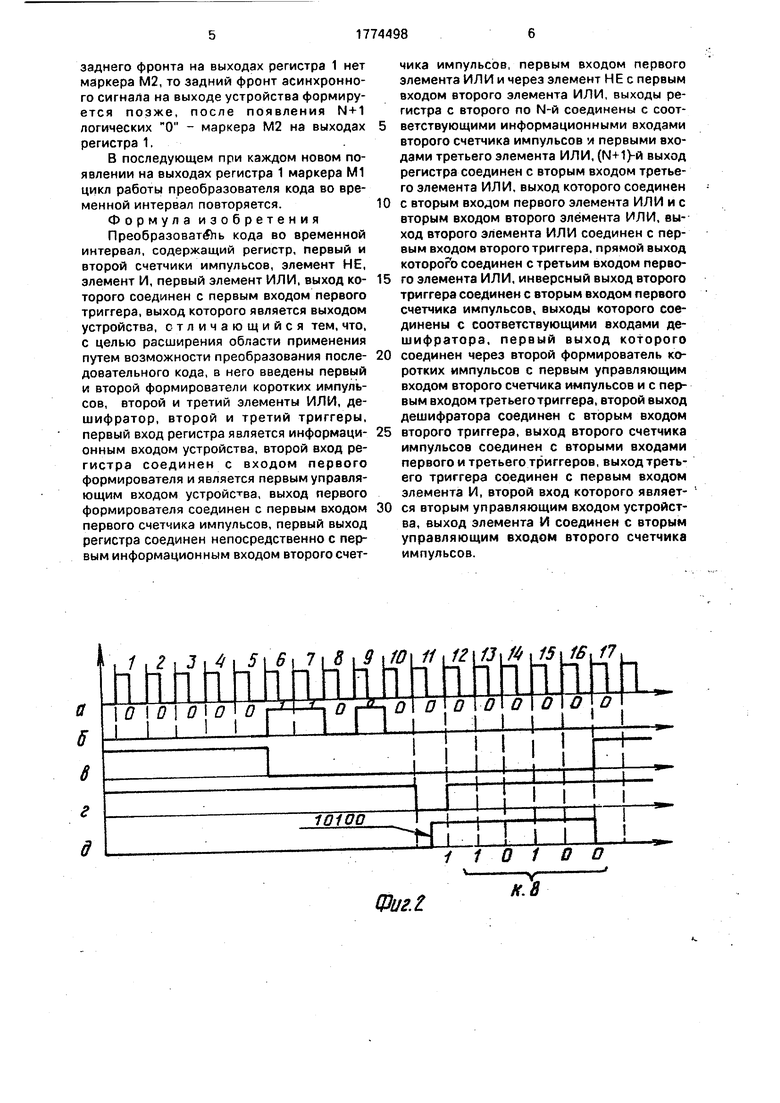

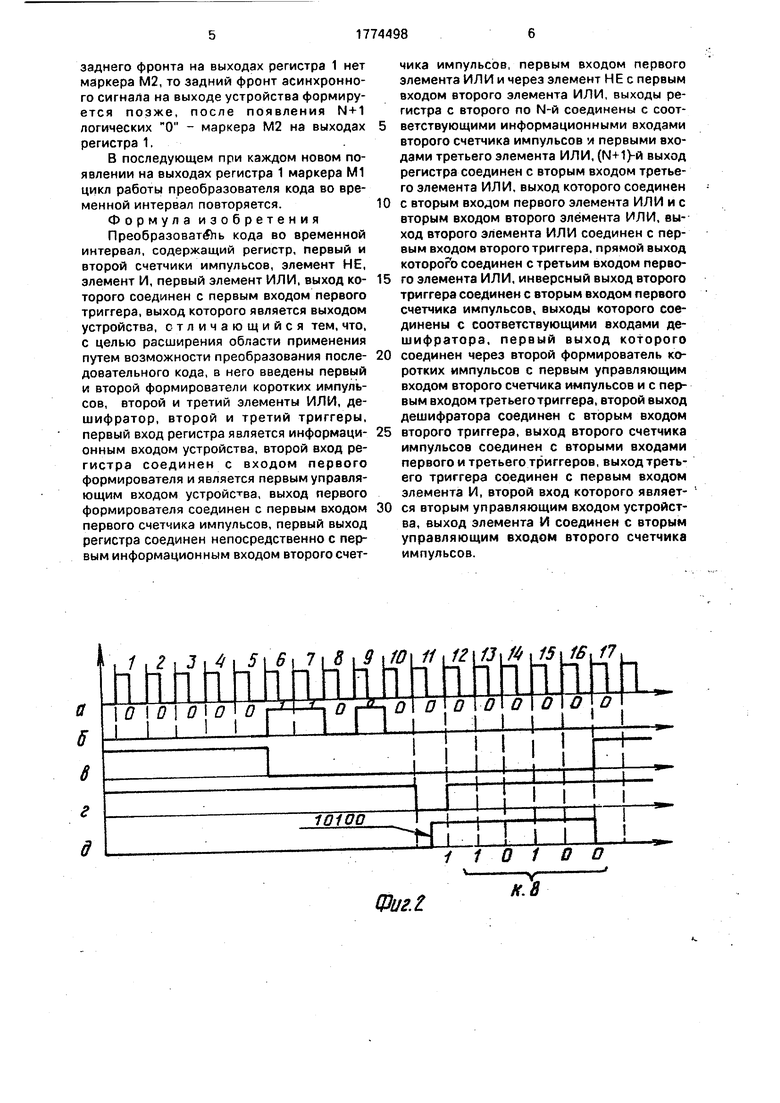

На фиг. 1 представлена функциональная схема преобразователя кода во времен- ной интервал; на фиг. 2 приведены временные диаграммы, поясняющие работу устройства.

Преобразователь кода во временной интервал содержит регистр 1, первый и второй счетчики 2 и 3, дешифратор 4, элемент НЕ 5, элемент И 6, первый, второй и третий элементы ИЛИ 7, 8 и 9, первый, второй и третий триггеры 10, 11 и 12, первый и второй формирователи 13 и 14 коротких импульсов.

На первый управляющий вход (фиг. 1а, 2а) подается тактовая частота f, а последовательность бит информации поступает на вход устройства (фиг. 16, 26).

Регистр 1 включен в режиме последовательного занесения со сдвигом вправо.

На второй управляющий вход элемента И 6 подается частота .

Второй счетчик 3 - реверсивный.

Тактовая частота f и частота, подаваемая на второй управляющий вход второго счетчика 3, ттакт хМ между собой синхронизированы.

В первом формирователе 13 организуются короткие импульсы по переднему фронту каждого импульса тактовой частоты f. По задним фронтам этих коротких импульсов срабатывает первый счетчик 2.

На втором формирователе 14 коротких импульсов по заднему фронту импульса на первом выходе дешифратора 4 формируется короткий отрицательный импульс.

Работает преобразователь кода во временной интервал следующим образом.

При включении питания в начальный момент времени обнуляются регистр 1, третий триггер 12 и второй триггер 11. В регистр 1 начинают поступать биты информации и сдвигаться на его выходах по передним фронтам тактовых импульсов. Когда на выходах регистра 1 появляется маркер М1 (комбинация нулевой, затем одной логической 1), на выходах третьего элемента ИЛИ 9, элемента НЕ 5 и соответственно входах второго элемента ИЛИ 8 по- являются логические О, которые формируют логический О на выходе второго элемента ИЛИ 8 и первом входе второго триггера 11, в результате чего последний устанавливается в единичное состояние и,

тем самым, снимает блокировку первого счетчика 2. По задним фронтам коротких импульсов с выхода первого формирователя 13 коротких импульсов первый счетчик 2

начинает считать тактовые импульсы, причем свой счет начинает с импульса, на который на выходах регистра 1 появился маркер Ml.

Когда первый счетчик 2 отсчитает N+1

0 импульсов, на первом выходе дешифратора 4 появляется логический О (логический О на первом выходе дешифратора 4 указывает на то, что маркер М1 выведен и комбинация на первых N выходах регистра 1 - код вре5 мени) и короткий ноль на выходе второго формирователя 14 коротких импульсов - разрешение записи во второй счетчик 3 кода времени с выходов N первых разрядов регистра 1. В результате код времени запи0 сывается во второй счетчик 3 и, так как короткий ноль на выходе второго формирователя 14 коротких импульсов и первом входе третьего триггера 12 перебрасывает третий триггер 12 в единичноесосто5 яние, с второго управляющего входа второго счетчика 3 {счетного входа в режиме вычитания) снимается блокировка, и он готов к работе в режиме вычитания. По заднему фронту каждого импульса с второго

0 управляющего входа код времени во втором счетчике 3 уменьшается на единицу в двоичном счете до обнуления. В момент обнуления на выходе второго счетчика 3 (выходе обратного переноса реверсивного счетчика)

5 появляется логический О, который устанавливает первый триггер 10 в единичное состояние - на выходе устройства (фиг. 2а) формируется передний фронт декодируемого асинхронного сигнала, обнуляется третий

0 триггер 12, блокируется второй счетчик 3.

Когда первый счетчик 2 отсчитает 2 (N+1) импульсов, на втором выходе дешифратора 4 появляется логический О, который переводит второй триггер 11 в нулевое

5 состояние и, тем самым, блокирует первый счетчик 2 и организует дежурный логический О на третьем входе первого элемента ИЛИ 7 - разрешение формирования заднего фронта. Если в это время на выходах

0 регистра 1 оказывается маркер M2-(N+1) логических О, то на первом и втором входах первого элемента ИЛИ 7 тоже оказываются логические О, которые организуют на выходе первого элемента ИЛИ 7 и первом вхо5 де первого триггера 10 логический О - первый триггер 10 перебрасывается в нулевое состояние, формируется задний фронт декодируемого асинхронного сигнала на выходе устройства (фиг. 2а), Если при появлении сигнала разрешения формирования

заднего фронта на выходах регистра 1 нет маркера М2, то задний фронт асинхронного сигнала на выходе устройства формируется позже, после появления N+1 логических О - маркера М2 на выходах регистра 1.

В последующем при каждом новом появлении на выходах регистра 1 маркера М1 цикл работы преобразователя кода во временной интервал повторяется. Формула изобретения Преобразователь кода во временной интервал, содержащий регистр, первый и второй счетчики импульсов, элемент НЕ, элемент И, первый элемент ИЛИ, выход ко- торого соединен с первым входом первого триггера, выход которого является выходом устройства, отличающийся тем, что, с целью расширения области применения путем возможности преобразования после- довательного кода, в него введены первый и второй формирователи коротких импульсов, второй и третий элементы ИЛИ, дешифратор, второй и третий триггеры, первый вход регистра является информаци- онным входом устройства, второй вход регистра соединен с входом первого формирователя и является первым управляющим входом устройства, выход первого формирователя соединен с первым входом первого счетчика импульсов, первый выход регистра соединен непосредственно с первым информационным входом второго счетчика импульсов, первым входом первого элемента ИЛИ и через элемент НЕ с первым входом второго элемента ИЛИ, выходы регистра с второго по N-й соединены с соответствующими информационными входами второго счетчика импульсов и первыми входами третьего элемента ИЛИ, (М+1)-й выход регистра соединен с вторым входом третьего элемента ИЛИ, выход которого соединен с вторым входом первого элемента ИЛИ и с вторым входом второго элемента ИЛИ, выход второго элемента ИЛИ соединен с первым входом второго триггера, прямой выход которого соединен с третьим входом первого элемента ИЛИ, инверсный выход второго триггера соединен с вторым входом первого счетчика импульсов, выходы которого соединены с соответствующими входами дешифратора, первый выход которого соединен через второй формирователь коротких импульсов с первым управляющим входом второго счетчика импульсов и с первым входом третье го триггера, второй выход дешифратора соединен с вторым входом второго триггера, выход второго счетчика импульсов соединен с вторыми входами первого и третьего триггеров, выход третьего триггера соединен с первым входом элемента И, второй вход которого являет- ся вторым управляющим входом устройства, выход элемента И соединен с вторым управляющим входом второго счетчика импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода во временной интервал | 1990 |

|

SU1753512A1 |

| Устройство для передачи цифровой информации | 1990 |

|

SU1780192A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1988 |

|

SU1608679A1 |

| Селектор импульсов по длительности | 1986 |

|

SU1422383A1 |

| Устройство для передачи и приема телеметрической информации | 1986 |

|

SU1397956A1 |

| Устройство для выделения R-зубцов в электрокардиосигнале | 1990 |

|

SU1808306A1 |

| Устройство для отображения информации на экране электроннолучевой трубки | 1984 |

|

SU1257635A1 |

| Устройство для сопряжения ЭВМ с каналом связи | 1988 |

|

SU1656544A1 |

| УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ | 1991 |

|

RU2020608C1 |

| Способ маркирования информационных комбинаций в системах последовательной записи с двухчастотным кодированием и устройства записи и воспроизведения для его осуществления | 1987 |

|

SU1543445A1 |

Изобретение относится к импульсной технике и может быть использовано в системах приемопередачи цифровой информации. Целью изобретения является расширение области применения за счет возможности преобразования последовательного кода. Преобразователь содержит регистр 1, первый и второй счетчики 2 и 3, дешифратор 4, элеме.нт НЕ 5, элемент И 6. первый, второй и третий элементы ИЛИ 7, 8 и 9, первый, второй и третий триггеры 10,11 и 12, первый и второй формирователи 13 и 14 коротких импульсов. 2 ил. VI VI t ю 00 Фиг.1

| Преобразователь код-временной интервал | 1985 |

|

SU1305865A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь кода во временной интервал | 1985 |

|

SU1275776A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-11-07—Публикация

1990-02-28—Подача