1

(21)4888970/21

(22)10.12.90

(46) 15.09.92. Бюл. №34

(71)Научно-исследовательский и проектно- конструкторский институт автоматизированных систем управления транспортам газа

(72)Е.Н.Бантюков

(56)Авторское свидетельство СССР № 976426, кл. G 04 F 10/04, 1980.

(54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ВРЕМЕННЫХ ИНТЕРВАЛОВ В КОД

(57)Изобретение относится к измерительной технике, предназначено для определения длительностей временных интервалов, разграниченных импульсами импульсной последовательности.и может быть использовано в устройствах определения скорости, например скорости вращения вала двигателя. Цель - повышение надежности устройства. Устройство для преобразования временных интервалов в код содержит триггеры, генератор импульсов регистр сдвига, элемент И, счетчик импульсов, блок памяти, входную шину, кодовые шины. Цель достигается за счет новых связей в устройстве и за счет подключения шин сброса и нулевого сигнала 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многокоординатный цифровой интерполятор | 1984 |

|

SU1200246A1 |

| Генератор испытательных кодов | 1985 |

|

SU1322275A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Управляемый делитель частоты | 1982 |

|

SU1046936A1 |

| Устройство для записи информации в оперативную память | 1990 |

|

SU1751811A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1987 |

|

SU1522272A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| ПАРАЛЛЕЛЬНАЯ СИСТЕМА ИНФОРМАЦИОННОГО ПОИСКА | 2001 |

|

RU2195015C1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

Изобретение относится к измерительной технике, предназначено для определения длительностей временных интервалов, разграниченных импульсами импульсной последовательностей может быть использовано в устройствах определения скорости, например скорости вращения вала двигателя.

Цель - повышение надежности.

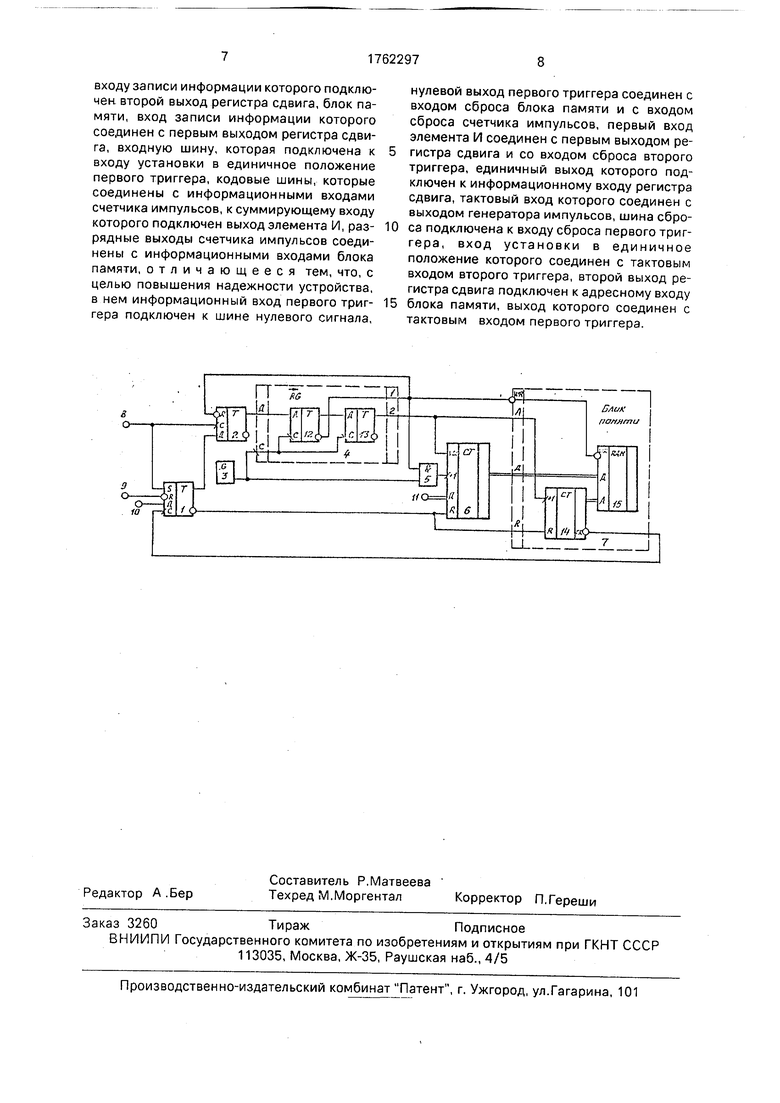

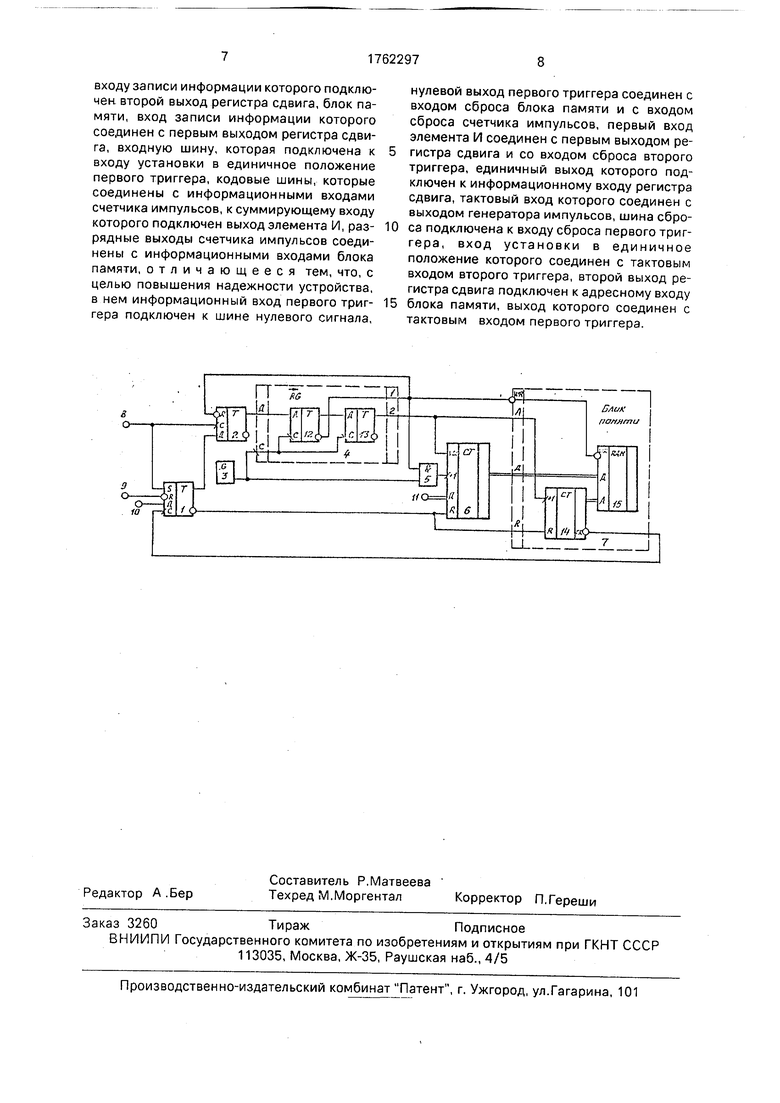

На чертеже представлена функциональная схема устройства для преобразования временных интервалов в код.

Устройство для преобразования временных интервалов в код содержит первый триггер 1, второй триггер 2, генератор импульсов 3, регистр сдвига 4 к информационному входу которого подключен единичный выход триггера 2, элемент И 5, второй вход которого соединен с выходом генератора импульсов 3 и с тактовым входом регистра сдвига 4, счетчик импульсов 6, к суммирующему входу которого подключен выход элемента И 5, блок памяти 7, вход записи информации которого соединен с первым входом элемента И 5, с первым выходом регистра сдвига 4 и с входом сброса триггера 2, к информационному входу которого подключен единичный выход триггера 1, нулевой выход которого соединен с входом сброса блока памяти 7 и входом сброса счетчика импульсов 6, разрядные выходы которого подключены к информационным входам блока памяти 7, выход которого соединен с тактовым входом триггера 1, входную шину 8, которая подключена к тактовому входу триггера 2 и к входу установки в единичное положение триггера 1 шину сброса 9 которая соединена с входом сброса триггера 1, шину нулевого сигнала 10, которая подключена к информационному входу триггера 1, кодовые шины 11, кото- рые соединены с информационными входами счетчика импульсов 6, вход записи информации которого соединен со вторым

со

с

XI О

NJ

to

Ю XI

выходом регистра сдвига 4 и с адресным входом блока памяти 7,

Регистр сдвига 4 содержит триггер 12, информационный вход которого соединен с информационным входом регистра 4, к первому выходу которого подключен нулевой выход триггера 12, триггер 13, тактовый вход которого соединен с тактовым входом триггера 12 и с тактовым входом регистра 4, ко второму выходу которого подключен единичный выход триггера 13, информационный вход которого соединен с единичным выходом триггера 12.

Блок памяти 7 содержит адресный счетчик 14, суммирующий вход которого соединен с адресным входом блока 7, вход сброса которого подключен к входу сброса счетчика импульсов 14, выход переполнения которого соединен с выходом блока памяти 7, оперативно запоминающее устройство 15, вход записи информации которого соединен с входом записи информации блока 7, информационные входы которого подключены к входам данных оперативного запоминающего устройства 15, адресные входы которого соединены с разрядными выходами счетчика 14.

Триггеры 1 и 2 по переднему фронту (перепаду 0-1) импульсов, а триггеры 12 и 13 по заднему фронту (перепаду 1-0) импульсов, поступающих на их тактовые входы, устанавливаются в положение, соответствующее сигналу на их информационных входах. Триггер 1 по входу установки в единичное положение работает от единичных импульсов - импульсов единичного уровня. Триггеры 1 и 2 по входу сброса работают от нулевых импульсов - импульсов нулевого уровня.

Входы сброса и установки в единичное положение триггеров 1 и 3 имеют приоритет перед их тактовыми входами.

Счетчик импульсов 6 по суммирующему входу работает от передних фронтов импульсов, поступающих на этот вход, счетчик импульсов 14 работает также от передних фронтов импульсов, поступающих на этот вход. При поступлении на вход записи информации счетчика импульсов 6 единичного импульса - импульса единичного уровня в счетчик импульсов 6 записывается код, находящийся на его информационных входах. Установка счетчиков импульсов 6 и 14 в нулевое положение производится подачей единичного импульса на вход сброса. Вход записи информации счетчика 6 имеет приоритет перед суммирующим входом, входы сброса счетчиков 6 и 14 имеют приоритет перед всеми другими входами. На выходе переполнения счетчика импульсов 14 появляется нулевой сигнал при содержимом счетчика, равном 11...1, и при отсутствии импульса на суммирующем входе счетчика 14.

В состав оперативного запоминающего устройства 15 могут входить не показанные на чертеже повторители с открытым коллектором и повторители с третьим состоянием в зависимости от типа микросхемы,

0 выбранной для реализации оперативного запоминающего устройства. Запись информации производится подачей нулевого импульса на вход записи информации блока памяти 7 и, соответственно, на вход записи

5 информации оперативного запоминающего устройства 15. В качестве входа записи информации оперативного запоминающего устройства 15 может использоваться либо вход Чтение - запись, либо вход Выбор0 ка микросхемы оперативного запоминающего устройства в зависимости от ее типа (при этом на другие входы подаются сигналы, обеспечивающие совместно с сигналом на входе записи информации режим записи

5 в оперативное запоминающее устройство информации, находящейся на входах данных, по адресу, код которого задается счетчиком 14).

На шину сброса 9 подаются нулевые

0 импульсы. На входную шину 8 подаются единичные импульсы.

На шины 11 подается постоянно кол числа 2.

Устройство для преобразования вре5 менных интервалов работает следующим образом,

В исходном состоянии триггеры 1, 2, регистр сдвига 4, счетчик импульсов 6 и адресный счетчик 14 блока памяти 7 находятся

0 в нулевом положении, на втором выходе регистра сдвига 4 находится нулевой сигнал, на первом выходе регистра сдвига 4 находится единичный сигнал, через элемент И 5 импульсы генератора 3 поступают на сумми5 рующий вход счетчика 6, но он остается в нулевом положении, т.к. на его входе сброса имеется единичный сигнал с нулевого выхода триггера 1. При включении питания регистр 4, в зависимости от того, в какое

0 положение установлены триггер 2 и триггеры 12 и 13 может выдать на свои выходы импульсы, которые не влияют на работу устройства. Установка устройства в исходное положение после включения питания про5 изводится подачей импульса на шину 9.

При поступлении на шину 8 первого им пульса в единичное положение устанавливается только триггер 1, триггер 2 остается в нулевом положении, т.к. на его информационном входе единичный сигнал появляется через время переброса триггера 1 в единичное положение после поступления переднего фронта импульса на тактовый вход триггера 2. После переброса триггера 1 в единичное положение единичный сигнал с его единичного выхода поступает на информационный вход триггера 2, подготавливая последний к перебросу в единичное положение при поступлении на шину 8 следующих импульсов. Нулевой сигнал с нулевого выхода триггера 1 разрешает работу счетчика импульсов 6 и адресного счетчика 14 блока памяти 7 по суммирующим входам. Счетчик импульсов 6 начинает определять количество импульсов генератора 3, поступивших на его суммирующий вход через элемент И 5. Идет определение длительности временного интервала. При поступлении второго импульса на шину 8 триггер 2 устанавливается в единичное положение по переднему фронту этого импульса.

По заднему фронту первого, после установки триггера 2 в единичное положение, импульса генератора 3 устанавливается в единичное положение триггер 12 регистра 4, на первом выходе регистра 4 появляется нулевой сигнал, закрывающий элемент И 5, устанавливающий в нулевое положение триггер 2 и записывающий в блок памяти 7 - в нулевую ячейку оперативного запоминающего устройства 15 содержимое счетчика импульсов 6 - код окончившегося временного интервала (в данном случае - первого). Второй, после поступления импульса на шину 8 и установки триггера 2 в единичное положение, импульс генератора 3 через элемент И 5 не проходит, а по заднему фронту этого импульса триггер 13 регистра 4 устанавливается в единичное положение, а триггер 12 - в нулевое положение. На первом и на втором выходах регистра 4 появляются единичные сигналы. Единичный сигнал со второго выхода регистра 4 записывает в счетчик импульсов 6 код, находящийся на шинах 11 - код числа 2, а также поступает на суммирующий вход адресного счетчика 14 блока памяти 7, который фиксирует сигнал по его переднему фронту, подготавливая адрес следующей (в данном случае, первой) ячейки оперативного запоминающего устройства 15, в которую будет заноситься код следующего временного интервала. Единичный сигнал с первого выхода регистра 4 открывает элемент И 5.

Третий, после поступления импульса на шину 8 и установки триггера 2 в единичное положение, импульс генератора 3 проходит на суммирующий вход счетчика импульсов 6, но в последнем остается записанным код числа 2, т.к. как указывалось выше, вход

записи информации счетчика 6 имеет приоритет перед суммирующим входом. По заднему фронту третьего, после поступления импульса на шину 8 и установки триггера 2

в единичное положение, импульса генератора 3 триггер 13 регистра 4 устанавливается в нулевое положение и на втором выходе регистра 4 появляется нулевой сигнал, разрешающий работу счетчика импульсов б по

0 суммирующему входу. Последующие импульсы генератора 3 поступают через элемент И 5 на суммирующий вход счетчика 6 и формируют в нем код второго временного интервала. При поступлении на шину 8

5 третьего и последующих импульсов устройство работает аналогично тому, как оно работает при поступлении на шину 8 второго импульса. После окончания (2п-1)-ого импульса (где п - разрядность счетчика 14 бло0 ка памяти 7), поступившего на адресный вход блока памяти 7 (т.е. импульса, выданного на второй выход регистра 4, после поступления на шину 8 - 2п-ого импульса), на выходе переполнения счетчика импульсов

5 14 блока памяти 7 появляется нулевой сигнал. При поступлении 2п-ого импульса на адресный вход блока памяти 7 счетчик 14 блока памяти 7 устанавливается в нулевое положение, на его выходе переполнения по0 является единичный сигнал, по перепаду 0- 1 которого на тактовом входе триггера 1 . последний устанавливается в нулевое положение и устанавливает все устройство в исходное состояние. Коды временных

5 интервалов находятся в оперативном запоминающем устройстве 15 блока памяти 7 и могут быть считаны (сигналом, разрешающим считывание, может служить, например, единичный сигнал с нулевого выхода тригге0 ра 1 - на чертеже эта цепь не показана).

Если необходимо прекратить работу устройства до переполнения счетчика 14 блока памяти 7, то на шину 9 подается импульс, устанавливающий триггер 1 в нулевое поло5 жение. Единичный сигнал с нулевого выхода триггера 1 устанавливает устройство в исходное состояние. Коды длительностей окончившихся до подачи импульса на шину 9 временных интервалов хранятся в опера0 тивном запоминающем устройстве 15 блока памяти 7.

Формула изобретения Устройство для преобразования временных интервалов в код, содержащее

5 первый триггер, второй триггер, к информационному входу которого подключен единичный выход первого триггера, генератор импульсов, регистр сдвига, элемент И. второй вход которого соединен с выходом генератора импульсов, счетчик импульсов, к

входу записи информации которого подключен второй выход регистра сдвига, блок памяти, вход записи информации которого соединен с первым выходом регистра сдвига, входную шину, которая подключена к входу установки в единичное положение первого триггера, кодовые шины, которые соединены с информационными входами счетчика импульсов, к суммирующему входу которого подключен выход элемента И, разрядные выходы счетчика импульсов соединены с информационными входами блока памяти, отличающееся тем, что, с целью повышения надежности устройства, в нем информационный вход первого триггера подключен к шине нулевого сигнала,

Ј

3 ЧЛгН

Оол

FS

нулевой выход первого триггера соединен с входом сброса блока памяти и с входом сброса счетчика импульсов, первый вход элемента И соединен с первым выходом регистра сдвига и со входом сброса второго триггера, единичный выход которого подключен к информационному входу регистра сдвига, тактовый вход которого соединен с выходом генератора импульсов, шина сброса подключена к входу сброса первого триггера, вход установки в единичное положение которого соединен с тактовым входом второго триггера, второй выход регистра сдвига подключен к адресному входу

блока памяти, выход которого соединен с тактовым входом первого триггера.

Блик понята

1

сг

К

Авторы

Даты

1992-09-15—Публикация

1990-12-10—Подача