Изобретение относится к импульсной технике и может быть использовано в качестве источника последовательностей различньк типов испытательных кодов Б аппаратуре контроля и диагностики цифровых блоков.

Цель изобретения - расширение функциональных возможностей генератора испытательных кодов за счет одновременного управления частотой появления единичного сигнала, частотой переключения сигналов на выходах генератора и величиной периода последовательности выходных сигналов генератора.

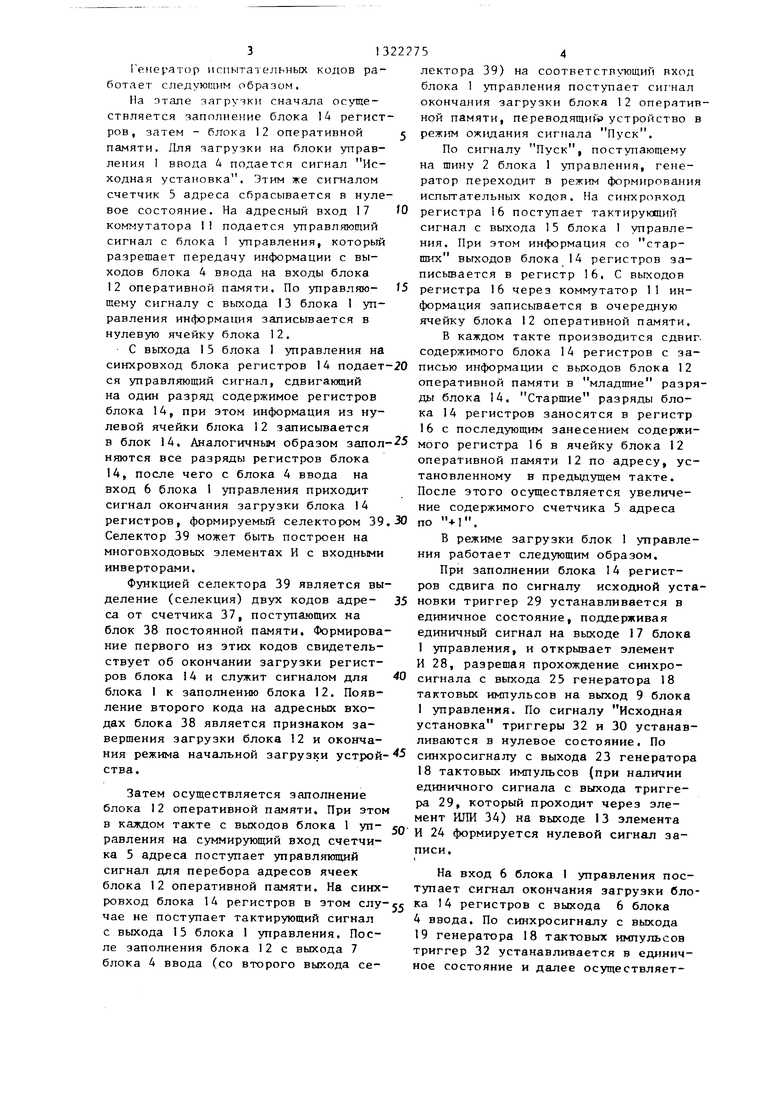

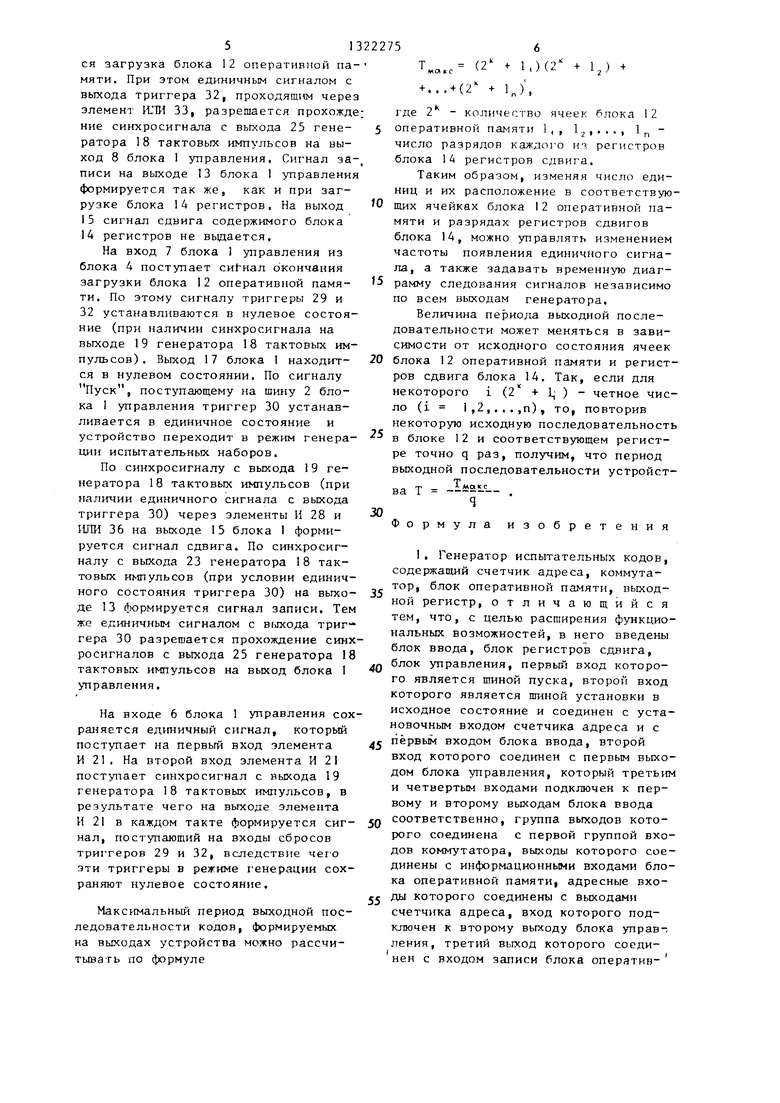

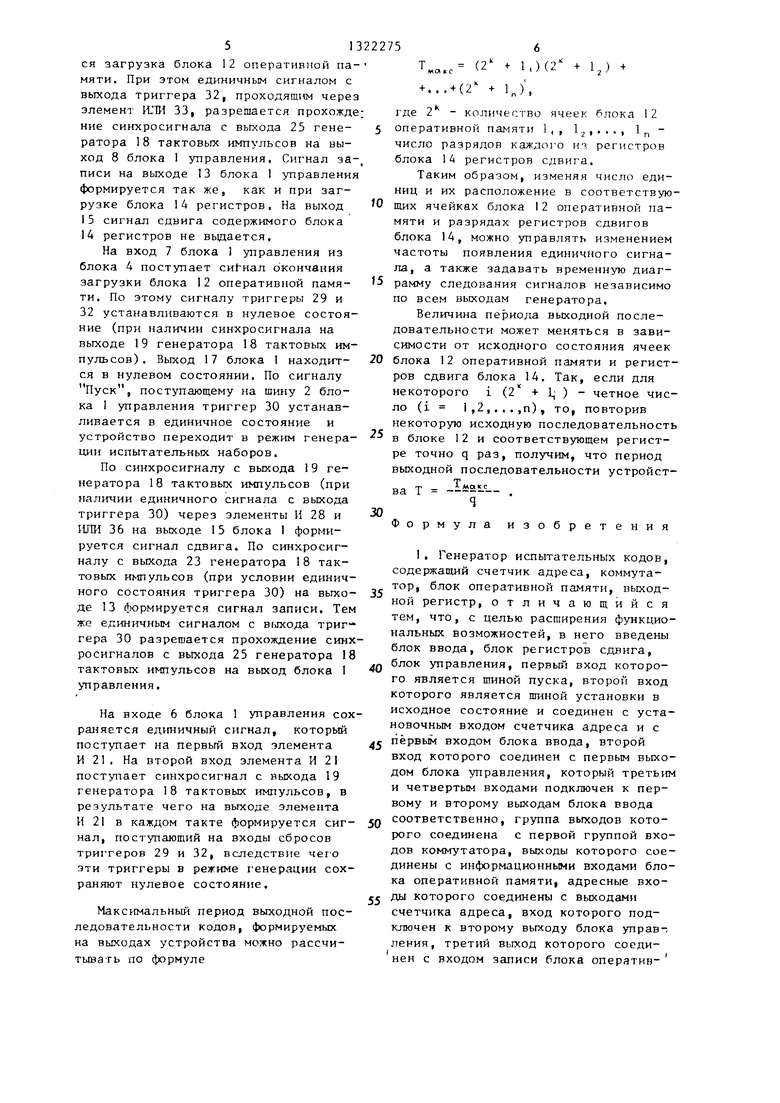

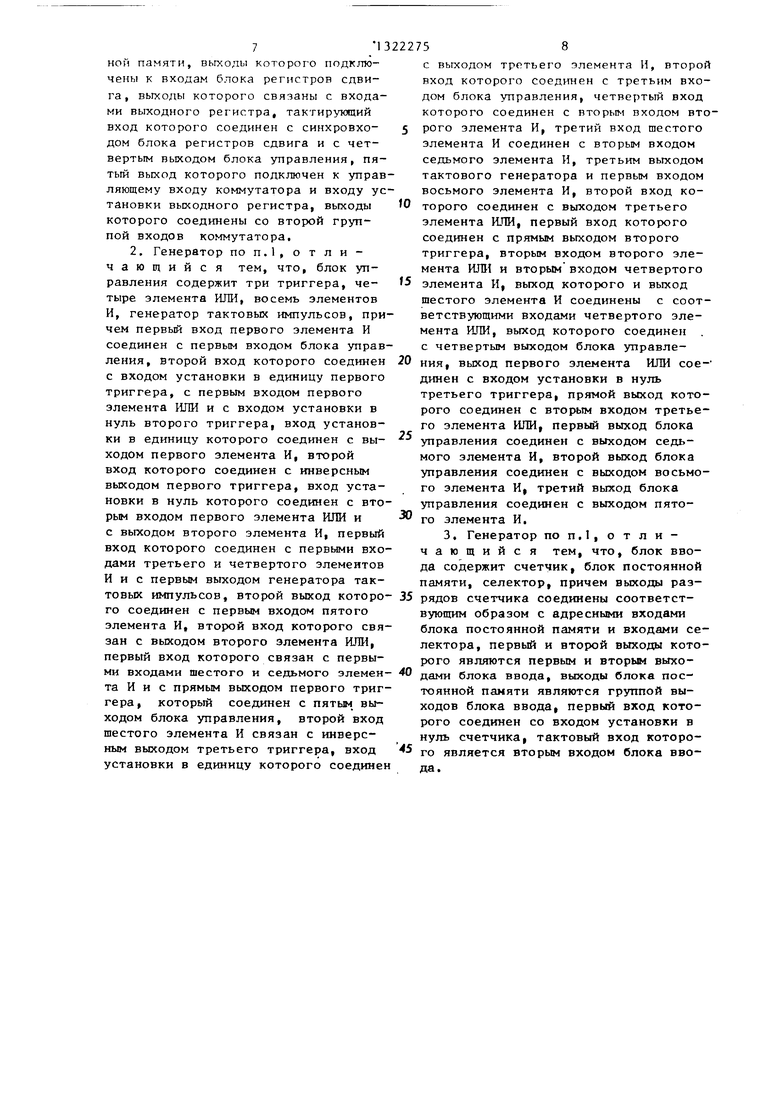

На фиг.1 представлена функциональная схема генератора испытательных кодов; на фиг, 2 - функциональная схема блока управления; на фиг. 3 - ф нкциональная схема блока ввода,

Устройство содержит блок I управления, входами которого являются шина 2 пуска и шина 3 установки в исходное состояние, который подключен к блоку и ввода и входу сброса счетчика 5 адреса. Выходы 6 и 7 блока

4ввода подключены к соответствующим входам блока 1 управления, выход 8 которого связан с суммирующим входом счетчика 5 адреса. Выход 9 блока управления 1 соединен с блоком 4, группа выходов 10 которого связана с первой группой входов коммутатора

1I, выходы которого соединены с информационными входами, блока I 2 оперативной памяти, адресные входы которого подключены к выходам счетчика

5адреса, I

Выход 13 блока 1 управления соединен с управляющим входом блока 12 оперативной памяти, выходы которого связаны с информационными входами блока 14 регистров сдвига, синхро- вход которого связан с выходом 15 блока 1 управления, подключенным также к синхровходу выходного регистра 16. Выходы блока 14 регистров сдвига соединены с информационными входами выходного регистра 16, выходы которого подключены к второй группе входов коммутатора I, управляющий вход которого связан с выходом 17 блока 1 управления и с установочным входом выходного регистра 16. Выходы регистра 16 являются выходами генератора.

Блок 1 управления содержит генератор 18 тактовых -импульсов, выход

O

5

0

5

0

5

0

5

0

5

19 которого соединен с входами элементов И 20-22. Выход 23 генератора 18 тактовых импульсов соединен с входом элемента И 24, выход 13 которого является вькодом блока I управления 1. Выход 25 генератора 18 тактовых импульсов соединен с входами элементов И 26 - 28. Вход установки в 1 триггера 29 соединен с входом установки в о триггера 30, с входом элемента ИЛИ 31 и с шиной 3 установки в исходное состояние блока 1 управления.

Вход установки в О триггера 29 подключен к выходу элемента И 21 и соединен с вторым входом элемента ИЛИ 31, выход которого связан с входом установки в О триггера 32, прямой выход которого соединен с входом элемента ИЛИ 33, выход которого соединен с вторым входом элемента И 26. Прямой выход триггера 29 соединен со вторыми входами элементов И 28 и 27, с входом элемента ИЛИ 34 и с выходом 17 блока 1 управления.

Инверсный выход триггера 29 соединен с входом элемента И 35, выход которого подключен к входу установки в 1 триггера 30, прямой выход которого соединен с вторыми входами элементов И 22, ИЛИ 33 и 34, выход последнего заведен на второй вход элемента И 24, Инверсный выход триггера 32 подключен к третьему входу элемента И 27, выход которого связан с входом элемента ИЛИ 36, выход которого соединен с выходом 15 блока 1 управления.

Второй вход элемента ИЛИ 36 связан с выходом элемента И 22. Вход 6 блока 1 управления заведен на второй вход элемента И 20, выход которого соединен с входом установки в 1 триггера 32. Входы 2 и 6 блока 1 управления подключены к вторым входам элементов И 35 и 21 соответственно.

Блок 4 ввода содержит счетчик 37, выходы которого соединены с входами блока 38 постоянной памяти и подключены к входам селектора 39, первый выход последнего соединен с выходом 6 блбка 4 ввода, второй выход селектора 39 является выходом 7 блока 4 ввода. Вход 3 блока 4 ввода связан со входом сброса счетчика 37, а вход 9 блока 4 соединен с суммирующим входом счетчика 37. Выходы блока 38 являются группой выходов 10 блока 4.

Iенератор испытй ельньк кодов работает следующим образом,

На этапе загрузки сначала осуществляется заполнение блока 14 регистров, затем - блока 12 оперативной памяти. Для загрузки на блоки управления 1 ввода 4 подается сигнал Исходная установка. Этим же сигналом счетчик 5 адреса сбрасывается в нулевое состояние. На адресный вход 17 О коммутатора I1 подается управляющий сигнал с блока 1 управления, который разрешает передачу информации с выходов блока 4 ввода на входы блока 12 оперативной памяти. По управляю- J5 щему сигналу с вьгхода 13 блока 1 управления информация записывается в нулевую ячейку блока 12,

С выхода 15 блока 1 управления на

лектора 39) на соответстпующий вход блока 1 управления поступает сиг нал окончания загрузки блока 12 оперативной памяти, переводящий устройство в 5 режим ожидания сигнала Пуск.

По сигналу Пуск, поступающему на шину 2 блока 1 управления, генератор переходит в режим формирования испытательных кодов. На синхровход регистра 16 поступает тактирующий сигнал с выхода 15 блока 1 управления. При этом информация со старших выходов блока 14 регистров за- письшается в регистр 16, С выходов регистра 16 через коммутатор 11 информация записывается в очередную ячейку блока 12 оперативной памяти. В каждом такте производится сдвиг.

содержимого блока 14 регистров с за- синхровход блока регистров 14 подает-20 писью информации с вькодов блока 12 ся управляющий сигнал, сдвигающий оперативной памяти в младшие разря- на один разряд содержимое регистров ды блока 14, Старшие разряды бло- блока 14, при этом информация из ну- ка 14 регистров заносятся в регистр левой ячейки блока 12 записывается 16 с последующим занесением содержи- в блок 14, Аналогичным образом запол- мого регистра 16 в ячейку блока 12 няются все разряды регистров блока оперативной памяти 12 по адресу, ус- 14, после чего с блока 4 ввода на тановленному в предыдущем такте, вход 6 блока 1 управления приходит После этого осуществляется увеличе- сигнал окончания загрузки блока 14 ние содержимого счетчика 5 адреса регистров, формируемый селектором 39.-30 по -t-l.

Селектор 39 может быть построен на многовходовых элементах И с входными инверторами.

Функцией селектора 39 является выделение (селекция) двух кодов адреса от счетчика 37, поступающих на блок 38 постоянной памяти. Формирование первого из этих кодов свидетельствует об окончании загрузки регистров блока I4 и служит сигналом для блока 1 к заполнению блока 12. Появление второго кода на адресных входах блока 38 является признаком завершения загрузки блока 12 и окончаВ режиме загрузки блок 1 управления работает следующим образом.

При заполнении блока 14 регистров сдвига по сигналу исходной уста35 новки триггер 29 устанавливается в единичное состояние, поддерживая единичньш сигнал на выходе 17 блока 1 управления, и открьгоает элемент И 28, разрешая прохождение синхро40 сигнала с выхода 25 генератора 18 тактовых импульсов на выход 9 блока 1 управления. По сигналу Исходная установка триггеры 32 и 30 устанавливаются в нулевое состояние. По

ния режима начальной загрузки устрой- - синхросигналу с выхода 23 генератора ства,18 тактовых импульсов (при наличии

единичного сигнала с выхода триггера 29, который проходит через элемент ИЛИ 34) на выходе 13 элемента

Затем осуществляется заполнение блока 12 оперативной памяти. При этом

в каждом такте с выходов блока 1 уп- сп. ,, V -

- И 24 формируется нулевой сигнал за- равления на суммирующий вход счетчика 5 адреса поступает управляющий сигнал для перебора адресов ячеек блока 12 оперативной памяти. На синхровход блока 14 регистров в этом слу-с ка 14 регистров с выхода 6 блока чае не поступает тактирующий сигнал 4 ввода. По синхросигналу с выхода с выхода 15 блока I управления. После заполнения блока 12 с выхода 7 блока 4 ввода (со второго выхода сепией.

На вход 6 блока I управления поступает сигнал окончания загрузки бло19 генератора 18 тактовых иьшульсов триггер 32 устанавливается в единичное состояние и далее осуществляет ОJ5 27754

лектора 39) на соответстпующий вход блока 1 управления поступает сиг нал окончания загрузки блока 12 оперативной памяти, переводящий устройство в 5 режим ожидания сигнала Пуск.

По сигналу Пуск, поступающему на шину 2 блока 1 управления, генератор переходит в режим формирования испытательных кодов. На синхровход регистра 16 поступает тактирующий сигнал с выхода 15 блока 1 управления. При этом информация со старших выходов блока 14 регистров за- письшается в регистр 16, С выходов регистра 16 через коммутатор 11 информация записывается в очередную ячейку блока 12 оперативной памяти. В каждом такте производится сдвиг.

В режиме загрузки блок 1 управления работает следующим образом.

При заполнении блока 14 регистров сдвига по сигналу исходной установки триггер 29 устанавливается в единичное состояние, поддерживая единичньш сигнал на выходе 17 блока 1 управления, и открьгоает элемент И 28, разрешая прохождение синхросигнала с выхода 25 генератора 18 тактовых импульсов на выход 9 блока 1 управления. По сигналу Исходная установка триггеры 32 и 30 устанавливаются в нулевое состояние. По

И 24 формируется нулевой сигнал за- ка 14 регистров с выхода 6 блока 4 ввода. По синхросигналу с выхода

пией.

На вход 6 блока I управления поступает сигнал окончания загрузки блоИ 24 формируется нулевой сигнал за- ка 14 регистров с выхода 6 блока 4 ввода. По синхросигналу с выхода

19 генератора 18 тактовых иьшульсов триггер 32 устанавливается в единичное состояние и далее осуществляет51

ся загрузка блока 12 оперативной памяти. При этом единичным сигналом с выхода триггера 32, проходящим через элемент ПТИ 33, разрешается прохожде ние синхросигнала с выхода 25 гене- ратора 18 тактовых импульсов на выход 8 блока 1 управления, Сигнал записи на выходе 13 блока 1 управления формируется так же, как и при загрузке блока 14 регистров. На выход 15 сигнал сдвига содержимого блока 14 регистров не выдается,

На вход 7 блока 1 управления из блока 4 поступает окончания загрузки блока 12 оперативной памя- ти. По этому сигналу триггеры 29 и 32 устанавливаются в нулевое состояние (при наличии синхросигнала на выходе 19 генератора 18 тактовых импульсов). Выход 17 блока I находится в нулевом состоянии. По сигналу Пуск, поступающему на шину 2 блока 1 управления триггер 30 устанавливается в единичное состояние и устройство переходит в режим генерации испытательных наборов.

По синхросигналу с выхода 19 генератора 18 тактовых импульсов (при наличии единичного сигнала с выхода триггера 30) через элементы И 28 и ЯПИ 36 на вьсходе 15 блока I формируется сигнал сдвига. По синхросигналу с выхода 23 генератора 18 так

1. Генератор испытательных кодов, содержащий счетчик адреса, коммутатовых импульсов (при условии единич-

т„ тор, блок оперативной памяти, выходного состояния триггера 30) на выхо- 35 ,„-, , „ . „ - - .

де 13 формируется сигнал записи. Тем же единичным сигналом с вг 1хода триггера 30 разрешается прохождение синхросигналов с выхода 25 генератора 18

НОИ регистр, отличающийся тем, что, с целью расщирения функциональных возможностей, в него введены блок ввода, блок регистров сдвига, блок управления, первый вход которого является щиной пуска, второй вход которого является щиной установки в исходное состояние и соединен с установочным входом счетчика адреса и с JC пёрвьм входом блока ввода, второй

тактовых импульсов на выход блока I управления.

На входе 6 блока 1 управления сохраняется единичный сигнал, который поступает на первый вход элемента И 21. На второй вход элемента И 21 поступает синхросигнал с выхода 19 генератора 18 тактовых импульсов, в результате чего на выходе элемента И 21 в каждом такте формируется сигнал, поступающий на входы сбросов триггеров 29 и 32, вследствие чего эти триггеры в режиме генерации сохраняют нулевое состояние.

Максимальный период выходной последовательности кодов, формируемых на выходах устройства можно рассчитывать по формуле

-5

Т (2

мсткс

1.)

0

5

6

1,)(2

+ ...М2 Ij ,

где 2 - количество ячеек блока оперативной памяти 1,, l,..., число разрядов каждо1 о нп регистров блока 14 регистров сдвига.

Таким образом, изменяя число единиц и их расположение в соответствующих ячейках блока I2 оперативной памяти и разрядах регистров сдвигов блока 14, можно управлять изменением частоты появления единичного сигнала, а также задавать временную диаграмму следования сигналов независимо по всем выходам генератора.

Величина перпоца выходной последовательности может меняться в зависимости от исходного состояния ячеек блока 12 оперативной памяти и регистров сдвига блока 14. Так, если для некоторого i (2 + 1; ) четное число (i 1,2,...,п), то, повторив некоторую исходную последовательность в блоке 12 и соответствующем регистре точно q раз, получим, что период выходной последовательности устройства Т . ,

q

Формула изобретения

1. Генератор испытательных кодов, содержащий счетчик адреса, коммута

тор, блок оперативной памяти, выход,„-, , „ . „ - - .

НОИ регистр, отличающийся тем, что, с целью расщирения функциональных возможностей, в него введены блок ввода, блок регистров сдвига, блок управления, первый вход которого является щиной пуска, второй вход которого является щиной установки в исходное состояние и соединен с установочным входом счетчика адреса и с пёрвьм входом блока ввода, второй

вход которого соединен с первым выходом блока управления, который третьим и четвертым входами подключен к первому и второму выходам блока ввода соответственно, группа выходов которого соединена с первой группой входов коммутатора, выходы которого соединены с информационными входами блока оперативной памяти, адресные входы которого соединены с выходами счетчика адреса, вход которого подключен к второму выходу блока управ-, ления, третий выход которого соединен с входом записи блока оператив-

ной памяти, выходы которого подключены к входам блока регистров сдвига, выходы которого связаны с входами выходного регистра, тактирующий вход которого соединен с синхровхо- дом блока регистров сдвига и с четвертым выходом блока управления, пятый выход которого подключен к управляющему входу коммутатора и входу установки выходного регистра, выходы которого соединены со второй группой входов коммутатора,

2. Генератор по п.1, о т л и - чающийся тем, что, блок управления содержит три триггера, четыре элемента ИЛИ, восемь элементов И, генератор тактовых импульсов, причем первый вход первого элемента И соединен с первым входом блока управления, второй вход которого соединен с входом установки в единицу первого триггера, с первым входом первого элемента ИЛИ и с входом установки в нуль второго триггера, вход установки в единицу которого соединен с выходом первого элемента И, второй вход которого соединен с инверсным выходом первого триггера, вход установки в нуль которого соединен с вторым входом первого элемента ИЛИ и с выходом второго элемента И, первый вход которого соединен с первыми входами третьего и четвертого элементов И и с первым выходом генератора тактовьк импульсов, второй выход которо- 35 рядов счетчика соединены соответст- го соединен с первым входом пятого вующим образом с адресными входами элемента И, второй вход которюго связан с выходом второго элемента ИЛИ,

первый вход которого связан с первыблока постоянной памяти и входами селектора, первый и второй выходы которого являются первым и вторьи выхо- ми входами шестого и седьмого элемен- 40 дами блока ввода, выходы блока поста И и с прямым выходом первого триг- тоянной памяти являются группой вы- который

гера, который соединен с пятым выходом блока управления, второй вход шестого элемента И связан с инверсным выходом третьего триггера, вход установки в единицу которого соединен

ходов блока ввода, первый вход которого соединен со входом установки в нуль счетчика, тактовый вход которо- го является вторым входом блока ввода.

с выходом третьего элемента И, второй вход которого соединен с третьим входом блока управления, четвертый вход которого соединен с вторым входом второго элемента И, третий вход шестого элемента И соединен с вторьм входом седьмого элемента И, третьим выходом тактового генератора и первым входом восьмого элемента И, второй вход которого соединен с выходом третьего элемента ИЛИ, первый вход которого соединен с прямым выходом второго триггера, вторым входом второго элемента ИЛИ и вторым входом четвертого

5 элемента И, выход которого и выход шестого элемента И соединены с соответствующими входами четвертого элемента ИЛИ, выход которого соединен с четвертым выходом блока управле0 ния, выход первого элемента ИЛИ соединен с входом установки в нуль третьего триггера, прямой выход которого соединен с вторым входом третьего элемента ИЛИ, первый выход блока управления соединен с выходом седьмого элемента И, второй выход блока управления соединен с выходом восьмого элемента И, третий выход блока управления соединен с выходом пятого элемента И.

3. Генератор по п.1, о т л и - чающийся тем, что, блок ввода содержит счетчик, блок постоянной памяти, селектор, причем выходы раз-

5

блока постоянной памяти и входами селектора, первый и второй выходы которого являются первым и вторьи выхо- 40 дами блока ввода, выходы блока пос тоянной памяти являются группой вы-

ходов блока ввода, первый вход которого соединен со входом установки в нуль счетчика, тактовый вход которо- го является вторым входом блока ввода.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор испытательных кодов | 1986 |

|

SU1405058A1 |

| Устройство управления загрузкой микропрограмм | 1983 |

|

SU1136175A2 |

| Устройство управления загрузкой микропрограмм | 1983 |

|

SU1119019A1 |

| Устройство для контроля программ | 1987 |

|

SU1418720A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство контроля электропитания процессора | 1984 |

|

SU1188741A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для управления вводом информации | 1985 |

|

SU1278862A1 |

| Устройство для контроля доменной памяти | 1988 |

|

SU1501160A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

Изобретение может быть использовано в аппаратуре контроля и диагностики цифровых блоков. Цель изобретения - расширение функциональных возможностей генератора. Генератор содержит счетчик 5 адреса, коммутатор 11, блок I2 оперативной памяти и выходной регистр 16. Введение блока 4 ввода, блока 14 регистров сдвига, блока 1 управления и образование новых функциональных связей позволяет одновременно управлять частотой появления единичного сигнала, частотой переключения сигналов на выходах генератора и величиной периода последовательности выходных сигналов генератора. В описании представлены примеры конкретного вьнтолнения блока 1 управления и блока 4 ввода. 2 з.п. ф-лы, 3 ил. с о х э N0 СП

| Генератор псевдослучайных кодов | 1980 |

|

SU920718A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-07—Публикация

1985-11-19—Подача