, ,Т .Ј S 1

1

(21)4905766724

(22|i&;ioo

(46) 30.09.92. БЮЛ. № 36 (72) M. П .Ткаче в и В, Ю. П и ки н (56) Авторское свидетельство СССР № 1287ДбГкл ;с 106 F 11/00,1987. $ А вТ6 рское с ви дете л ьс тво С С С Р Г 1Вз ШГкл; ОВ Р 11/00, 1986. (54)УСТРб ЙСТВО ДЛЯ КОНТРОЖ ММрапроцЕСсоРА-

(57f Изобретение относится к цифровой вы- чШШтёЖной технике и может быть испольa& Vflsf &ftT t rs чл н i J , «Jx,-, К

Г -ft .- 1

1- . -Ь} , я

r«-; r)fr- ,v ,а . а. -, -,,

Изобретение относится к цифровой вы- чиТл й те Ль ной технике и может быть исполь tl s1$r brr f -к«т г - j« ж ц 2f

зёваноприпостроении

мй11 бпр оц ёс сЪ0ных систем и микроЭВМ с конт( v д

Целью изобретения является снижение anFffa p typribix1j§rpavT

Сущность изобретения состоит в сниже- Н5ий а11п а атур н ых 3 aYpaT за счёГисп бльз о- ва й Ш гйнфор ма ции о необходимости формирования в каждом машйн ном цикле

(

также сигналов приема DBIN или в Ш ач й У ГРЛТЁ йн рормацйи (за исключениeamTO Wi Tv DAp);

и й Анализ реж ймов функционирования мг(/Гк рйдацесс6 ра К580ИША1 показал, что каждый машинный цикл каждой из команд мШ: о1ьф о ёс Й|р а исключением команд НШ й рАО / сопровождается выдачей сиг- н лЖ ШлдЙйя 5УМ:СГаГтакже Ь В |№ или WRlTE (4). Следовательно, отсутствие этих

;Шп1йШ1 й№

ф ункциони ЪВани й микроп1роце ссора. 6 ко..-Э Sft& - ;f : fe|jtftSQ i :ftiys

йт/ у fщ ЩЙЙйШШ йййА

,-t ы gx«er% j

- -.-MJ. - -. W -р -, -s-v л ь г v J-T v -зов а н о при построений микропроЦессор- ных сйстём и микроЭВМ с контролем. Целью изобретения является сокращение аппаратурных затрат. Цель достигается путем введения в устройство триггеров, элемента НЕ и элемента ИЛИ. Сущность изобретения состоит в использовании для организации контроля сведений о закономерности поя в л ёййТ кбТнтрбТйруемых управляющих сигналов в машинных циклах микропроцессора, относящихся к разл йч- ным типам. 2 ил.

3: &№.

3 Й а в«51е;1

5: ..T ; -T%ЭЙ5 3&й

;;«Иёнк

мандах T4LT и ОД6 эти сигналы выдаются только в машинном цикле М1, поэтому при

ййгго лШ тх$

ошибки нёобходимб блокировать. Сущность изобретения реализуется путем введения следующё й сбвЬкугТности отличительных признаков (новых элементов и связей), определяющих соответствие заяв- л йёМЬ1г8 ус рб йства критерию новизна.

Введение второго триггера и его свя зёи позволяет управлять работой дешифратора ктШаЩ йом е нт § ьТб6рки кода команд (во время выполнения машинного цикла М1).

В веде н йё трёт ьё го т р и г гё ра и его с зей позволяет фиксировать отсутствие сигналов D6IKT и WRITE в каждом машинном цикле каждой команды микропроцессора .

В ведение четвертого триггера и его связей позволяет бсущё ствлят ь блокиро вку выдачи ей гнала 6 ш и б к и п р и в ы п 6л нении команд HLT или DAD. Вв еденйё пятЬго триггера и его связей позволяет фиксировагь отсутствие

с - ;. , if ., s, -У-П tr «fKiT t« .$ 3 Т€|в«ТЙ ,0t 3/ V ifev;ii #

(Л

С

xi о ел

00 Ю 00

дом машинном цикле сигнала SYNC микропроцессора и формировать сигнал ошибки.

Введение элемента не позволяет получить неинвертированное (единичное) значение управляющего сигнала WRITE микропроцессора,

Введение пятого элемента ИЛИ позволяет формировать сигнал ошибки как при отсутствии сигнала SYNC, так и сигналов DBIN или WRITE в каждом машинном цикле каждой команды микропроцессора (за исключением команд HLT и DAD).

Введение связей, соответствующих второму и четвертому элементам ИЛИ, позволяет осуществлять начальную установку счетчика и четвертого триггера соответственно по сигналу с входа устройства.

Введение связей, соответствующих третьему элементу ИЛИ, позволяет формировать сигнал установки третьего триггера в ноль, запрещая тем самым выдачу сигнала ошибки при выполнении команд HLT и DAD, а также при наличии сигналов DBIN и WRITE.

Введение указанной совокупности признаков обеспечивает достижение цепи изобретения - снижение аппаратурных затрат при контроле управляющих сигналов микропроцессоров.

Предлагаемое техническое решение соответствует критерию существенные отличия, поскольку в известных устройствах 1-3 вследствие отсутствия указанной совокупности конструктивных признаков не достигалось свойство снижения аппаратурных затрат при контроле управляющих сигналов микропроцессора за счет проверки наличия в каждом машинном цикле каждой команды (за исключением команд HLT и DAD) сигналов управления SYNC, DBiNnWRITE.

Положительный эффект, который может быть получен при использовании предлагаемого устройства, состоит в снижении затрат на производство и эксплуатацию за счет уменьшения по сравнению с прототипом сложности устройства контроля при той же совокупности управляющих сигналов, подвергающих контролю.

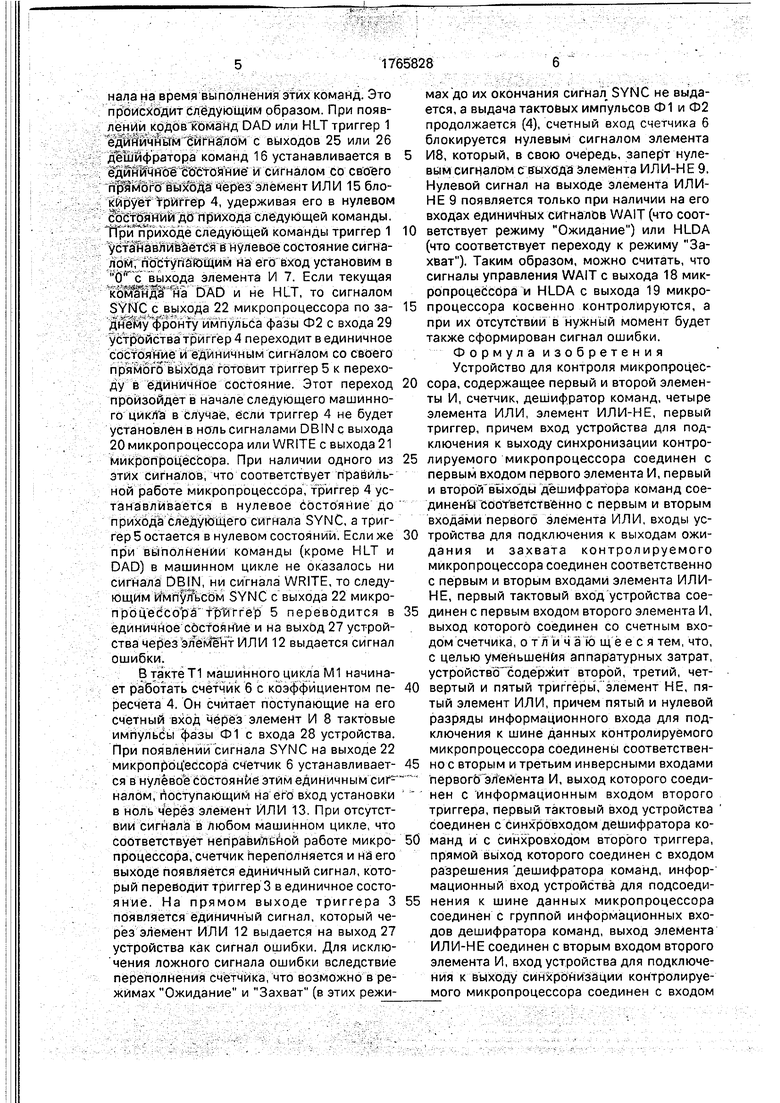

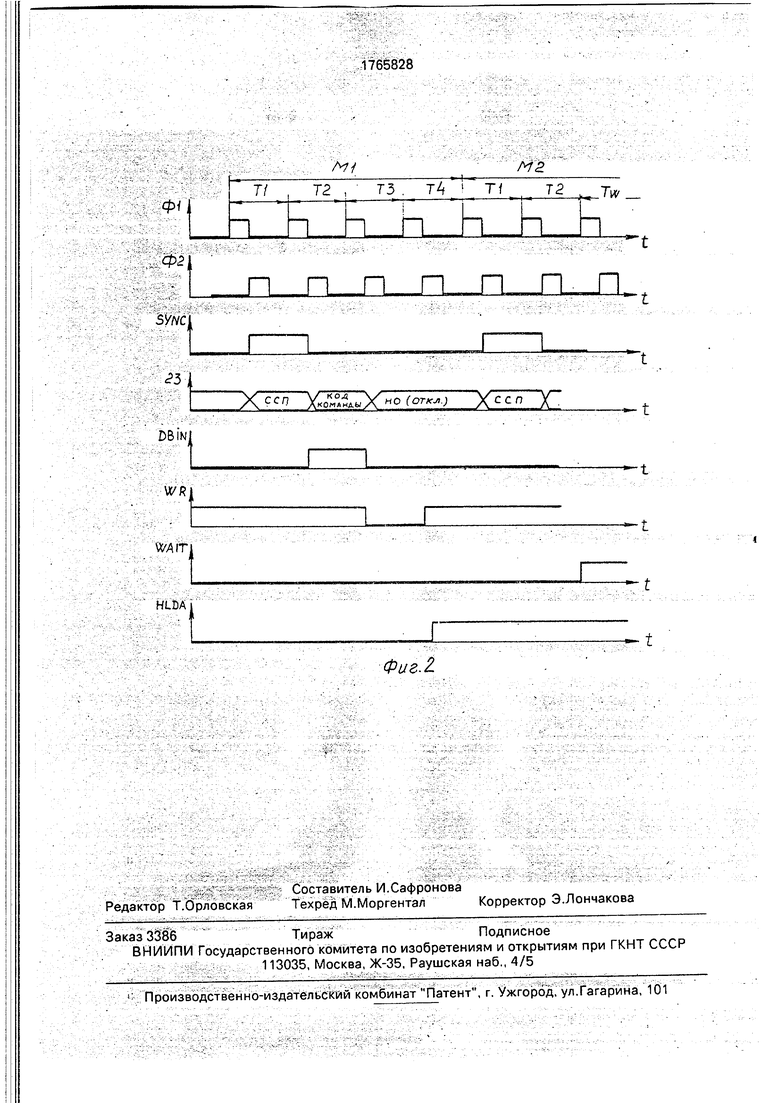

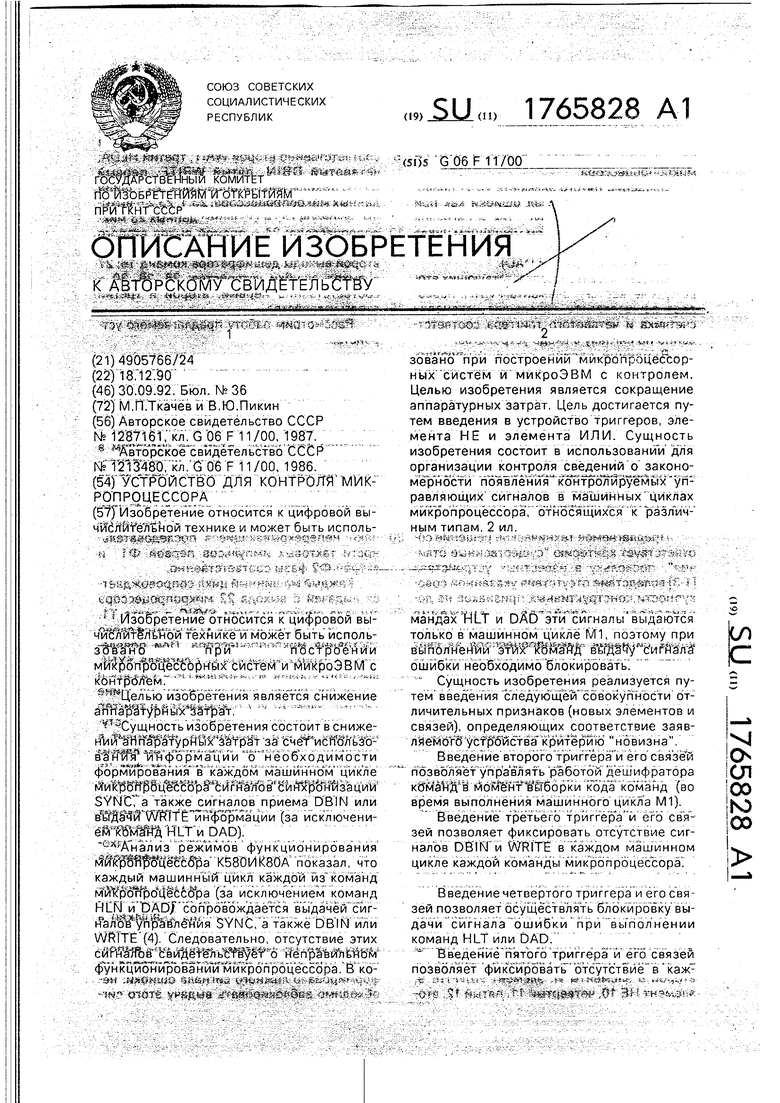

На фиг. 1 представлена функциональная схема устройства для контроля управля- ющихсигналовуправления

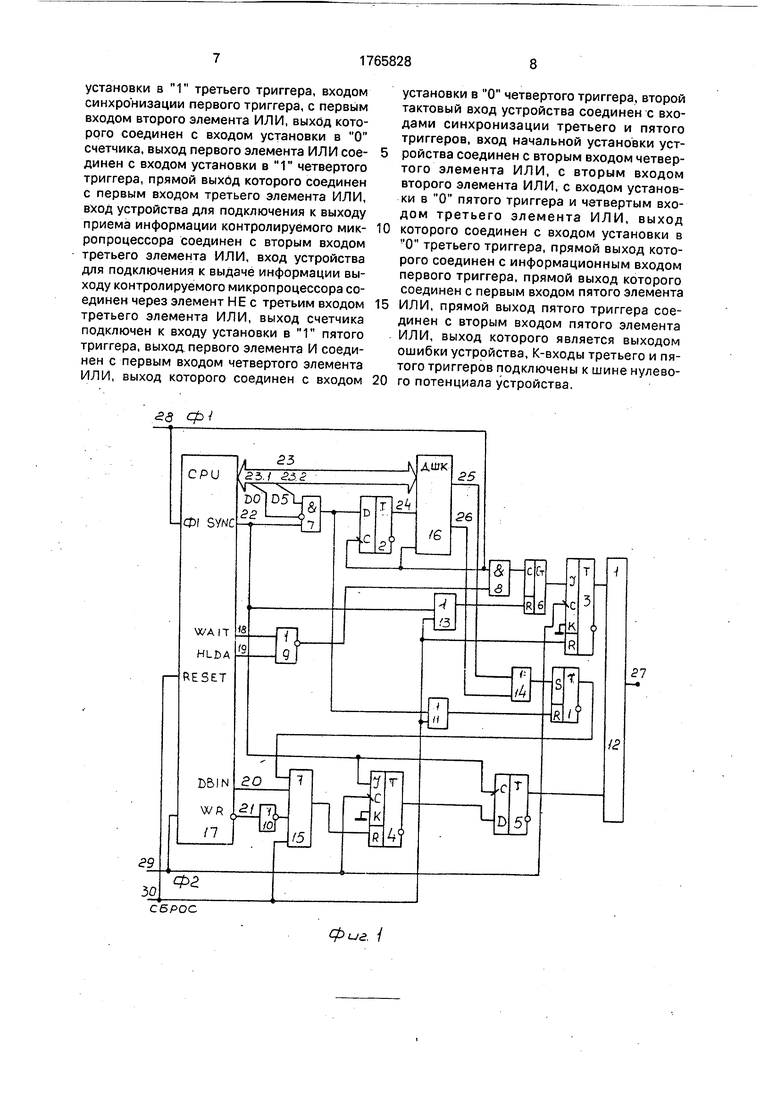

микропроцессора; на фиг. 2 - временные диаграммы работы устройства.

Устройство для контроля управляющих сигналов микропроцессора (фиг. 1) содержит четвертый 1, старой 2, пятый 3, третий 4, первый 4 триггеры, счетчик 6, первый 7 и второй 8 элементы И, элемент ИЛИ-НЕ 9, элемент НЕ 10, четвертый 11, пятый 12, второй 13, первый 14, третий 15 элементы ИЛИ,

дешифратор команд 16. На фиг. 1 обозначен

также контролируемый микропроцессор 17.

На фиг. 1 цифрами 18-22 обозначены

соответственно второй WAIT, третий HLDA, четвертый DBIN, пятый WRITE, первый SYNC выходы микропроцессора, 23 - шина данных микропроцессора, 23.1, 23.2 - выходы разрядов DO и D5 шины данных 23 микропроцессора; 24 - прямой выход второго триггера; 25, 26 - соответственно первый и второй выходы дешифратора команд 16; 27 - выход ошибки устройства; 28, 29, 30 - соответственно первый, второй и третий

входы устройства.

Рассмотрим работу предлагаемого устройства.

Перед началом работы на вход 30 устройства подается сигнал высокого уровня длительности не менее трех периодов тактовой частоты микропроцессора 17, которым микропроцессор устанавливается в исходное состояние. Этим же сигналом в

исходное нулевое состояние устанавливаются триггеры 1,3,4, счетчик 6. После этого в микропроцессоре начинается такт Т1 машинного цикла выборки команды М1 (см. фиг. 2), На входы 28 и 29 устройства поступают неперекрывающиеся последовательности тактовых импульсов первой Ф1 и второй Ф2 фазы соответственно.

Каждый машинный цикл сопровождается выдачей с выхода 22 микропроцессора

сигнала синхронизации SYNC в такте Т1. При этом на шину данных 32 выдается слово состояния микропроцессора. При появлении на входах элемента И 7 сигнала SYNC высокого уровня и разрядов D5 1 и DO О

слова состояния, выставленного на шине данных, элемент И 7 открывается и триггер 2 по заднему фронту импульса Ф1, поступившему на его синхровход, переходит в единичное состояние, разрешая тем самым

дешифратору команд 16 работу (см. фиг. 2). Код команды поступает по шине данных в дешифратор команд, где по синхроимпульсу Ф1 (со входа 28 устройства) происходит дешифрация кода команды и в случае появления кода команды DAD или HLT на выходах соответственно 25 или 26 дешифратора появится единичный сигнал.

Выявление команд HLT и DAD необходимо, так как только при выполнении этих

команд для микропроцессора К580ИК80 в машинных циклах отсутствуют сигналы DBIN и WRITE. Поэтому, чтобы при выполнении этих команд устройство контроля не формировало ложного сигнала ошибки, необходимо заблокировать выдачу этого сигнала на время выполнения этих команд. Это происходит следующим образом. При появлении кодов команд DAD или HLT триггер 1 е дШйчЙеГм бйгналом с выходов 25 или 26 дешифратора команд 16 устанавливается в единичное состояние и сигналом со своего п рШмогсГвыЗйда Через элемент ИЛИ 15 блокирует триггер 4, удерживая его в нулевом сЪстбянии до прихода следующей команды. Т ри приходе следующей команды триггер 1 устанавливается в нулевое состояние сигналом; поступающим на его вход установим в Ог с выхода элемента И 7. Если текущая ко 1а1ЖсГ на DAD и не HLT, то сигналом SYNC с выхода 22 микропроцессора по за- днему Фронту импульса фазы Ф2 с входа 29 устройства триггер 4 переходит в единичное состояние и единичным сигналом со своего прямого выхЪда готовит триггер 5 к переходу в единичное состояние. Этот переход произойдет в начале следующего машинного цикл а в случае, если триггер 4 не будет установлен в ноль сигналами DBIN с выхода 20 микропроцессора или WRITE с выхода 21 микропроцессора. При наличии одного из этих сигналов, что соответствует правильной работе микропроцессора, триггер 4 устанавливается в нулевое состояние до прихода следующего сигнала SYNC, а триггер 5 остается в нулевом состоянии. Если же при выполнении команды (кроме HLT и DAD) в машинном цикле не оказалось ни сигнала DBIN, ни сигнала WRITE, то следующим SYNC с выхода 22 микро- процеСсо ра триггер 5 переводится в единичное состояние и на выход 27 устройства через ИЛИ 12 выдается сигнал ошибки.

Вта ктеТ1 машинного цикла М1 начинает работать счетчик 6 с коэффициентом пе- ресчета 4. Он считает поступающие на его счетный вход через элемент И 8 тактовые импульсы фазы Ф1 с входа 28 устройства. При появлении сигнала SYNC на выходе 22 микропроцессора счетчик 6 устанавливает- ся в нулевое состояние этим единичным сиг налом, поступающим на его вход установки в ноль через элемент ИЛИ 13. При отсутствии сигнала в любом машинном цикле, что соответствует неправильной работе микро- процессора, счетчик переполняется и на его выходе появляется единичный сигнал, который переводит триггер 3 в единичное состо- яние. На прямом выходе триггера 3 появляется единичный сигнал, который через элемент ИЛИ 12 выдается на выход 27 устройства как сигнал ошибки. Для исключения ложного сигнала ошибки вследствие переполнения счетчика, что возможно в режимах Ожидание и Захват (в этих режимах до их окончания сигнал SYNC не выдается, а выдача тактовых импульсов Ф1 и Ф2 продолжается (4), счетный вход счетчика 6 блокируется нулевым сигналом элемента И8, который, в свою очередь, заперт нулевым сигналом с выхода элемента ИЛИ-НЕ 9. Нулевой сигнал на выходе элемента ИЛИ- НЕ 9 появляется только при наличии на его входах единичных сигналив WAIT (что соответствует режиму Ожидание) или HLDA (что соответствует переходу к режиму Захват). Таким образом, можно считать, что сигналы управления WAIT с выхода 18 микропроцессора и HLDA с выхода 19 микропроцессора косвенно контролируются, а при их отсутствии в нужный момент будет также сформирован сигнал ошибки. Формула изобретения Устройство для контроля микропроцессора, содержащее первый и второй элементы И, счетчик, дешифратор команд, четыре элемента ИЛИ, элемент ИЛИ-НЕ, первый триггер, причем вход устройства для подключения к выходу синхронизации контролируемого микропроцессора соединен с первым входом первого элемента И, первый и второй выхо ды дешифратора команд соединены соответственно с первым и вторым входами первого элемента ИЛИ, входы устройства для подключения к выходам ожидания и захвата контролируемого микропроцессора соединен соответственно с первым и вторым входами элемента ИЛИ- НЕ, первый тактовый вход устройства соединен с первым входом второго элемента И, выход которого соединен со счетным входом счетчика, отличающееся тем, что, с целью уменьшения аппаратурных затрат, устройство содержит второй, третий, четвертый и пятый триггеры, элемент НЕ, пятый элемент ИЛИ, причем пятый и нулевой разряды информационного входа для подключения к шине данных контролируемого микропроцессора соединены соответственно с вторым и третьим инверсными входами первого элемента И, выход которого соединен с информационным входом второго триггера, первый тактовый вход устройства соединен с синхровходом дешифратора команд и с синхровходом второго триггера, прямой выход которого соединен с входом разрешения дешифратора команд, информационный вход устройства для подсоединения к шине данных микропроцессора соединен с группой информационных входов дешифратора команд, выход элемента ИЛИ-НЕ соединен с вторым входом второго элемента И, вход устройства для подключения к выходу синхронизации контролируемого микропроцессора соединен с входом

установки в 1 третьего триггера, входом синхронизации первого триггера, с первым входом второго элемента ИЛИ, выход которого соединен с входом установки в О счетчика, выход первого элемента ИЛИ соединен с входом установки в 1 четвертого триггера, прямой выход которого соединен с первым входом третьего элемента ИЛИ, вход устройства для подключения к выходу приема информации контролируемого микропроцессора соединен с вторым входом третьего элемента ИЛИ, вход устройства для подключения к выдаче информации выходу контролируемого микропроцессора соединен через элемент НЕ с третьим входом третьего элемента ИЛИ, выход счетчика подключен к входу установки в 1 пятого триггера, выход первого элемента И соединен с первым входом четвертого элемента ИЛИ, выход которого соединен с входом

установки в О четвертого триггера, второй тактовый вход устройства соединен с входами синхронизации третьего и пятого триггеров, вход начальной установки устройства соединен с вторым входом четвертого элемента ИЛИ, с вторым входом второго элемента ИЛИ, с входом установки в О пятого триггера и четвертым входом третьего элемента ИЛИ, выход

которого соединен с входом установки в О третьего триггера, прямой выход которого соединен с информационным входом первого триггера, прямой выход которого соединен с первым входом пятого элемента

ИЛИ, прямой выход пятого триггера соединен с вторым входом пятого элемента ИЛИ, выход которого является выходом ошибки устройства, К-входы третьего и пятого триггеров подключены к шине нулевого потенциала устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля управляющих сигналов микропроцессора | 1989 |

|

SU1656536A1 |

| Устройство для контроля условных переходов микропроцессора | 1984 |

|

SU1238076A1 |

| Устройство для контроля микропроцессорной системы | 1985 |

|

SU1287161A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1753474A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

| Электронная вычислительная машина для ускоренной обработки запросов прерываний | 1988 |

|

SU1621029A1 |

| Устройство для резервирования и восстановления микропроцессорной системы | 1986 |

|

SU1374235A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1815638A1 |

| Микропроцессорная система с контролем | 1984 |

|

SU1242976A1 |

| Устройство для контроля микропроцессорной системы | 1984 |

|

SU1221655A1 |

sd ф

СБРОС

фиг /

Mi

. Ф21

. t

Хссп УД1ГУно(

MS.

Фиг 2.

Авторы

Даты

1992-09-30—Публикация

1990-12-18—Подача