Изобретение относится к области автоматики и вычислительной техники и может быть использовано в системах числового программного управления.

Известно устройство, состоящее из блока ввода, счетчика строк, преобразователя кода, блока памяти, блока отработки координатных перемещений, контрольного счетчика по модулю 9.

В указанном устройстве контрольное число вводится в контрольный счетчик с перфоленты. Устройство позволяет контролировать правильность считывания управляющей программы. К недостаткам устройства следует отнести необходимость предварительного расчета контрольного

числа и пробивку его на перфоленте, что усложняет расчет программы, увеличивает длину кадра и объем запоминающего устройства. Кроме того, усложняется процесс редактирования программы, т.к. возникает необходимость редактирования и контрольного числа.

Известно также устройство, содержащее блок ввода программы, выходы которого соединены со входами счетчика строк, преобразователя кода и блока памяти, соединенного со входами блока отработки координатных перемещений и контрольного счетчика, причем выход блока отработки координатных перемещений соединен со входом контрольного счетчика, а выходы

х|

ч ел

4

.&

о

счетчика строк и преобразователя кода через элемент И соединены со счетчиком, выход которого подключен к блоку памяти.

Наиболее близким к изобретению техническим решением является устройство состоящее из блока ввода программ, выход которого соединен с входом блока отработки координатных перемещений, подключенного первым выходом к входу контрольного счетчика, первый выход первого блока сравнения соединен с выходом контрольного счетчика, а второй вход - с выходом первого регистра, выход первого блока сравнения подключен к первому входу элемента И, второй вход которого соединен со вторым выходом блока отработки координатных перемещений и со входом записи первого регистра. Информационный вход первого регистра соединен со вторым входом первого сумматора и с выходом второго регистра. Вход записи второго регистра соединен с первым входом самого устройства, а информационный вход - с выходом второго сумматора, первый вход которого соединен с выходом блока формирования кода. Вход этого блока соединен с выходом второго блока сравнения, первый вход которого подсоединен ко второму входу всего устройства, а второй вход - ко входу сумматора и к выходу первого сумматора, первый вход которого соединен с выходом блока ввода программы.

Недостатком данного устройства является низкая периодичность контроля: устройство контролирует правильность отработки в конце каждого кадра. Однако неисправность может возникать в ходе отработки кадра. При этом может быть отработано перемещение как меньшее, так и большее заданного. При отработке детали, несмотря на аварийный останов, деталь и станок могут быть испорчены. Особенно повышается вероятность неисправностей при использовании устройства в системах с большим временем работы (например, круглосуточно в составе ГПМ).

Целью изобретения является повышение эффективности контроля: контроль в предлагаемом устройстве осуществляется через каждые восемь импульсов тактовой частоты интерполятора.

С этой целью в устройство контроля для систем программного управления, содержащее первый и второй сумматоры, формирователь дополнительного кода, регистр, первый и второй блоки сравнения, элемент И, первый вход элемента И соединен с выходом первого блока сравнения, выход элемента И соединен с выходом устройства, первый вход первого блока сравнения соединен с выходом регистра, информационный вход которого соединен с первой группой входов первого сумматора, выход которого соединен с первыми входами второго блока сравнения и второго сумматора, второй вход второго блока сравнения соединен с входом устройства, выход второго блока сравнения соединен с входом формирователя дополнительного кода, вы0 ход которого соединен со вторым входом второго сумматора, дополнительно введены первый и второй элементы задержки, элемент ИЛИ, счетчик импульсов, делитель частоты, блок задания программы, сдвиговый

5 регистр, третий сумматор, первый и второй

блоки свертки по модулю 9, группа выхо. дов первого блока свертки по модулю 9

соединена с первой группой информационных

входов регистра, вход соединен с выходом

0 сдвигового регистра, первый и второй входы которого соединены соответственно с первым и вторым выходами блока задания программы, третий вход сдвигового регистра соединен с входом синхроимпульса, чет5 вертый вход соединен с первым входом счетчика импульсов и с выходом первого элемента задержки, группа информационных входов сдвигового регистра соединена с группой выходов второго сумматора, тре0 тий выход блока задания программы соединен соответственно с первыми входами делителя частоты, первого элемента задержки и со вторым входом запись регистра, четвертый выход соединен с входом второго

5 блока свертки по модулю 9, пятый и шестой выходы соединены соответственно с первым и вторым входами элемента ИЛИ, седьмой выход соединен со второй группой входов первого сумматора, восьмой выход

0 соединен со вторым входом делителя частоты, выход которого соединен с входом второго элемента задержки, выход элемента задержки соединен со вторым входом элемента И, выход элемента ИЛИ соединен со

5 вторым входом счетчика импульсов, выход которого соединен с первым входом третьего сумматора, второй вход которого соединен с выходом второго блока свертки по модулю 9, выход третьего сумматора сое0 динен со вторым входом первого блока сравнения.

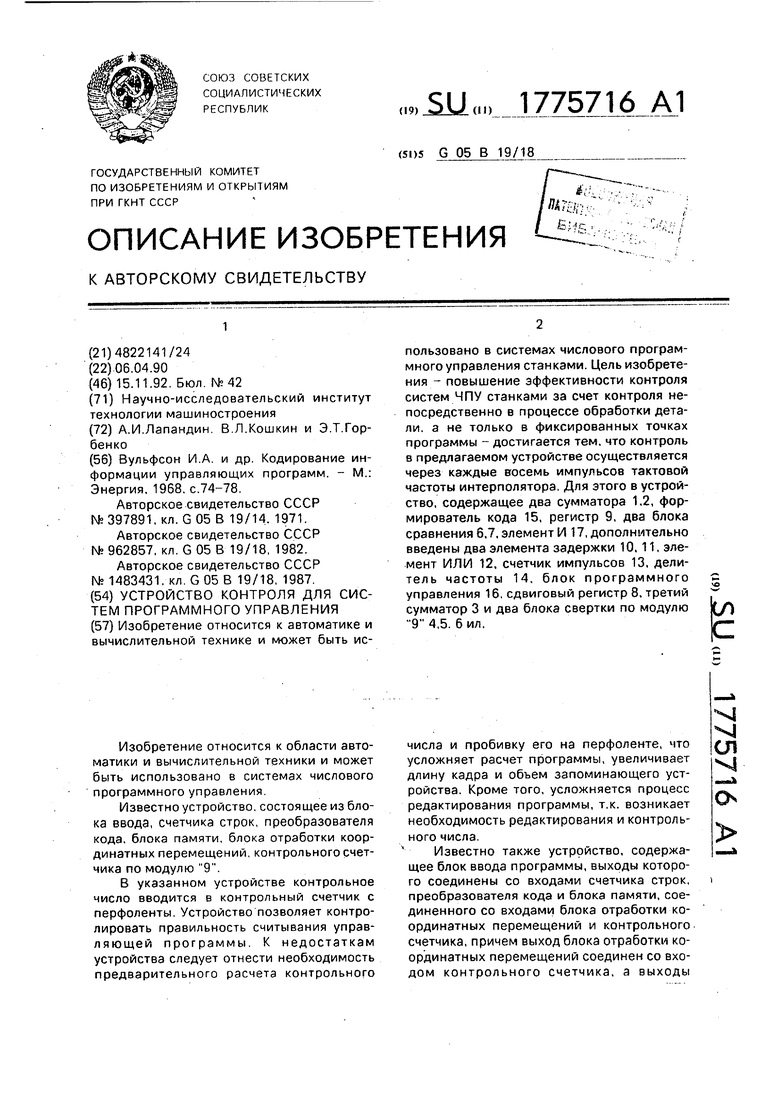

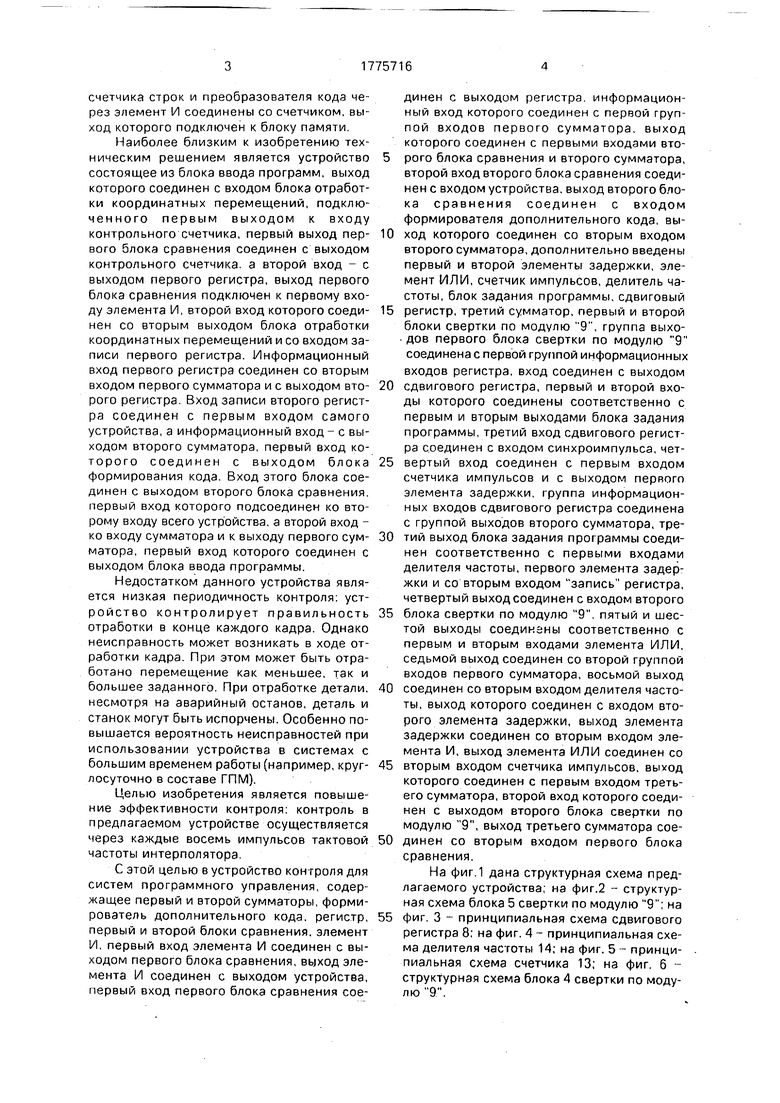

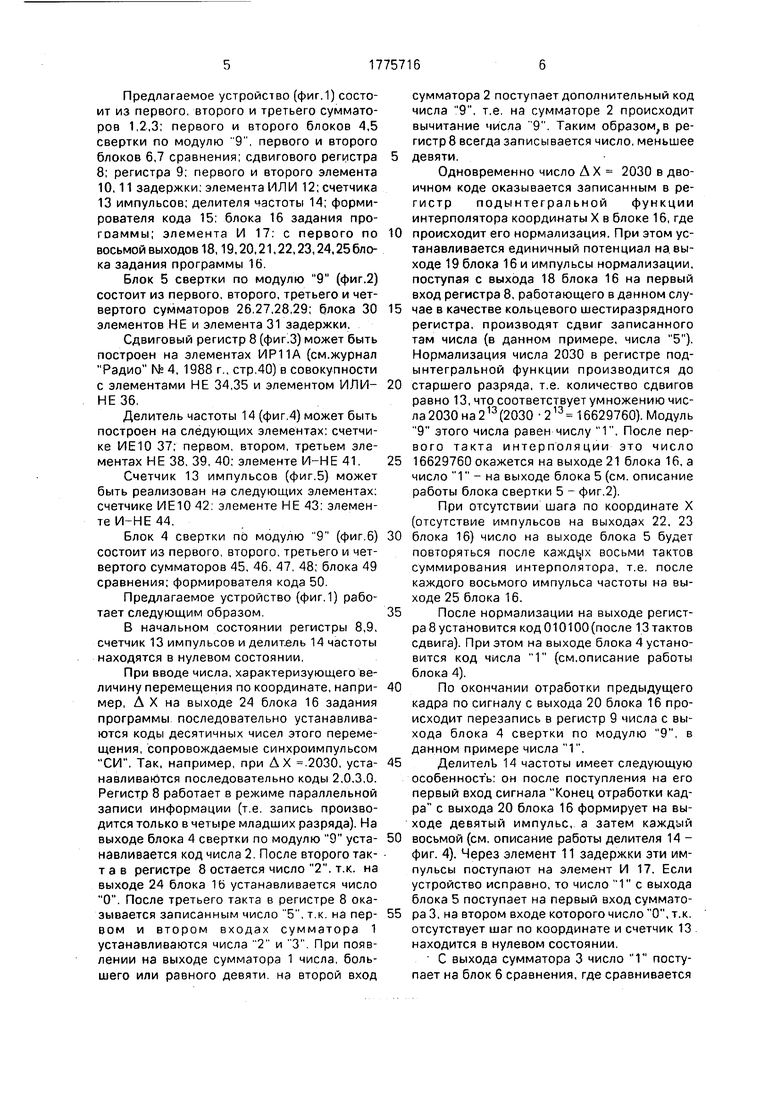

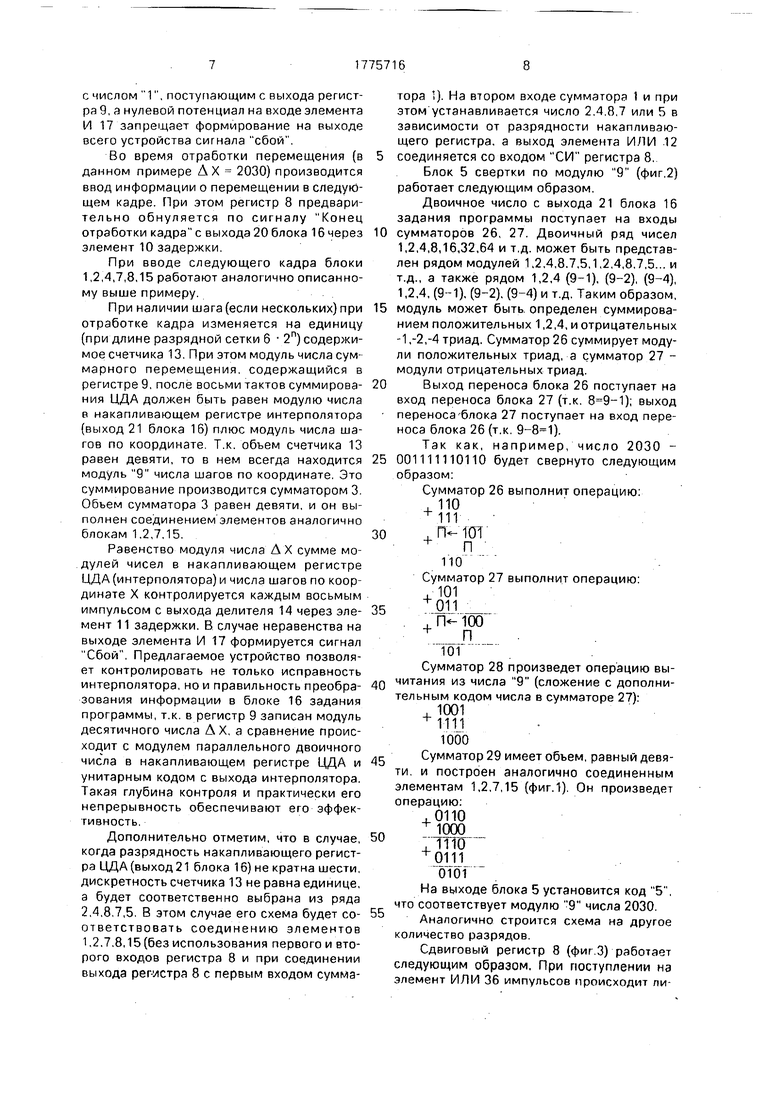

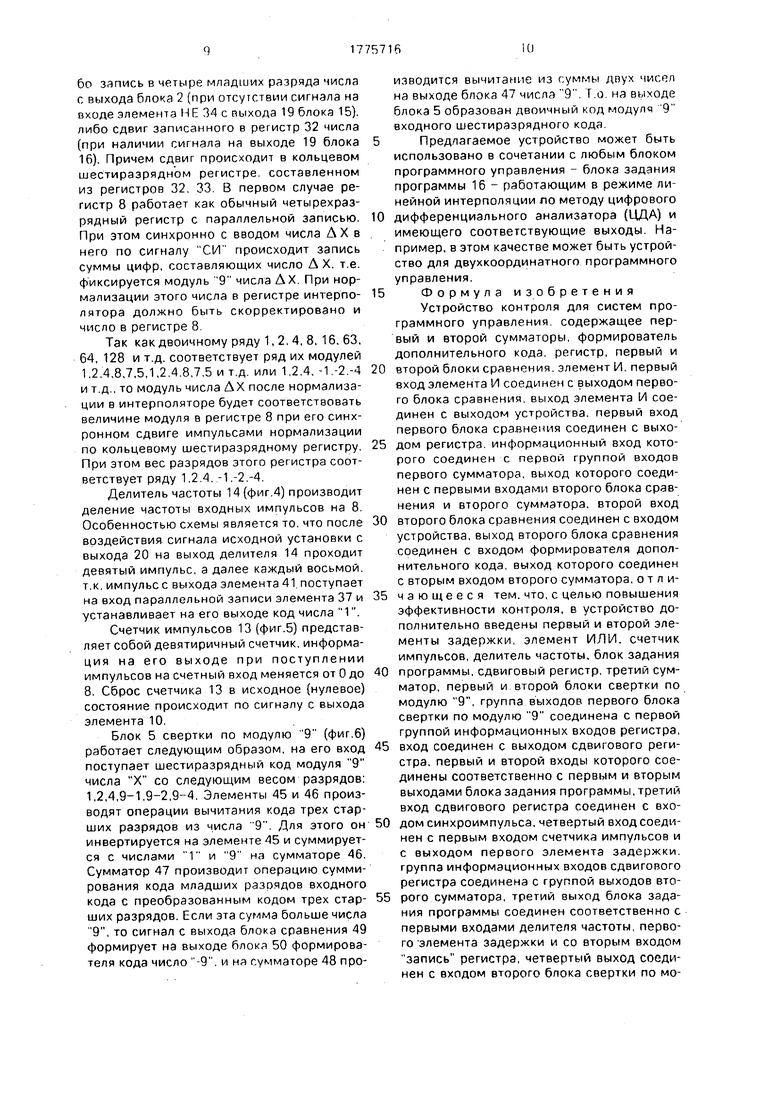

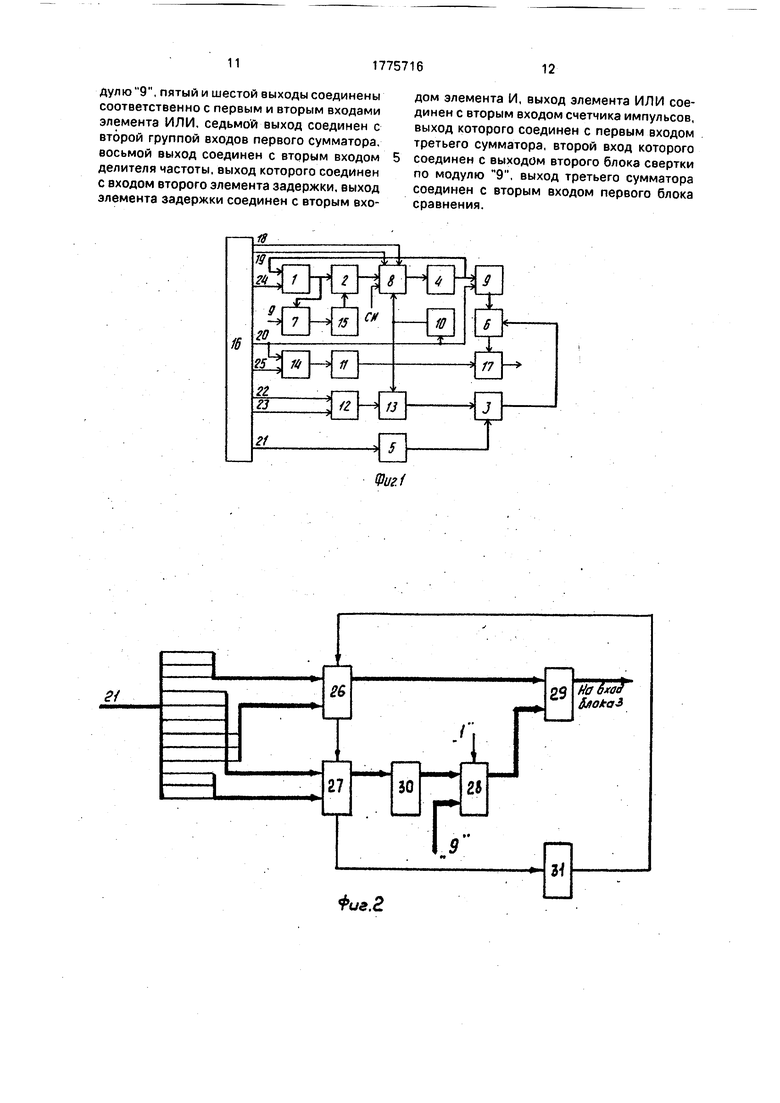

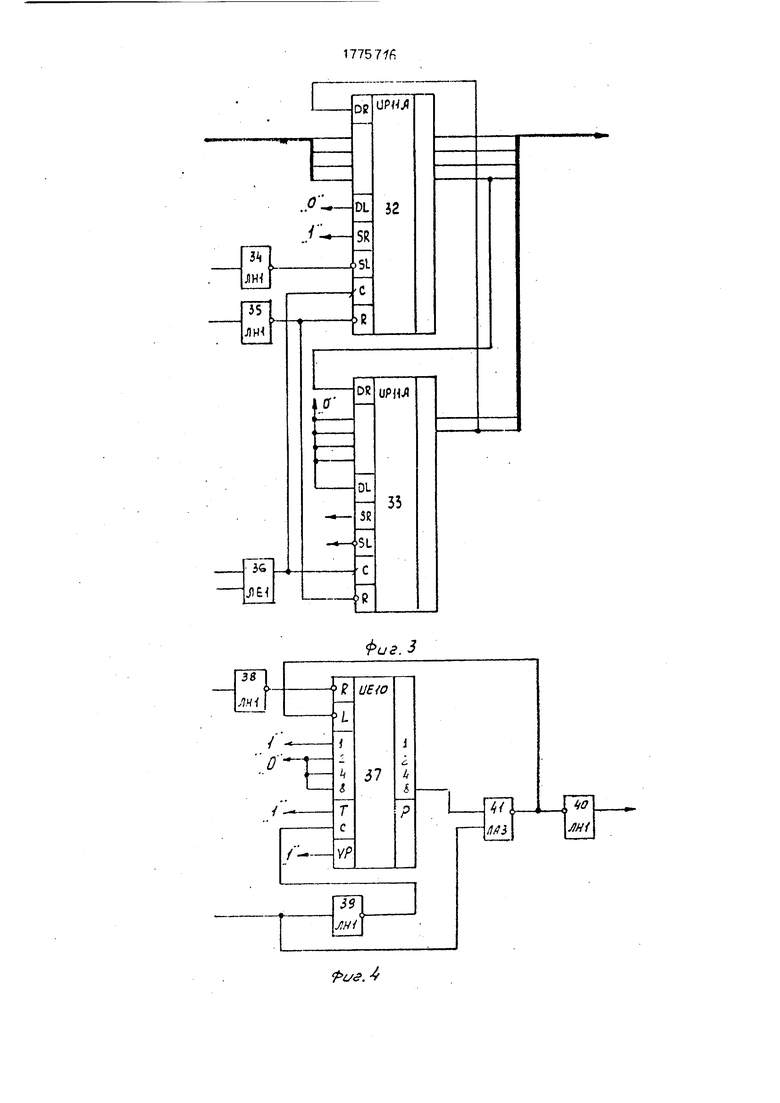

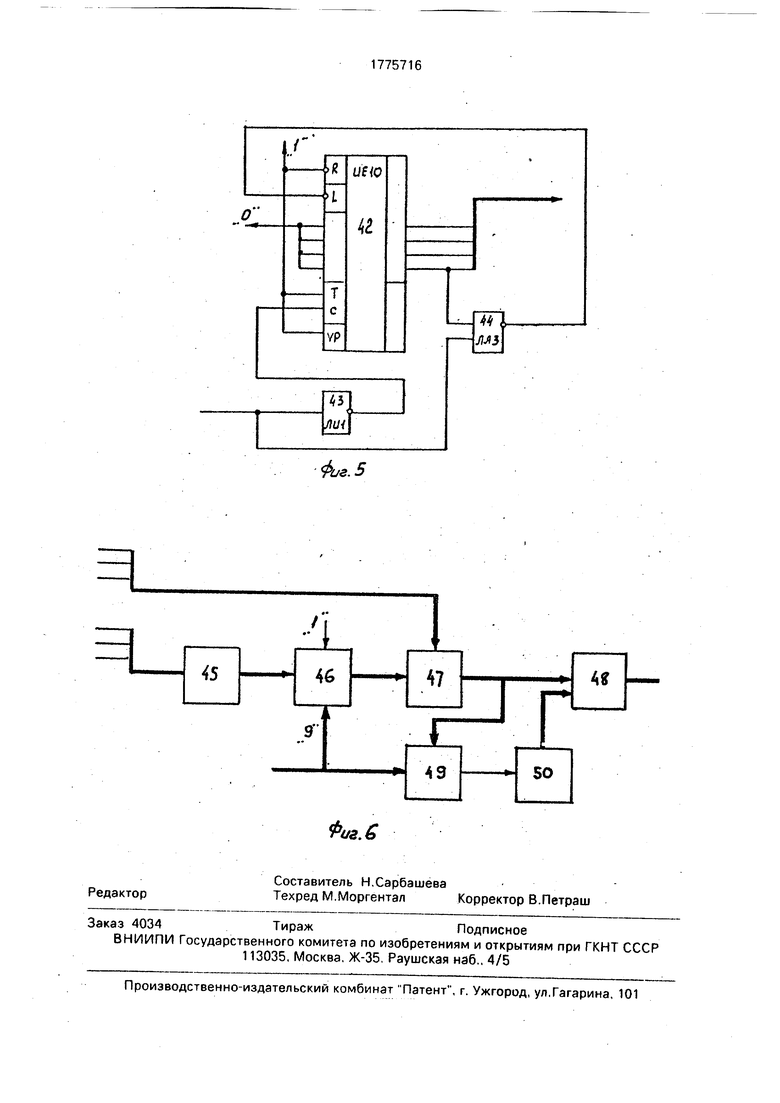

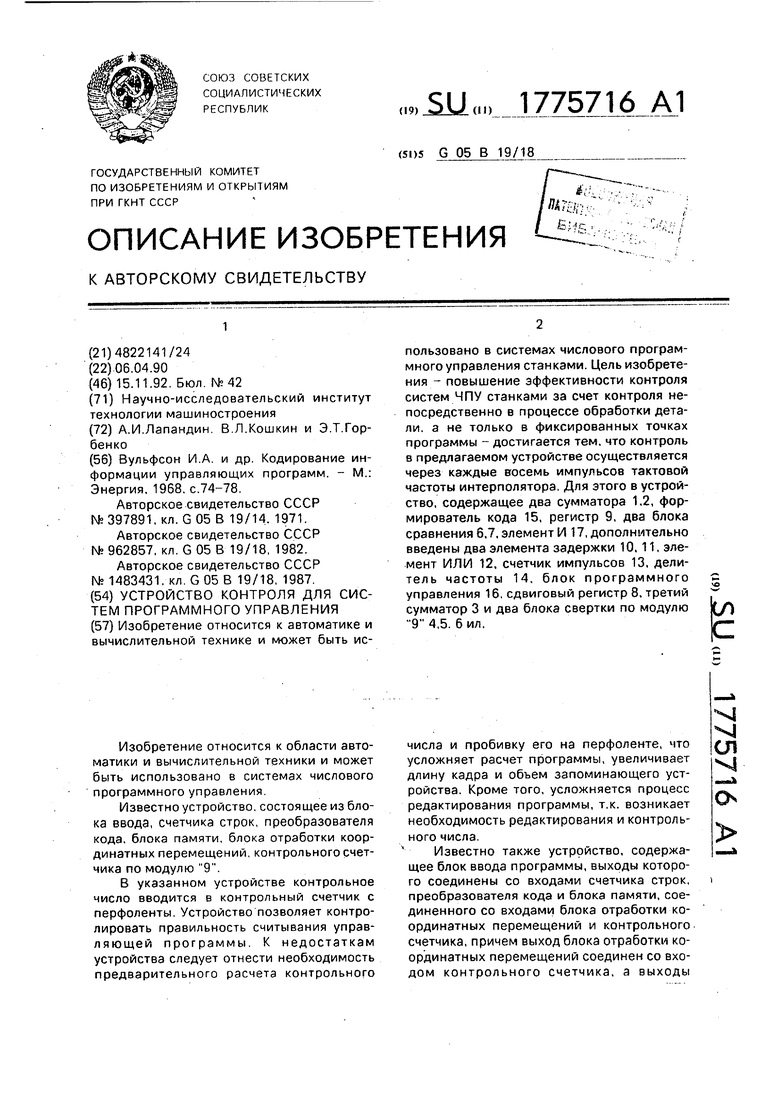

На фиг.1 дана структурная схема предлагаемого устройства; на фиг.2 - структурная схема блока 5 свертки по модулю на

5 фиг. 3 - принципиальная схема сдвигового регистра 8; на фиг. 4 - принципиальная схема делителя частоты 14; на фиг. 5 - принципиальная схема счетчика 13; на фиг. 6 - структурная схема блока 4 свертки по модулю 9.

Предлагаемое устройство (фиг.1) состоит из первого, второго и третьего сумматоров 1,2,3; первого и второго блоков 4,5 свертки по модулю 9, первого и второго блоков 6,7 сравнения; сдвигового регистра 8; регистра 9; первого и второго элемента 10,11 задержки; элемента ИЛИ 12; счетчика 13 импульсов; делителя частоты 14; формирователя кода 15; блока 16 задания про- гоаммы; элемента И 17: с первого по восьмой выходов 18,19,20,21,22,23,24,25блока задания программы 16.

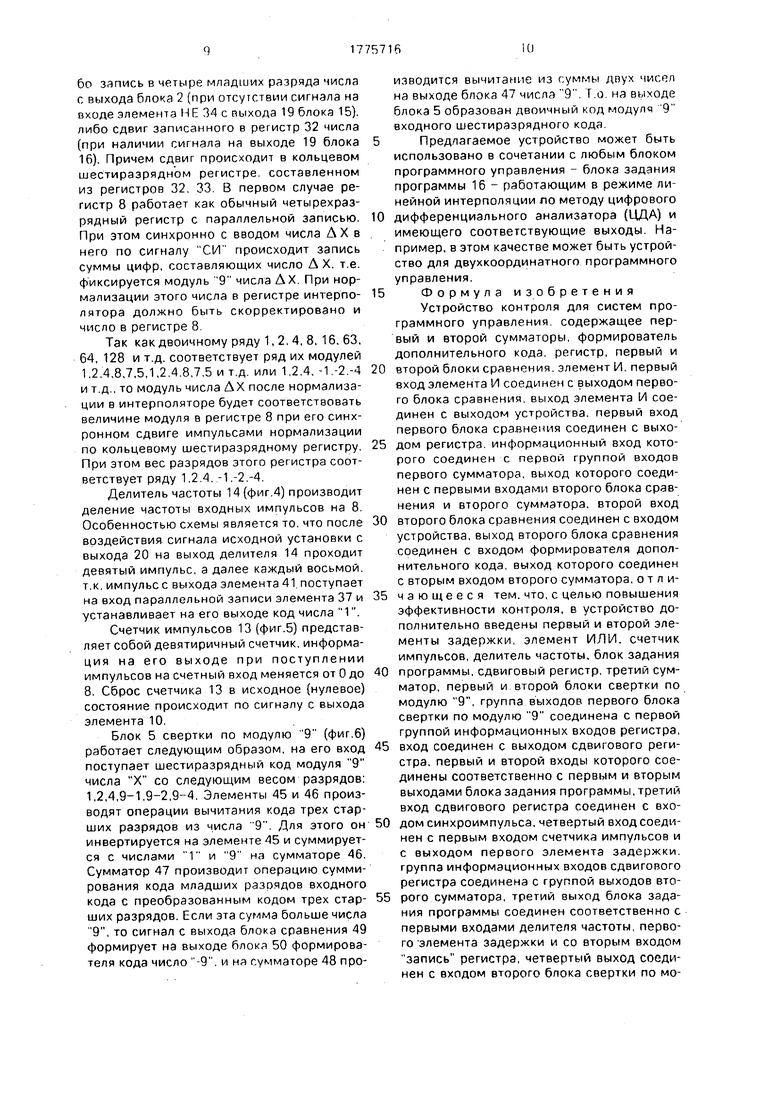

Блок 5 свертки по модулю 9 (фиг.2) состоит из первого, второго, третьего и четвертого сумматоров 26,27,28,29; блока 30 элементов НЕ и элемента 31 задержки.

Сдвиговый регистр 8 (фиг.З) может быть построен на элементах ИР11А (см.журнал Радио № 4, 1988 г., стр.40) в совокупности с элементами НЕ 34,35 и элементом ИЛИ- НЕ 36,

Делитель частоты 14 (фиг.4) может быть построен на следующих элементах: счетчике ИЕ10 37; первом, втором, третьем элементах НЕ 38, 39, 40; элементе И-НЕ 41.

Счетчик 13 импульсов (фиг.5) может быть реализован на следующих элементах: счетчике ИЕ10 42. элементе НЕ 43: элементе И-НЕ 44.

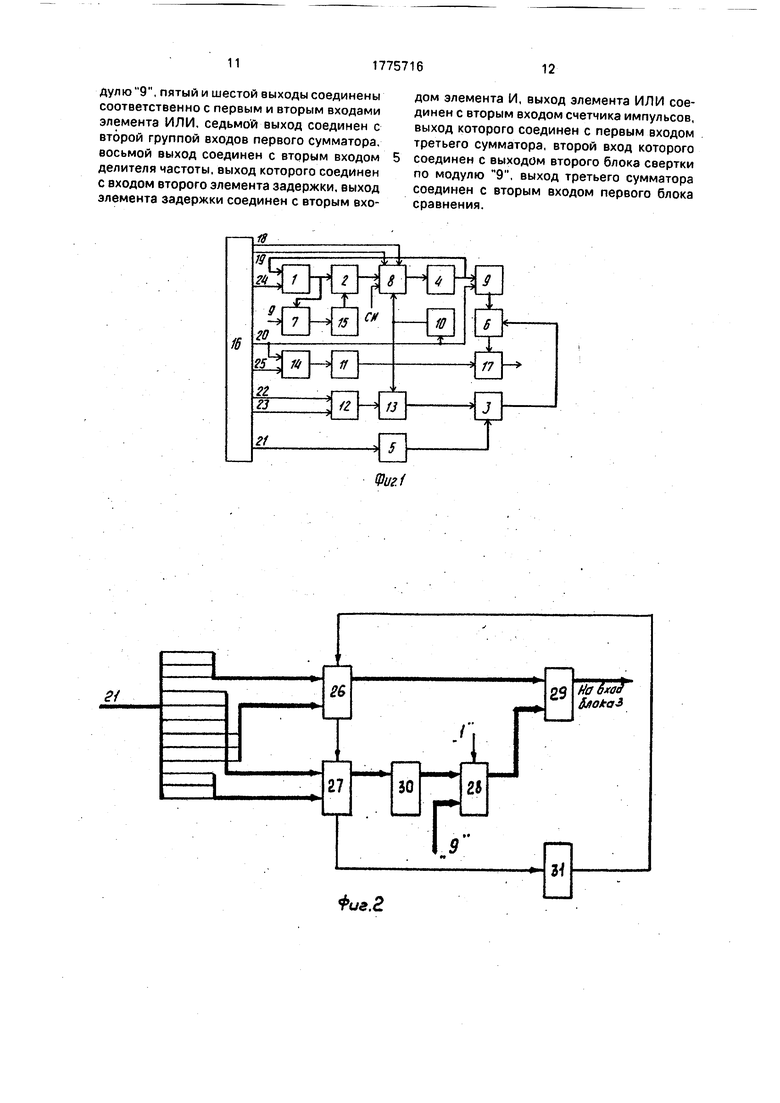

Блок 4 свертки по модулю 9 (фиг.6) состоит из первого, второго, третьего и четвертого сумматоров 45, 46. 47, 48; блока 49 сравнения; формирователя кода 50.

Предлагаемое устройство (фиг.1) работает следующим образом.

В начальном состоянии регистры 8,9, счетчик 13 импульсов и делитель 14 частоты находятся в нулевом состоянии,

При вводе числа, характеризующего величину перемещения по координате, напри- мер, Д X на выходе 24 блока 16 задания программы последовательно устанавливаются коды десятичных чисел этого перемещения, сопровождаемые синхроимпульсом СИ, Так, например, при ДХ .2030, уста- навливаются последовательно коды 2,0,3,0. Регистр 8 работает в режиме параллельной записи информации (т.е. запись производится только в четыре младших разряда). На выходе блока 4 свертки по модулю 9 уста- навливается код числа 2. После второго так- т а в регистре 8 остается число 2. т.к. на выходе 24 блока 1Ь устанавливается число О. После третьего такта в регистре 8 оказывается записанным число 5, т.к. на пер- вом и втором входах сумматора 1 устанавливаются числа 2 и 3. При появлении на выходе сумматора 1 числа, большего или равного девяти, на второй вход

сумматора 2 поступает дополнительный код числа 9, т.е. на сумматоре 2 происходит вычитание числа 9. Таким образом, в регистр 8 всегда записывается число, меньшее девяти.

Одновременно число Д X 2030 в двоичном коде оказывается записанным в регистр подынтегральной функции интерполятора координаты X в блоке 16, где происходит его нормализация. При этом устанавливается единичный потенциал на выходе 19 блока 16 и импульсы нормализации, поступая с выхода 18 блока 16 на первый вход регистра 8, работающего в данном случае в качестве кольцевого шестиразрядного регистра, производят сдвиг записанного там числа (в данном примере, числа 5). Нормализация числа 2030 в регистре подынтегральной функции производится до старшего разряда, т.е. количество сдвигов равно 13, что соответствует умножению числа 2030 на 213(2030 213 16629760). Модуль 9 этого числа равен числу 1. После первого такта интерполяции это число 16629760 окажется на выходе 21 блока 16, а число 1 - на выходе блока 5 (см. описание работы блока свертки 5 - фиг.2).

При отсутствии шага по координате X (отсутствие импульсов на выходах 22, 23 блока 16) число на выходе блока 5 будет повторяться после каждых восьми тактов суммирования интерполятора, т.е. после каждого восьмого импульса частоты на выходе 25 блока 16.

После нормализации на выходе регистра 8 установится код 010100 (после 13 тактов сдвига). При этом на выходе блока 4 установится код числа 1 (см.описание работы блока 4).

По окончании отработки предыдущего кадра по сигналу с выхода 20 блока 16 происходит перезапись в регистр 9 числа с выхода блока 4 свертки по модулю 9, в данном примере числа 1.

Делитель 14 частоты имеет следующую особенность: он после поступления на его первый вход сигнала Конец отработки кадра с выхода 20 блока 16 формирует на выходе девятый импульс, а затем каждый восьмой (см. описание работы делителя 14 - фиг. 4). Через элемент 11 задержки эти импульсы поступают на элемент И 17. Если устройство исправно, то число 1 с выхода блока 5 поступает на первый вход сумматора 3, на втором входе которого число О, т.к. отсутствует шаг по координате и счетчик 13 находится в нулевом состоянии.

С выхода сумматора 3 число 1 поступает на блок 6 сравнения, где сравнивается

с числом 1, поступающим с выхода регистра 9, а нулевой потенциал на входе элемента И 17 запрещает формирование на выходе всего устройства сигнала сбой.

Во время отработки перемещения (в данном примере ДХ - 2030) производится ввод информации о перемещении в следующем кадре. При этом регистр 8 предварительно обнуляется по сигналу Конец отработки кадра с выхода 20 блока 16 через элемент 10 задержки.

При вводе следующего кадра блоки 1,2,4,7,8,15 работают аналогично описанному выше примеру.

При наличии шага (если нескольких) при отработке кадра изменяется на единицу (при длине разрядной сетки 6 2П) содержимое счетчика 13. При этом модуль числа суммарного перемещения, содержащийся в регистре 9, после восьми тактов суммирования ЦДА должен быть равен модулю числа а накапливающем регистре интерполятора (выход 21 блока 16) плюс модуль числа шагов по координате Т.к. объем счетчика 13 равен девяти, то в нем всегда находится модуль 9 числа шагов по координате. Это суммирование производится сумматором 3 Объем сумматора 3 равен девяти, и он выполнен соединением элементов аналогично блокам 1.2,7,15.

Равенство модуля числа ДХ сумме модулей чисел в накапливающем регистре ЦДА (интерполятора) и числа шагов по координате X контролируется каждым восьмым импульсом с выхода делителя 14 через элемент 11 задержки. В случае неравенства на выходе элемента И 17 формируется сигнал Сбой. Предлагаемое устройство позволяет контролировать не только исправность интерполятора, но и правильность преобразования информации в блоке 16 задания программы, т.к. в регистр 9 записан модуль десятичного числа ДХ, а сравнение происходит с модулем параллельного двоичного числа в накапливающем регистре ЦДА и унитарным кодом с выхода интерполятора. Такая глубина контроля и практически его непрерывность обеспечивают его эффективность.

Дополнительно отметим, что в случае, когда разрядность накапливающего регистра ЦДА (выход 21 блока 16) не кратна шести, дискретность счетчика 13 не равна единице, а будет соответственно выбрана из ряда 2,4,8,7,5. В этом случае его схема будет соответствовать соединению элементов 1,2,7.8,15 (без использования первого и второго входов регистра 8 и при соединении выхода регистра 8 с первым входом суммагора 1). На втором входе сумматора 1 и при этом устанавливается число 2.4.8,7 или 5 в зависимости от разрядности накапливающего регистра, а выход элемента ИЛИ 12 соединяется со входом СИ регистра 8.

Блок 5 свертки по модулю 9 (фиг.2) работает следующим образом.

Двоичное число с выхода 21 блока 16 задания программы поступает на входы 0 сумматоров 26, 27. Двоичный ряд чисел 1,2,4,8,16,32,64 и т.д. может быть представлен рядом модулей 1,2,4,8.7,5,1,2,4,8.7,5... и т.д., а также рядом 1,2,4 (9-1), (9-2), (9-4), 1,2,4, (9-1). (9-2). (9-4) и т.д. Таким образом, 5 модуль может быть определен суммированием положительных 1,2,4, и отрицательных -1 ,-2,-4 триад. Сумматор 26 суммирует модули положительных триад, а сумматор 27 - модули отрицательных триад. 0Выход переноса блока 26 поступает на

вход переноса блока 27 (т.к. ), выход переноса блока 27 поступает на вход переноса блока 26 (т.к. ).

Так как, например, число 2030 - 5 001111110110 будет свернуто следующим образом:

Сумматор 26 выполнит операцию: 110 111

+

+

п

ют

п

110

Сумматор 27 выполнит операцию: 101

+

+

01.1

п

100

п

10 Г

0

5

0

5

Сумматор 28 произведет операцию вычитания из числа 9 (сложение с дополнительным кодом числа в сумматоре 27):

,1001

+ 1111

1000

Сумматор 29 имеет объем, равный девяти и построен аналогично соединенным элементам 1,2,7,15 (фиг.1). Он произведет операцию: 0110 1000

гпо

0111 0101

На выходе блока 5 установится код 5, что соответствует модулю 9 числа 2030.

Аналогично строится схема на другое количество разрядов.

Сдвиговый регистр 8 (фиг 3) работает следующим образом. При поступлении на элемент ИЛИ 36 импульсов происходит ли+

+

бо запись в четыре младших разряда числа с выхода блока 2 (при отсутствии сигнала на входе элемента НЕ 34 с выхода 19 блока 15). либо сдвиг записанного в регистр 32 числа (при наличии сигнала на выходе 19 блока 16). Причем сдвиг происходит в кольцевом шестиразрядном регистре, составленном из регистров 32. 33. В первом случае регистр 8 работает как обычный четырехразрядный регистр с параллельной записью. При этом синхронно с вводом числа ЛХ в него по сигналу СИ происходит запись суммы цифр, составляющих число Д X, т.е. фиксируется модуль 9 числа Д X. При нормализации этого числа в регистре интерпо- лятора должно быть скорректировано и число в регистре 8

Так как двоичному ряду 1,2.4,8, 16. 63, 64, 128 и т.д. соответствует ряд их модулей 1,2.4,8,7,5,1,2,4.8,7.5 и т.д. или 1,2.4. -1.-2.-4 и т.д., то модуль числа ДХ после нормализации в интерполяторе будет соответствовать величине модуля в регистре 8 при его синхронном сдвиге импульсами нормализации по кольцевому шестиразрядному регистру. При этом вес разрядов этого регистра соответствует ряду 1.2.4. -1.-2.-4.

Делитель частоты 14 (фиг.4) производит деление частоты входных импульсов на 8. Особенностью схемы является то. что после воздействия сигнала исходной установки с выхода 20 на выход делителя 14 проходит девятый импульс, а далее каждый восьмой, т.к. импульс с выхода элемента 41 поступает на вход параллельной записи элемента 37 и устанавливает на его выходе код числа 1.

Счетчик импульсов 13 (фиг.5) представляет собой девятиричный счетчик, информация на его выходе при поступлении импульсов на счетный вход меняется от 0 до 8. Сброс счетчика 13 в исходное (нулевое) состояние происходит по сигналу с выхода элемента 10.

Блок 5 свертки по модулю 9 (фиг.6) работает следующим образом, на его вход поступает шестиразрядный код модуля 9 числа X со следующим весом разрядов: 1,2,4,9-1,9-2,9-4. Элементы 45 и 46 производят операции вычитания кода трех старших разрядов из числа 9. Для этого он инвертируется на элементе 45 и суммируется с числами 1 и 9 на сумматоре 46. Сумматор 47 производит операцию суммирования кода младших разоядов входного кода с преобразованным кодом трех стар- ших разрядов. Если эта сумма больше числа 9, то сигнал с выхода блока сравнения 49 формирует на выходе блока 50 формирователя кода число -9. и ня сумматоре 48 производится вычитание из суммы двух чисел на выходе блока 47 числа 9. Г.о на выходе блока 5 образован двоичный код модуля 9 входного шестиразрядного кода

Предлагаемое устройство может быть использовано в сочетании с любым блоком программного управления - блока задания программы 16 - работающим в режиме линейной интерполяции ло методу цифрового дифференциального анализатора (ЦДА) и имеющего соответствующие выходы. Например, в этом качестве может быть устройство для двухкоординатного программного управления.

Формула изобретения Устройство контроля для систем программного управления содержащее первый и второй сумматоры, формирователь дополнительного кода, регистр, первый и второй блоки сравнения, элемент И, первый вход элемента И соединен с выходом первого блока сравнения, выход элемента И соединен с выходом устройства, первый вход первого блока сравнения соединен с выходом регистра, информационный вход которого соединен с первой группой входов первого сумматора, выход которого соединен с первыми входами второго блока сравнения и второго сумматора, второй вход второго блока сравнения соединен с входом устройства, выход второго блока сравнения соединен с входом формирователя дополнительного кода, выход которого соединен с вторым входом второго сумматора, отличающееся тем. что, с целью повышения эффективности контроля, в устройство дополнительно введены первый и второй элементы задержки, элемент ИЛИ, счетчик импульсов, делитель частоты, блок задания программы, сдвиговый регистр, третий сумматор, первый и второй блоки свертки по модулю 9, группа выходов первого блока свертки по модулю 9 соединена с первой группой информационных входов регистра, вход соединен с выходом сдвигового регистра, первый и второй входы которого соединены соответственно с первым и вторым выходами блока задания программы, третий вход сдвигового регистра соединен с входом синхроимпульса, четвертый вход соединен с первым входом счетчика импульсов и с выходом первого элемента задержки, группа информационных входов сдвигового регистра соединена с группой выходов второго сумматора, третий выход блока задания программы соединен соответственно с первыми входами делителя частоты, первого элемента задержки и со вторым входом запись регистра, четвертый выход соединен с входом второго блока свертки по модулю 9, пятый и шестой выходы соединены соответственно с первым и вторым входами элемента ИЛИ, седьмой выход соединен с второй группой входов первого сумматора, восьмой выход соединен с вторым входом делителя частоты, выход которого соединен с входом второго элемента задержки, выход элемента задержки соединен с вторым входом элемента И, выход элемента ИЛИ соединен с вторым входом счетчика импульсов, выход которого соединен с первым входом третьего сумматора, второй вход которого соединен с выходом второго блока свертки по модулю 9, выход третьего сумматора соединен с вторым входом первого блока сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задания программы | 1979 |

|

SU849148A1 |

| Линейно-круговой интерполятор | 1978 |

|

SU746431A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Устройство для задания программы | 1979 |

|

SU862118A1 |

| Цифровой интерполятор | 1984 |

|

SU1238033A1 |

| Линейно-круговой интерполятор | 1986 |

|

SU1312530A1 |

| Устройство для программного управления | 1986 |

|

SU1397878A1 |

| Линейно-круговой интерполятор | 1979 |

|

SU847279A1 |

| Устройство для программного управления | 1984 |

|

SU1218368A1 |

| Программное задающее устройство | 1981 |

|

SU991376A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах числового программного управления станками. Цель изобретения - повышение эффективности контроля систем ЧПУ станками за счет контроля непосредственно в процессе обработки детали, а не только в фиксированных точках программы - достигается тем. что контроль в предлагаемом устройстве осуществляется через каждые восемь импульсов тактовой частоты интерполятора, Для этого в устройство, содержащее два сумматора 1,2, формирователь кода 15, регистр 9, два блока сравнения 6.7, элемент И 17, дополнительно введены два элемента задержки 10.11, элемент ИЛИ 12, счетчик импульсов 13, делитель частоты 14, блок программного управления 16, сдвиговый регистр 8. третий сумматор 3 и два блока свертки по модулю 9 4,5. 6 ил. сл С

Фиг.2

Фиг. 5

| Вульфсон И.А | |||

| и др | |||

| Кодирование информации управляющих программ | |||

| - М.: Энергия, 1968, с.74-78 | |||

| 0 |

|

SU397891A1 | |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство контроля по модулю 9 для программного управления | 1987 |

|

SU1483431A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1992-11-15—Публикация

1990-04-06—Подача