1

Изобретение относится к автоматике и вычислительной технике и может быть использовано.в системах числового программного управления станками в тех случаях, когда необходимо поддерживать с высокой точностью постоянную контурную скорость.

Целью изобретения является повышение точности устройства за счет поддержания постоянства контурной скорости, расширение его функционал ных возможностей и повышение производительности.

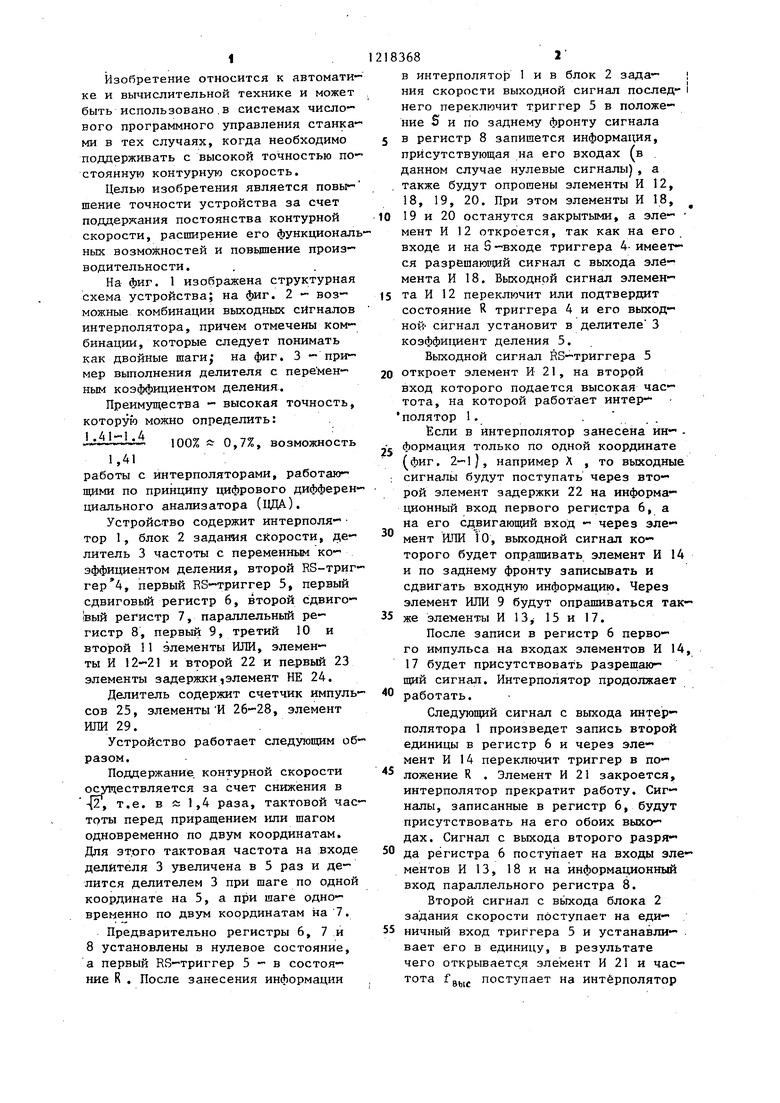

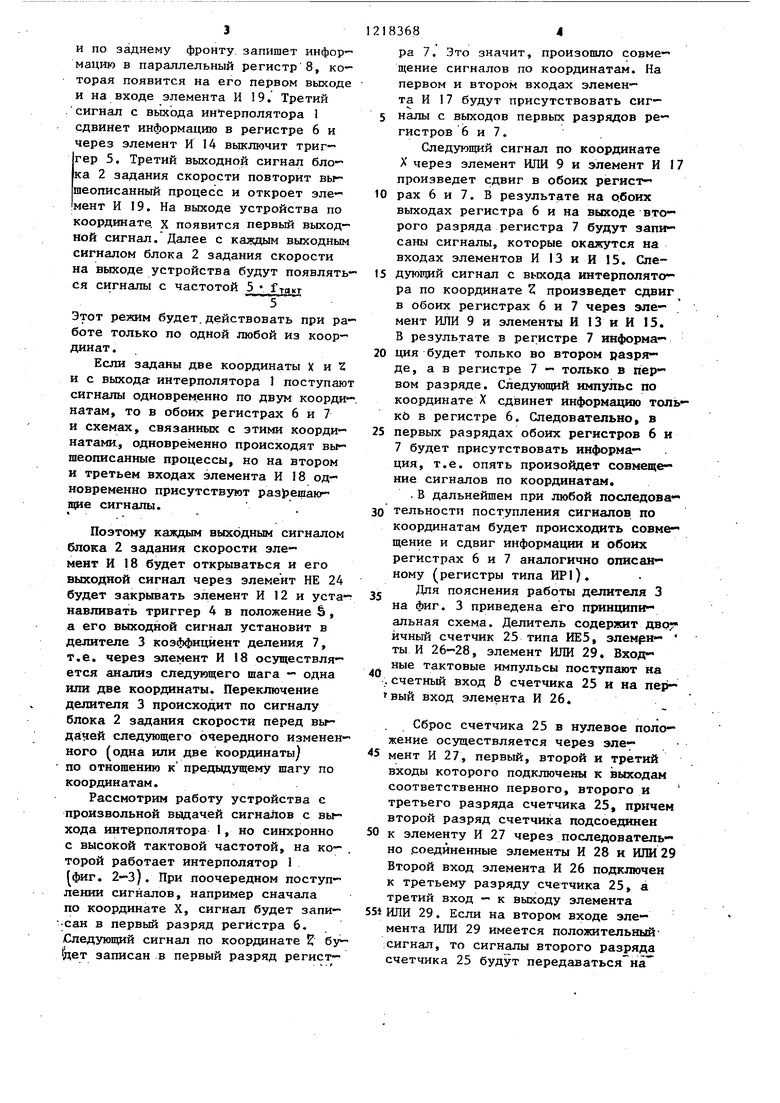

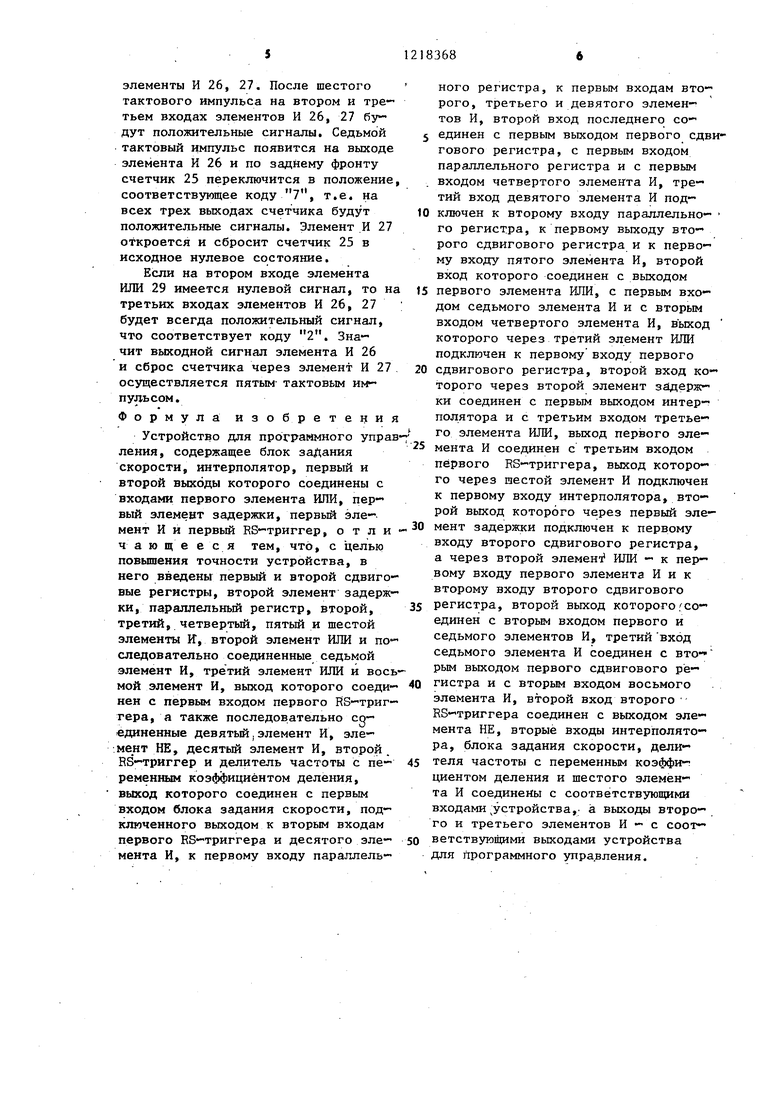

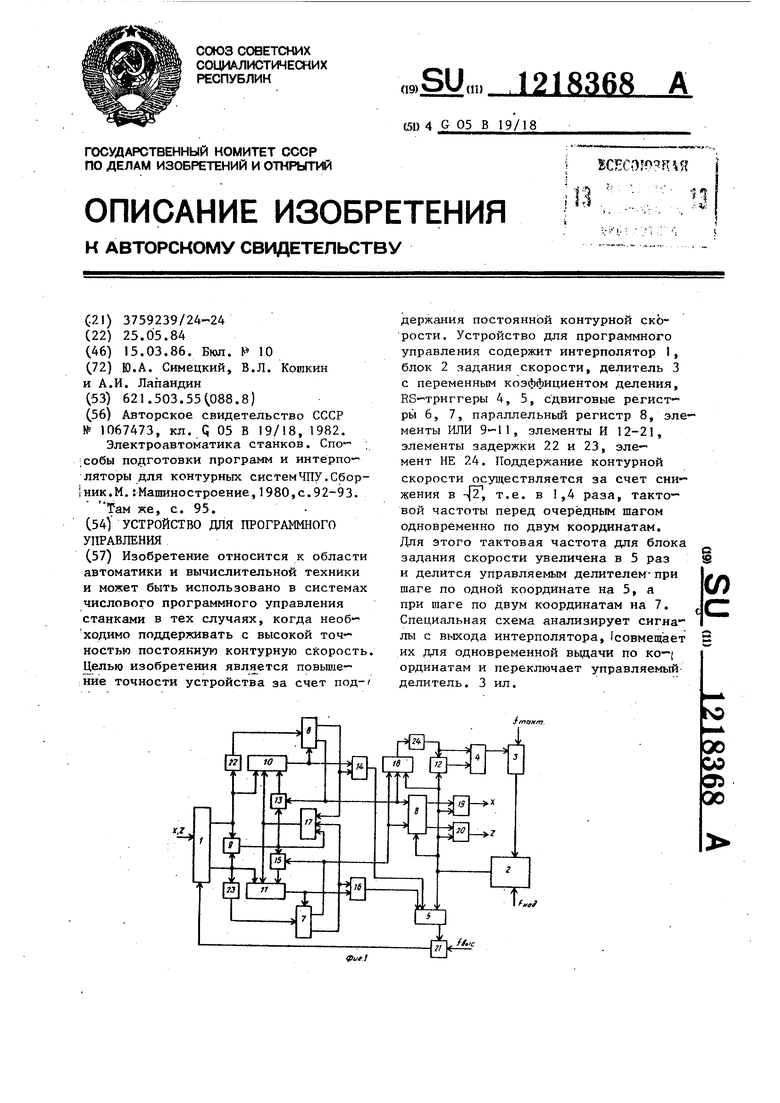

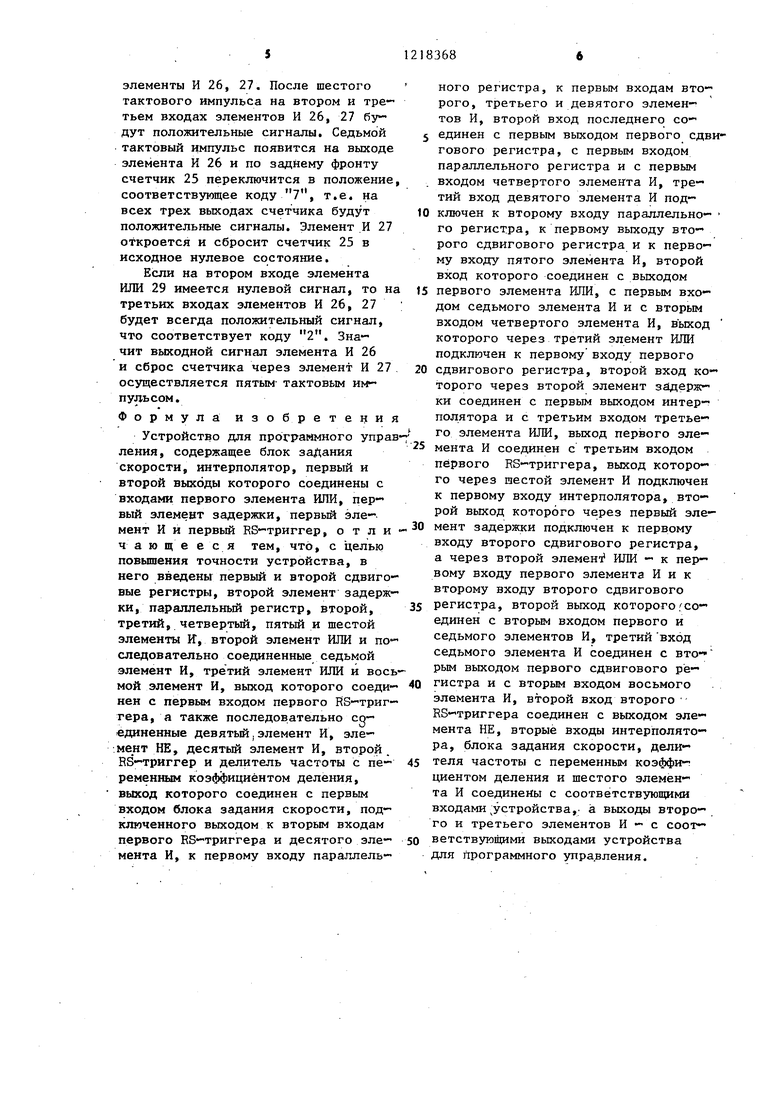

На фиг. 1 изображена структурная схема устройства; на фиг. 2 - возможные комбинации выходных сигналов интерполятора, причем отмечены комбинации, которые следует понимать как двойные шаги; на фиг. 3 - пример выполнения делителя с переменным коэффициентом деления.

Преимущества - высокая точность, которую можно определить: 1.41-1.4

1,41

100% 0,7%, возможность

работы с интерполяторами, работающими по принципу цифрового дифференциального анализатора (ЦДА).

Устройство содержит интерполя- тор 1, блок 2 задания скорости, fl(e- литель 3 частоты с переменным коэффициентом деления, второй RS-триг- , первый RS-триггер 5, первый сдвиговый регистр 6, второй Ьдвиго- вый регистр 7, параллельный регистр 8, первьй 9, третий 10 и второй 11 элементы ИЛИ, элементы И 12-21 и второй 22 и первый 23 элементы задержки,элемент НЕ 24.

Делитель содержит счетчик импульсов 25, элементы И 26-28, элемент ИЛИ 29..

Устройство работает следующим образом.

Поддержание, контурной скорости осутдествляется за счет снижения в 4, т.е. в л 1,4 раза, тактовой частоты перед приращением или шагом одновременно по двум координатам. Для зт.ого тактовая частота на входе делителя 3 увеличена в 5 раз и делится делителем 3 при шаге по одной координате на 5, а при шаге одновременно по двум координатам на 7.

Предварительно регистры 6, 7 и 8 установлены в нулевое состояние, а первый RS-триггер 5 - в состояние R . После занесения информации

2183682

в интерполятор 1 и в блок 2 зада- | ния скорости выходной сигнал послед-i него переключит триггер 5 в положение S и по заднему фронту сигнала

5 в регистр 8 запишется информация, присутствующая на его входах (в . данном случае нулевые сигналы), а . также будут опрошены элементы И 12, 18, 19, 20. При этом элементы И 18,

10 19 и 20 останутся закрытыми, а эле- мент И 12 откроется, так как на его входе и на 6 -входе триггера 4- имеется разрешаюрщй сигнал с выхода элемента И 18. Выходной сигнал элемен15 та И 12 переключит или подтвердит состояние R триггера 4 и его выходной сигнал установит в делителе 3 коэффициент деления 5.

Выходной сигнал RS-триггера 5

20 откроет элемент И 21, на второй вход которого подается высокая частота, на которой работает интер

полятор 1..

Если в интерполятор занесена ин- 25 формация только по одной координате

(фиг. 2-1), например X , то выходные : сигналы будут поступать через второй элемент задержки 22 на информационный вход первого регистра 6, а на его сдвигающий вход - через элемент ИЛИ 10, выходной сигнал которого будет опрашивать элемент И 14 и по заднему фронту записывать и сдвигать входную информацию. Через элемент ИЛИ 9 будут опрашиваться так-

35 же элементы И13 15и17.

После записи в регистр 6 первого импульса на входах элементов И 14, 17 будет присутствовать разрещаю- щйй сигнал. Интерполятор продолжает

работать.

Следующий сигнал с выхода интерполятора 1 произведет запись второй единицы в регистр 6 и через элемент И 14 переключит триггер в по-

ложение R . Элемент И 21 закроется, интерполятор прекратит работу. Сигналы, записанные в регистр 6, будут присутствовать на его обоих выходах. Сигнал с выхода второго разря-

50 да регистра 6 поступает на входы элементов И 13, 18 и на информационный вход параллельного регистра 8.

Второй сигнал с вьгхода блока 2 задания скорости поступает на еди-

55 ничный вход триггера 5 и устанавли- . вает его в единицу, в результате чего открывается элемент И 21 и частота fg, поступает на интерполятор

30

и по заднему фронту, запишет информацию в параллельный регистр 8, которая появится на его первом выходе и на входе элемента И 19. Третий сигнал с выхода интерполятора 1 сдвинет информацию в регистре 6 и через элемент И 14 вьжлючит триггер 5, Третий выходной сигнал блока 2 задания скорости повторит вышеописанный процесс и откроет элемент И 19. На выходе устройства по координате, х появится первый выходной сигнал. Далее с каждым выходным сигналом блока 2 задания скорости на выходе устройства будут появляться сигналы с частотой 5 f тд.кг

5

Этот режим будет.действовать при работе только по одной любой из координат .

Если заданы две координаты X и % и с выхода: интерполятора 1 поступаю сигналы одновременно по двум коорди- натам, то в обоих регистрах 6 и 7 и схемах, связанных с этими координатами., одновременно происходят вышеописанные процессы, но на втором и третьем входах элемента И 18 одновременно присутствуют разрешающие сигналы.

Поэтому каждым выходным сигналом блока 2 задания скорости элемент И 18 будет открываться и его выходной сигнал через элемент НЕ 24 будет закрывать элемент И 12 и устанавливать триггер 4 в положение S, а его выходной сигнал установит в делителе 3 коэффициент деления 7, т.е. через элемент И 18 осуществляется анализ следующего шага - одна или две координаты. Переключение делителя 3 происходит по сигналу блока 2 задания скорости перед вы- да;чвй следзпощего очередного измененного (одна или две координаты) по отношению к предыдущему шагу по координатам.

Рассмотрим работу устройства с произвольной выдачей сигналов с хода интерполятора 1, но синхронно с высокой тактовой частотой, на ко- . торой работает интерполятор 1 фиг. 2-з). При поочередном поступлении сигналов, например сначала по координате X, сигнал будет запи- сан в первый разряд регистра 6. Следуюш сй сигнал по коорда€нате Z бу- дет записан в первый разряд регист-

183684

ра 7, Это значит, произошло совмещение сигналов по координатам. На первом и втором входах элемента И 1 7 будут присутствовать сиг-

5 налы с выходов первых разрядов регистров (5 и 7.

Следующий сигнал по координате X через элемент ИЛИ 9 и элемент И 17 произведет сдвиг в обоих регист-

10 pax 6 и 7. В результате на обоих выходах регнстра 6 и на выходе вто рого разряда регистра 7 будут запи-- саны сигналы, которые окажутся на входах элементов И 13 и И 15. Сле15 дующий сигнал с выхода интерполятора по координате Z произведет сдвиг в обоих регистрах 6 и 7 через эле- . мент ИЛИ 9 и элементы И 13 и И 15. В результате в регистре 7 информа

20 ция будет только во втором разряде, а в регистре 7 - только в первом разряде. Следующий импульс по координате X сдвинет информацию толь- Кб в регистре 6. Следовательно, в

25 первых разрядах обоих регистров 6 и 7 будет присутствовать информация, т.е. опять произойдет совмещение сигналов по координатам.

.В дальнейшем прн любой последова-

30 тельности поступления снгналов по координатам будет пронсходить совмещение и сдвиг информации и обоих регистрах 6 и 7 аналогично описанному (регистры типа ИР1).

Для пояснения работы делителя 3 на фиг. 3 приведена его принципиальная схема. Делитель содержит двог йчный счетчик 25 типа ИЕ5, элемрн- ты И 26-28, элемент ИЛИ 29. Вход- ные тактовые импульсы поступают на ,счетный вход В счетчика 25 и на пер- вый вход элемента И 26.

Сброс счетчика 25 в нулевое положение осуществляется через эле-

45 мент И 27, первый, второй и третий входы которого подключены к выходам соответственно первого, второго и третьего разряда счетчика 25, причем второй разряд счетчика подсоединен

50 к элементу И 27 через последовательно .соединенные элементы И 28 и ИЛИ 29 Второй вход элемента И 26 подключен к третьему разряду счетчика 25, а третий вход - к выходу элемента

554 ИЛИ 29. Если на втором входе элемента ИЛИ 29 имеется положительный- сигнал, то сигналы второго разряда счетчика 25 будут передаваться иа

35

элементы И 26, 27. После шестого тактового импульса на втором и тре- тьем входах элементов И 26, 27 будут положительные сигналы. Седьмой тактовый импульс появится на выходе элемента И 26 и по заднему фронту счетчик 25 переключится в положение соответствующее коду 7, т.е. на всех трех выходах счетчика будут положительные сигналы. Элемент И 27 откроется и сбросит счетчик 25 в исходное нулевое состояние.

Если на втором входе элемента ИЛИ 29 имеется нулевой сигнал, то на третьих входах элементов И 26, 27 будет всегда положительный сигнал, что соответствует коду 2. Значит выходной сигнал элемента И 26 и сброс счетчика через элемент И 27 осуществляется пятым тактовым импульсом.

Формула изобретения Устройство для программного управления, содержащее блок задания скорости, интерполятор, первый и второй выходы которого соединены с входами первого элемента ИЛИ, первый элемент задержки, первый элемент И и первый RS-триггер, о т л и ч а ю щ е е с я тем, что, с целью повышения точности устройства, в него введены первый и второй сдвиговые регистры, второй элемент задержки, параллельный регистр, второй, третий, четвертый, пятый и шестой элементы И, второй элемент ИЛИ и последовательно соединенные седьмой элемент И, третий элемент ИЛИ и восьмой элемент И, выход которого соединен с первым входом первого RS-триггера, а также последовательно соединенные девятый,элемент И, элемент НЕ, десятый элемент И, второй. RS-триггер и делитель частоты с переменным коэффициентом деления, выход которого соединен с первым входом блока задания скорости, подключенного вькодом к вторым входам первого RS-триггера и десятого элемента И, к первому входу параллелького регистра, к первым входам второго, третьего и девятого элементов И, второй вход последнего со- 5 единен с первым выходом первого сдвигового регистра, с первым входом параллельного регистра и с первым входом четвертого элемента И, третий вход девятого элемента И под- 10 ключен к второму входу параллельно- го регистра, к первому выходу второго сдвигового регистра и к первому входу пятого элемента И, второй вход которого соединен с выходом 15 первого элемента ИЛИ, с первым входом седьмого элемента И и с вторым входом четвертого элемента И, в ыход которого через третий элемент ИЛИ подключен к первому входу; первого 20 сдвигового регистра, второй вход которого через второй элемент задержки соединен с первым выходом интерполятора и с третьим входом третье-

го элемента ИЛИ, выход первого эле25 мента И соединен с третьим входом первого RS-триггера, выход которого через шестой элемент И подключен к первому входу интерполятора, второй выход которого через первый эле-

30 мент задержки подключен к первому входу второго сдвигового регистра, а через второй элемент ИЛИ - к первому входу первого элемента И и к второму входу второго сдвигового 35 регистра, второй выход которогоfco- единен с вторым входом первого и седьмого элементов И, третий вход седьмого элемента И соединен с рым выходом первого сдвигового ре- 40 гистра и с вторым входом восьмого элемента И, второй вход второго RS-триггера соединен с выходом элемента НЕ, вторые входы интерполятора, блока задания скорости, дели- 45 теля частоты с переменным коэффициентом деления и шестого элемента И соединены с соответствующими входами устройства, а выходы второго и третьего элементов И - с соот-

50 ветствующими выходами устройства для программного управления.

LI I II I И М I I I I 1 I I II I N I J I t M M M I

III I f

{

{.:

{:

I I I I I I I I I i fT I /I } i r t /

« I 1 m

TE

x:-,N

Редактор M. Бандура

Заказ 1130/55 Тираж 837 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная,

till I I I I

I I I I

,/lV fT I

CL/ J

j

Упра$/гяющий cusffa от триггера 4- ipt/ff.3

Составитель И. Швец

Техред Л.МикешКорректор Л.ГГатая

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления | 1981 |

|

SU976428A1 |

| Программное задающее устройство | 1981 |

|

SU991376A1 |

| Устройство для программного управления | 1984 |

|

SU1255993A1 |

| Устройство для программного управления | 1985 |

|

SU1290263A1 |

| Устройство для задания программы | 1979 |

|

SU849148A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Устройство для коррекции положения резца на станке с программным управлением | 1981 |

|

SU983651A1 |

| Цифровой интерполятор | 1981 |

|

SU1003022A1 |

| Цифровой интерполятор | 1986 |

|

SU1310778A1 |

| Круговой интерполятор | 1988 |

|

SU1566321A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в системах числового программного управления станками в тех случаях, когда необ- ходимо поддерживать с высокой точностью постоянную контурную скорость. Целью изобретения является повьаие- ние точности устройства за счет поддержания постоянной контурной скорости. Устройство для программного управления содержит интерполятор 1, блок 2 задания скорости, делитель 3 с переменным коэффициентом деления, RS-триггеры 4, 5, сдвиговые регистры 6, 7, параллельный регистр 8, элементы ИЛИ 9-11, элементы И 12-21, элементы задержки 22 и 23, элемент НЕ 24. Поддержание контурной скорости осуществляется за счет снижения в -(, т.е. в 1,4 раза, тактовой частоты перед очерёдным шагом одновременно по двум координатам. Для этого тактовая частота для блока задания скорости увеличена в 5 раз и делится управляемым делителем-при шаге по одной координате на 5, а при Diare по двум координатам на 7. Специальная схема анализирует сигна- лы с выхода интерполятора,1совмещает их для одновременной вьщачи по ко-j ординатам и переключает управляемый делитель. 3 ил. (Л iputt

| Устройство для программного управления скоростью подачи | 1982 |

|

SU1067473A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Электроавтоматика станков | |||

| Спо ; :Собы по готовки программ и интерполяторы для контурных системЧПУ.Сбор- |ник.М.:Машиностроение,1980,с.92-93 | |||

| Там же, с | |||

| Прибор для очистки паром от сажи дымогарных трубок в паровозных котлах | 1913 |

|

SU95A1 |

Авторы

Даты

1986-03-15—Публикация

1984-05-25—Подача