Изобретение относится к приборостроению, в частности к воспроизведению цифровой информации с движущегося носителя магнитной записи, например с магнитной ленты, - и может быть использовано в устройствах накопления информации.

Известно устройство декодирования 1, обеспечивающее декодирование воспроизводимого сигнала цифровой магнитной записи, осуществленной способом узкополосной частотной модуляции.

Известно также устройство декодирования 2 при воспроизведении цифровой маг- нитнойзаписи,содержащее

последовательно соединенные блок воспроизведения и блок преобразования кода.

Кроме того, известен преобразователь кода в устройстве для воспроизведения цифровой информации 3, содержащий регистр сдвига, дешифратор, элементы НЕ, И. формирователь сигнала обратной связи и счетчик импульсов.

Этот преобразователь обеспечивает декодирование цифровой информации только одного из способов группового кодирования.

Цель изобретения - расширение эксплуатационных возможностей устройства декодирования путем универсализации входящего в него преобразователя, обеспечивающего декодирование воспроизводимой цифровой информации, записанной несколькими существенно различными способами записи.

Устройство декодирования при воспроизведении цифровой магнитной записи, содержащее регистр, входную тактовую шину, подключенную к одному входу элемента И. другой вход которого соединен с выходом триггера, первый вход которого подключен к входной информационной шине, счетчик, преобразователь, первые выходы которого соединены с выходной информационной шиной, дополнительную выходную шину, и в котором выход элемента И соединен со

v

ос v, ос

ч

счетным входом счетчика и входом сдвига регистра, соответствующие входы установки Которого подключены к входной информационной шине, вход циклического переноса - к второму выходу преобразователя, третий выход которого соединен с дополнительной выходной шиной и с вторым входом триггера, первый вход которого подключен к входу записи регистра, разрядными выходами соединенного с соответствующими информационными входами преобразователя, а частью этих раз- рядных выходов - с выходной информационной шиной, подключенной k выходам счетчика.

Преобразователь выполнен в виде элемента ИЛИ и элемента И. выходы которых являются соответственно третьим и вторым выходами преобразователя, первым, четвертым, шестым и седьмым входами которого являются соответственно один инвертирующий вход элемента ИЛИ, подключенный к первому инвертирующему входу элемента И, второй, третий и четвертый, подключенный к второму входу элемента ИЛИ, входы элемента И.

Кроме того, преобразователь выполнен в виде трех элементов И-ИЛ И и элемента И, третий вход которого подключен к выходу второго элемента И-ИЛ И, при этом выходы первого элемента И-ИЛ И, элемента И и третьего элемента И-ИЛИ являются соответственно вторым, третьим и первым входами преобразователя, первым, вторым, третьим, пятым, шестым и седьмым входами которого являются соответственно первый инверсный вход первого элемента И-ИЛИ, подключенный к его третьему инверсному входу и первому инверсному входу элемента И, второй инверсный вход первого элемента И-ЙЛИ, подключенный к первому инверсному входу второго элемента И-ИЛИ и третьему входу третьего элемента И-ИЛИ, второй вход элемента-И. третий вход второго элемента И-ИЛИ, подключенный к второму входу третьего элемента И-ИЛИ, четвертый инверсный вход первого элемента И-ЙЛИ, подключенный к второму входу второго элемента И-ИЛИ и к первому входу третьего элемента И-ИЛИ, и пятый вход первого элемента И-ИЛИ, подключенный к четвертому входу элемента И.

И, кроме того, преобразователь выполнен в виде двух элементов И, элемента И- ИЛИ, элемента 2И-ИЛИ и элемента ЗИ-ИЛИ, выход которого подключен к четвертому входу первого элемента И, при этом третий вход первого элемента И, его выход и выходы элемента И-ИЛИ, второго элемента И и элемента 2 И-ИЛ И являются

соответственно вторым, третьим и первым выходами преобразователя, первым, вторым, третьим, четвертым, пятым, шестым и девятым входами которого являются соответственно первый инверсный вход первого элемента И, первый инверсный вход элемента И-ИЛИ, подключенный к первым инверсным входам первого и второго элементов И элемента ЗИ-ИЛИ. Первый

0 вход третьего элемента И элемента ЗИ- ИЛИ, подключенный к второму входу элемента И-ИЛИ, одному входу второго элемента И и первому инверсному входу первого элемента И элемента 2И-ИЛИ, вто5 рой вход первого элемента И, второй вход первого элемента И элемента ЗИ-ИЛИ, подключенный к первому, входу второго элемента И элемента 2И-ИЛИ, второй вход первого элемента И элемента 2И-ИЛИ, вто0 рой вход второго элемента и элемента ЗИ- ИЛИ, подключенный к второму входу третьего элемента И элемента ЗИ-ИЛИ, третьему инверсному входу элемента И-ИЛИ. второму входу второго элемента И,

5 второму инверсному входу первого элемента И элемента 2И-ИЛИ, и третий вход первого элемента И.

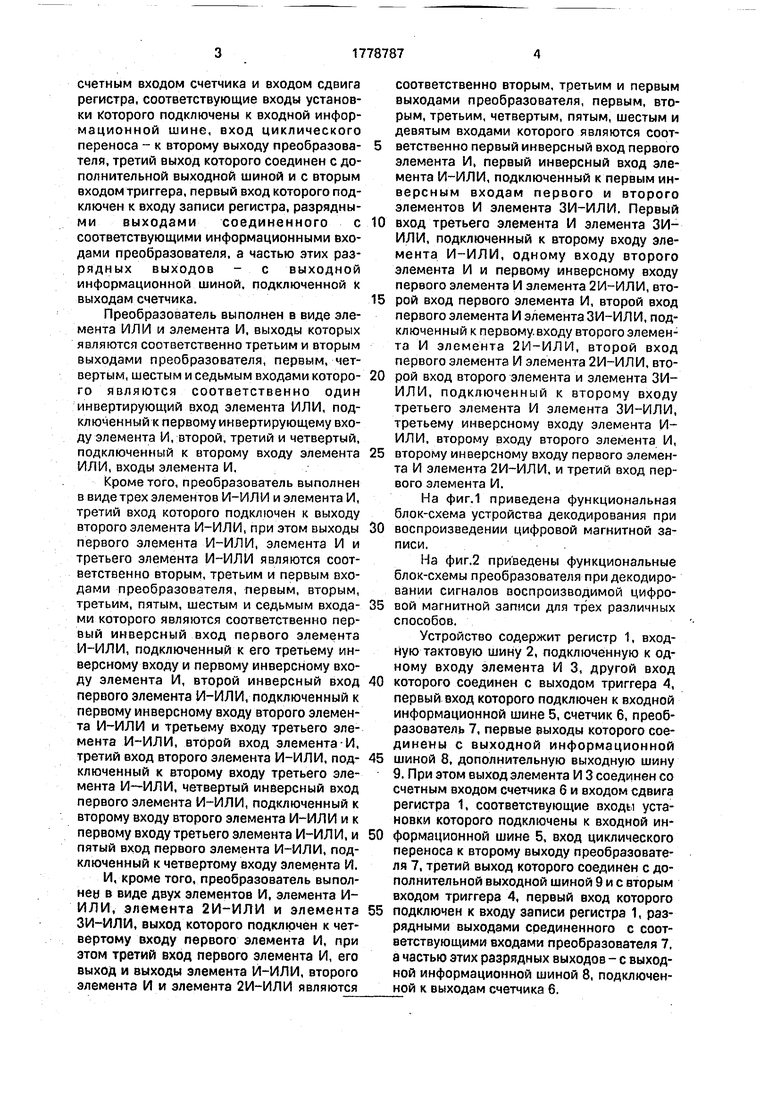

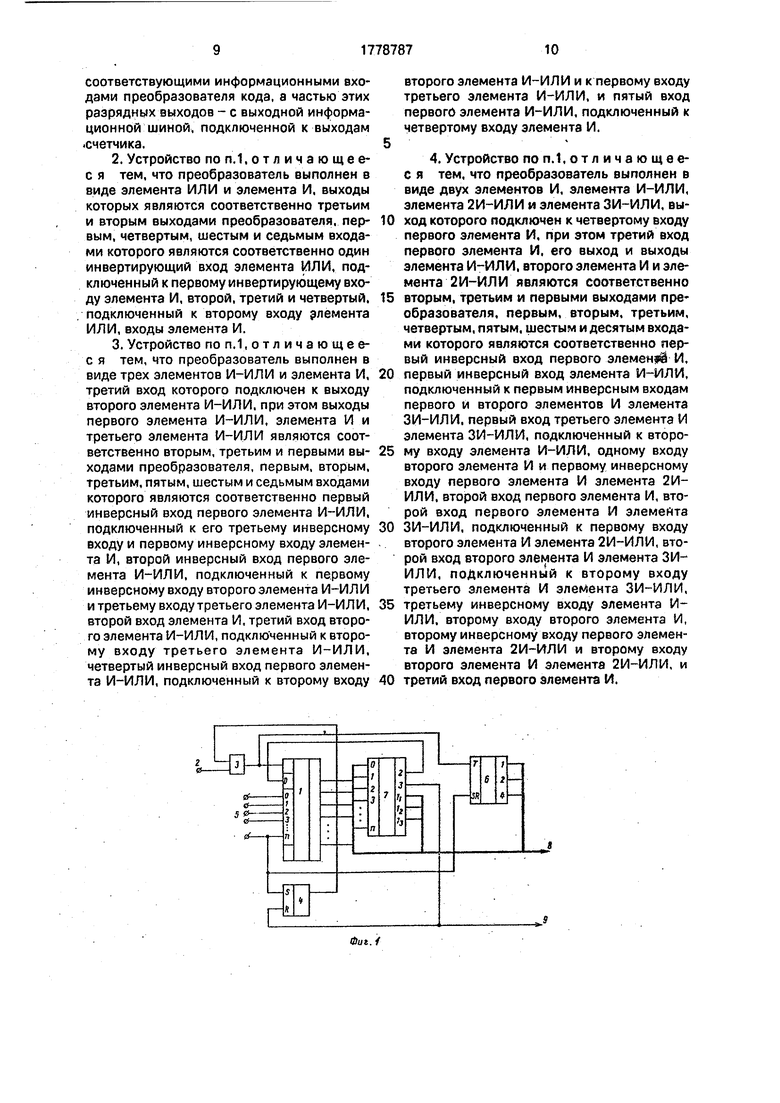

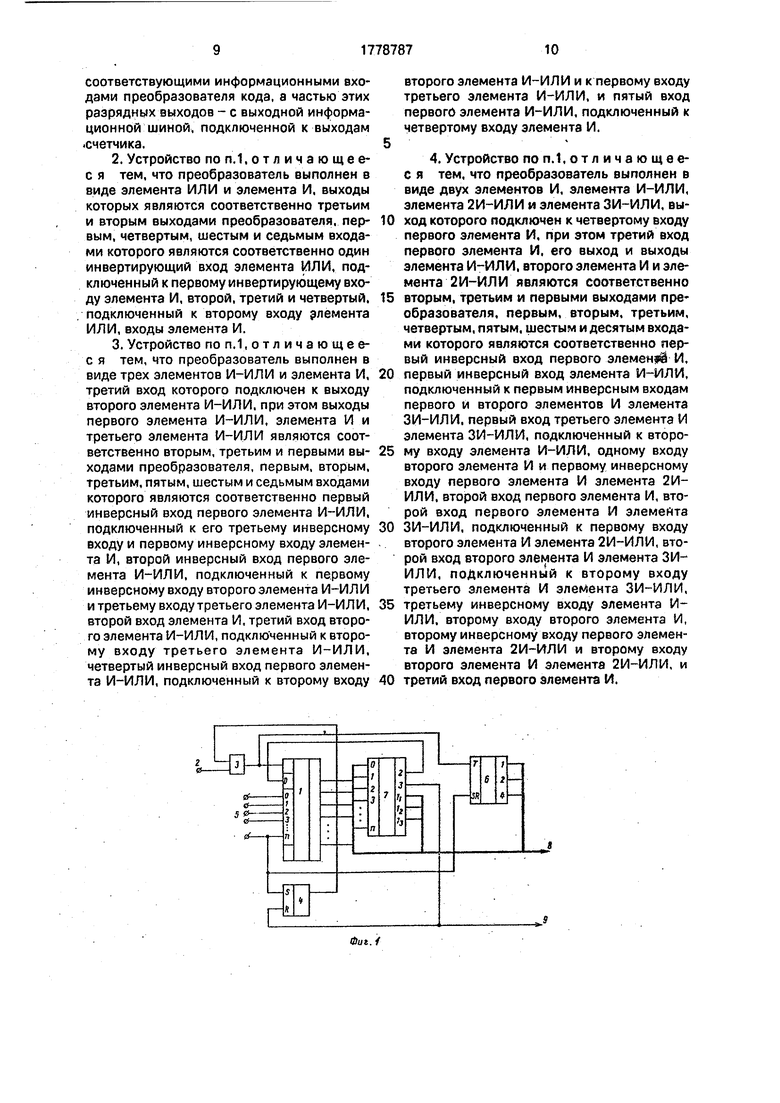

На фиг.1 приведена функциональная блок-схема устройства декодирования при

0 воспроизведении цифровой магнитной записи.

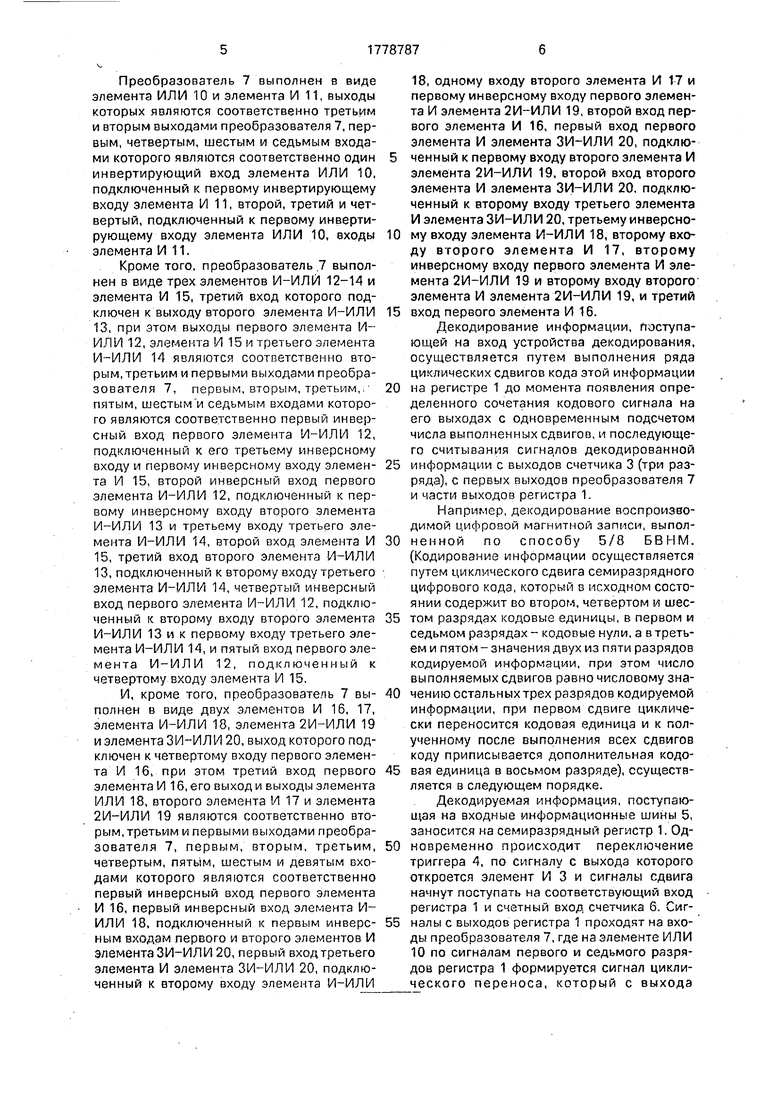

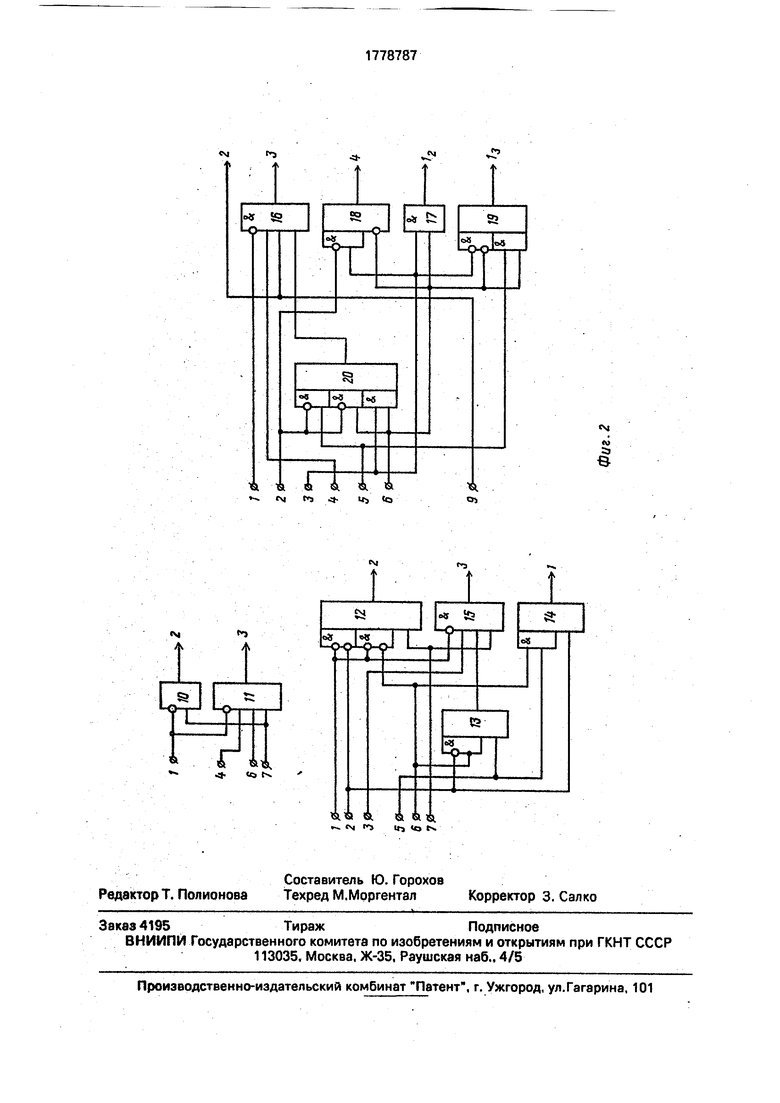

На фиг.2 приведены функциональные блок-схемы преобразователя при декодировании сигналов воспроизводимой цифро5 вой магнитной записи для трех различных способов.

Устройство содержит регистр 1, входную тактовую шину 2, подключенную к одному входу элемента И 3, другой вход

0 которого соединен с выходом триггера 4, первый вход которого подключен к входной информационной шине 5, счетчик 6, преобразователь 7, первые выходы которого сое- динены с выходной информационной

5 шиной 8, дополнительную выходную шину 9. При этом выход элемента И 3 соединен со счетным входом счетчика 6 и входом сдвига регистра 1, соответствующие входы установки которого подключены к входной ин0 формационной шине 5, вход циклического переноса к второму выходу преобразователи 7, третий выход которого соединен с дополнительной выходной шиной 9 и с вторым входом триггера 4, первый вход которого

5 подключен к входу записи регистра 1, разрядными выходами соединенного с соответствующими входами преобразователя 7. а частью этих разрядных выходов - с выходной информационной шиной 8, подключенной к выходам счетчика 6.

Преобразователь 7 выполнен в виде элемента ИЛИ 10 и элемента И 11, выходы которых являются соответственно третьим и вторым выходами преобразователя 7, первым, четвертым, шестым и седьмым входами которого являются соответственно один инвертирующий вход элемента ИЛИ 10, подключенный к первому инвертирующему входу элемента И 11, второй, третий и четвертый, подключенный к первому инвертирующему входу элемента ИЛИ 10, входы элемента И 11.

Кроме того, преобразователь .7 выполнен в виде трех элементов И-ИЛИ 12-14 и элемента И 15, третий вход которого подключен к выходу второго элемента И-ИЛИ 13, при этом выходы первого элемента И-ИЛИ 12, элемента И 15 и третьего элемента И-ИЛИ 14 являются соответственно вторым,третьим и первыми выходами преобразователя 7, первым, вторым, третьим,. пятым, шестым и седьмым входами которого являются соответственно первый инверсный вход первого элемента И-ИЛИ 12, подключенный к его третьему инверсному входу и первому инверсному входу элемента И 15, второй инверсный вход первого элемента И-ИЛИ 12, подключенный к первому инверсному входу второго элемента И-ИЛИ 13 и третьему входу третьего элемента И-ИЛИ 14, второй вход элемента И 15, третий вход второго элемента И-ИЛИ 13, подключенный к второму входу третьего элемента И-ИЛИ 14, четвертый инверсный вход первого элемента И-ИЛИ 12, подключенный к второму входу второго элемента И-ИЛИ 13 и к первому входу третьего элемента И-ИЛИ 14, и пятый вход первого элемента И-ИЛИ 12, подключенный к четвертому входу элемента И 15.

И, кроме того, преобразователь 7 выполнен в виде двух элементов И 16, 17, элемента И-ИЛИ 18, элемента 2И-ИЛИ 19 и элемента ЗИ-ИЛ И 20, выход которого подключен к четвертому входу первого элемента И 16, при этом третий вход первого элемента И 16, его выход и выходы элемента ИЛИ 18, второго элемента И 17 и элемента 2И-ИЛИ 19 являются соответственно вторым, третьим и первыми выходами преобразователя 7, первым, вторым, третьим, четвертым, пятым, шестым и девятым входами которого являются соответственно первый инверсный вход первого элемента И 16, первый инверсный вход элемента И- ИЛИ 18, подключенный к первым инверсным входам первого и второго элементов И элемента ЗИ-ИЛИ 20, первый вход третьего элемента И элемента ЗИ-ИЛИ 20, подключенный к второму входу элемента И-ИЛИ

18, одному входу второго элемента И 17 и первому инверсному входу первого элемента И элемента 2И-ИЛИ 19, второй вход первого элемента И 16, первый вход первого элемента И элемента ЗИ-ИЛИ 20, подклю- ченный к первому входу второго элемента И элемента 2И-ИЛИ 19. второй вход второго элемента И элемента ЗИ-ИЛИ 20. подключенный к второму входу третьего элемента И элемента ЗИ-ИЛИ 20, третьему инверсно0 му входу элемента И-ИЛИ 18, второму входу второго элемента И 17, второму инверсному входу первого элемента И элемента 2И-ИЛИ 19 и второму входу второго элемента И элемента 2И-ИЛИ 19, и третий

5 вход первого элемента И 16.

Декодирование информации, поступающей на вход устройства декодирования, осуществляется путем выполнения ряда циклических сдвигов кода этой информации

0 на регистре 1 до момента появления определенного сочетания кодового сигнала на его выходах с одновременным подсчетом числа выполненных сдвигов, и последующего считывания сигналов декодированной

5 информации с выходов счетчика 3 (три разряда), с первых выходов преобразователя 7 и части выходов регистра 1.

Например, декодирование воспроизводимой цифровой магнитной записи, выпол0 ненной по способу 5/8 БВНМ. (Кодирование информации осуществляется путем циклического сдвига семиразрядного цифрового кода, который в исходном состоянии содержит во втором, четвертом м шес5 том разрядах кодовые единицы, в первом и седьмом разрядах - кодовые нули, а в третьем и пятом - значения двух из пяти разрядов кодируемой информации, при этом число выполняемых сдвигов равно числовому зна0 чению остальных трех разрядов кодируемой информации, при первом сдвиге циклически переносится кодовая единица и к полученному после выполнения всех сдвигов коду приписывается дополнительная кодо5 вая единица в восьмом разряде), осуществляется в следующем порядке.

Декодируемая информация, поступающая на входные информационные шины 5, заносится на семиразрядный регистр 1. Од0 новременно происходит переключение триггера 4, по сигналу с выхода которого откроется элемент И 3 и сигналы сдвига начнут поступать на соответствующий вход регистра 1 и счетный вход счетчика 6. Сиг5 налы с выходов регистра 1 проходят на входы преобразователя 7, где на элементе ИЛИ 10 по сигналам первого и седьмого разрядов регистра 1 формируется сигнал циклического переноса, который с выхода

преобразователя 7 поступает на вход регистра, 1. Циклический сдвиг будет происходить до момента возникновения на первом, четвертом, шестом и седьмом разрядных местах сигналов, соответствующих кодовой комбинации 0111. При появлении этой комбинации на выходе элемента И 11 формируется сигнал, по которому триггер 4 возвращается в исходное состояние, запрещая дальнейший сдвиг кода информации на регистре 1. Посту пая также на выход устройства декодирования, сигнал с третьего выхода преобразователя 7 будет свидетельствовать о завершении цикла декодирования. При этом сигналы с инверсных выходов счетчика 6 будут соответствовать трем первым разрядам декодируемой информации, а сигналы с выходов третьего и пятого разрядов регистра 1 - двум остальным разрядам декодируемой информации.

Декодирование информации, записанной способами 6/8 БВНМ и 8/10 БВНМ, осуществляется в основном аналогично случаю декодирования информации, записанной способом 5/8 БВНМ. (Кодирование информации по способу 6/8 БВНМ также осуществляется циклическим сдвигом семиразрядного цифрового кода, в исходном состоянии который на первом и седьмом разрядных местах содержит кодовые нули, на третьем - кодовую единицу, на четвертом и шестом - кодовые значения четвертого и пятого разрядов кодируемой информации и на пятом - логическую сумму сигналов шестого и инверсии пятого разрядов кодируемой информации и на втором месте - логическое произведение этих же сигналов. При этом число выполняемых сдвигов также равно числовому значению первых трех разрядов кодируемой информации, при первом сдвиге циклически переносится кодовая единица и к полученному после выполнения всех сдвигов коду приписывается дополнительная кодовая единица в восьмом разряде. При кодировании поспособу8/10 БВНМ циклическим сдвигам подвергается девяти- . разрядный код, в котором в исходном состоянии на втором и шестом разрядных местах содержатся кодовые единицы, на третьем - кодовый ноль, на первом и девятом - соответственно значения четвертого и пятого разрядов кодируемой информации, а на четвертом, пятом, седьмом и восьмом - кодовые значения, определяемые логическими функциями от значений разрядов кодируемой информации соответственно: ае aeae v аеат v as; as v а. При этом число сдвигов no-прежнему равно числовому значению трех разрядов кодируемой информации, а к полученному после выполнения всех сдвигов коду приписывается дополнительная кодовая единица в десятом разряде. Отличия при декодировании

информации, записанной способами 6/8 БВНМ и 8/10 БВНМ, в сравнении с процессом декодирования информации, записанной способом 5/8 БВНМ, сводятся к следующему.

0 При декодировании информации, записанной способом 6/8 БВНМ, сигнал циклического переноса формируется на выходе элемента 2И-ИЛИ 12 из сигналов с выходов второго, шестого и седьмого разрядов реги5 стра 1, а завершается преобразование по сигналу с выхода элемента l/l 15. Декодирование информации при этом образуется тремя инверсными сигналами с выходов счетчика 6, сигналами с выходов четвертого

0 и шестого разрядов регистра 1 и сигналом с выхода третьего элемента Й-ИЛИ 14 преобразователя 7.

При декодировании информации, записанной способом 8/10 БВНМ, сигнал цикли5 ческого переноса образуется прямой трансляцией сигнала девятого разряда регистра 1. преобразование завершается по сигналу с выхода элемента И 16 преобразователя 7. Декодированная информация об0 разуется тремя инверсными сигналами с выходов счетчика 6, сигналами с выходов седьмого и восьмого разрядов регистра 1 и сигналами с первых выходов преобразователя 7, формируемых элементом И-ИЛИ 18,

5 элементом И 17 и элементом 2И-ИЛИ 19. Формула изобретения 1. Устройство декодирования при воспроизведении цифровой магнитной записи, содержащее регистр, входную тактовую ши0 ну, подключенную к одному входу элемента И, другой вход которого соединен с выходом триггера, первый вход которого подключен к входной информационной шине, счетчик, преобразователь, первые выходы которого

5 соединены с выходной информационной шиной, дополнительную выходную шину, отличающееся тем, что, с целью расширения эксплуатационных возможностей при различных способах магнитной за0 писи, выход элемента И соединен со счетным входом счетчика и входом сдвига регистра, соответствующие входы установки которого подключены к входной информационной шине, вход циклического

5 переноса - к второму выходу преобразователя, третий выход которого соединен с дополнительной выходной шиной и с вторым входом триггера, первый вход которого подключен к входу записи регистра, разрядными выходами соединенного с

соответствующими информационными входами преобразователя кода, а частью этих разрядных выходов - с выходной информационной шиной, подключенной к выходам счетчика.

2.Устройство поп.1,отличающее- с я тем, что преобразователь выполнен в виде элемента ИЛИ и элемента И, выходы которых являются соответственно третьим

и вторым выходами преобразователя, пер- вым, четвертым, шестым и седьмым входами которого являются соответственно один инвертирующий вход элемента ИЛИ, подключенный к первому инвертирующему входу элемента И, второй, третий и четвертый, подключенный к второму входу элемента ИЛИ, входы элемента И.

3.Устройство поп.1,отличающее- с я тем, что преобразователь выполнен в виде трех элементов И-ИЛИ и элемента И, третий вход которого подключен к выходу второго элемента И-ИЛИ. при этом выходы первого элемента И-ИЛИ, элемента И и третьего элемента И-ИЛИ являются соответственно вторым, третьим и первыми вы- ходами преобразователя, первым, вторым, третьим, пятым, шестым и седьмым входами которого являются соответственно первый инверсный вход первого элемента И-ИЛИ, подключенный к его третьему инверсному входу и первому инверсному входу элемента И, второй инверсный вход первого элемента И-ИЛИ, подключенный к первому инверсному входу второго элемента И-ИЛИ

и третьему входу третьего элемента И-ИЛИ, второй вход элемента И, третий вход второго элемента И-ИЛИ, подключенный к второму входу третьего элемента И-ИЛИ, четвертый инверсный вход первого элемента И-ИЛИ, подключенный к второму входу

второго элемента И-ИЛИ и к первому входу третьего элемента И-ИЛИ, и пятый вход первого элемента И-ИЛИ, подключенный к четвертому входу элемента И.

4. Устройство поп.1,отличающее- с я тем, что преобразователь выполнен в виде двух элементов И, элемента И-ИЛИ, элемента 2И-ИЛИ и элемента ЗИ-ИЛИ, выход которого подключен к четвертому входу первого элемента И, при этом третий вход первого элемента И, его выход и выходы элемента И-ИЛИ, второго элемента И и элемента 2И-ИЛИ являются соответственно вторым, третьим и первыми выходами преобразователя, первым, вторым, третьим, четвертым, пятым, шестым и десятым входами которого являются соответственно первый инверсный вход первого элемент И, первый инверсный вход элемента И-ИЛИ, подключенный к первым инверсным входам первого и второго элементов И элемента ЗИ-ИЛИ. первый вход третьего элемента И элемента ЗИ-ИЛИ, подключенный к второму входу элемента И-ИЛИ, одному входу второго элемента И и первому инверсному входу первого элемента И элемента 2И- ИЛИ. второй вход первого элемента И, второй вход первого элемента И элемента ЗИ-ИЛИ, подключенный к первому входу второго элемента И элемента 2И-ИЛИ, второй вход второго элемента И элемента ЗИ- ИЛИ, подключенный к второму входу третьего элемента И элемента ЗИ-ИЛИ, третьему инверсному входу элемента И-ИЛИ. второму входу второго элемента И, второму инверсному входу первого элемента И элемента 2И-ИЛИ и второму входу второго элемента И элемента 2И-ИЛИ, и третий вход первого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Мажоритарное декодирующее устройство | 1986 |

|

SU1372627A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1163322A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1246091A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1800481A1 |

| Устройство для записи цифровой информации | 1989 |

|

SU1607008A1 |

| Устройство для симметрирования токов трехфазных сетей | 1988 |

|

SU1686600A1 |

| Матричный мультиплексор-демультиплексор | 1988 |

|

SU1656559A1 |

| Генератор концентрических окружностей для телевизионного индикатора | 1983 |

|

SU1124373A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

Изобретение относится к приборостроению, в частности к устройствам декодирования цифровой информации, воспроизводимой с движущегося магнитного носителя, и может быть использовано в накопителях на магнитной ленте. Целью изобретения является расширение эксплуатационных возможностей декодера при раз- личных способах магнитной записи. Устройство содержит регистр сдвига, счетчик импульсов сдвига, элемент И и преобразователь. 3 з.п. ф-лы, 2 ил.

1

fsi ц-j «о f

Составитель Ю. Горохов Редактор Т. Полионова Техред М.МоргенталКорректор 3. Салко

Заказ 4195ТиражПодписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва. Ж-35, Раушская наб., 4/5

сч

ъ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| и др | |||

| Накопители информации с подвижным носителем | |||

| Л.: Энергоиздат, 1982, с.43-47 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| ЭВТ, 1971,вып.Ю, с.30-46 | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-11-30—Публикация

1990-11-14—Подача