сравнения, RS-триггер, элемент И и шинный формирователь, причем первый и второй входы схемы сравнения соединены с первой и второй информационной шинами ячейки, вход сброса ячейки соединен с R-входом 5 RS-триггерэ, первый вход элемента И соединены с настроечным входом ячейки, вы- ход Не равно схемы сравнения соединен с S-входом RS-триггера, тактовый вход которого соединен с входом синхронизации ю ячейки, вход задания направления ячейки соединен с первым управляющим входом шинного формирователя, второй управляющий вход которого соединен с выходом элемента И, второй вход которого соединен с 15 инверсным выходом RS-триггера, первая информационная шина ячейки соединена с информационными входами шинного формирователя, выходы которого соединены с второй информационной шиной ячейки. 20

Недостатками данного устройства являются ограниченные функциональные возможности, так как оно не может быть использовано для связи между процессорными элементами одной группы в матрич- 25 ном коммутаторе.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения четырехмаправленной коммутации данных. .30

Поставленная цель достигается тем, что ячейка матричного коммутатора, содержащая первый шинный формирователь, первую схему сравнения и первый элемент И, выход которого соединен с входом выборки 35 первого шинного формирователя, первый и второй двунаправленные входы которого соединены соответственно с первой и второй шинами данных, причем первый и второй входы первой схемы сравнения Q соединены соответственно с первой и вто-° рой шинами данных ячейки, дополнительно содержит два шифратора, регистр, со второ- го по четвертый шинные формирователи, с второй по шестую схемы сравнения и с вто- 4с рого по четвертый элементы И, выход К-го элемента И (К 2, 3, 4) соединен .с входом выборки К-го шинного формировате ля, вход выбора направления которого и вход выбора направления первого шинного формиро- вателя соединены с выходами младших разрядов регистра, выходы старших разря- дов которого соединены с первыми входами элементов И с первого по четвертый, вторые входы которых соединены с настроечными входами ячейки, тактовый вход которой соединен с тактовым входом регистра, входы старших разрядов которого соединены с выходами первого шифратора, входы которого соединены с выходами схем сравнения с

55

5 0

5

0

5 Q с

5

первой по шестую, входы младших разрядов регистра соединены с выходами второго шифратора, входы которого соединены с шинами данных ячейки, первая шина данных которой соединена с первыми входами второй и третьей схем сравнения, вторая шина данных ячейки соединена с первыми входами четвертой и пятой схем сравнения, первый вход шестой схемы сравнения соединен с вторыми входами второй и четвертой схем сравнения и третьей шиной данных ячейки, четвертая шина данных которой соединена с вторыми входами третьей, пятой и шестой схем сравнения, первый двунаправленный вход второго шинного формирователя соединен с первой шиной данных ячейки, третья шина данных которой соединена с первыми двунаправленными входами третьего и четвертого шинных формирователей, вторые двунаправленные входы второго и третьего шинных формирователей соединены с четвертой шиной данных ячейки, вторая шина данных которой соединена с вторым двунаправленным входом четвертого шинного формирователя.

Благодаря введению дополнительно трех шинных формирователей, пяти схем сравнения, двух шифраторов, регистра и со- .ответствующих связей между элементами коммутирующей ячейки, а также благодаря изменению способа настройки обеспечивается настройка коммутации четырех информационных шин по символическим именам непосредственно одной ячейкой, а не четырьмя коммутирующими ячейками по прототипу. Значительно расширены функциональные возможности ячейки. Коммутационное поле, построенное на таких коммутирующих ячейках, позволяет связывать элементы одной группы (для создания подобных связей ячейкой-прототипом необходимо построение коммутирующего узла из более чем четырех коммутирующих элементов, при этом значительно возрастают аппаратурные затраты).

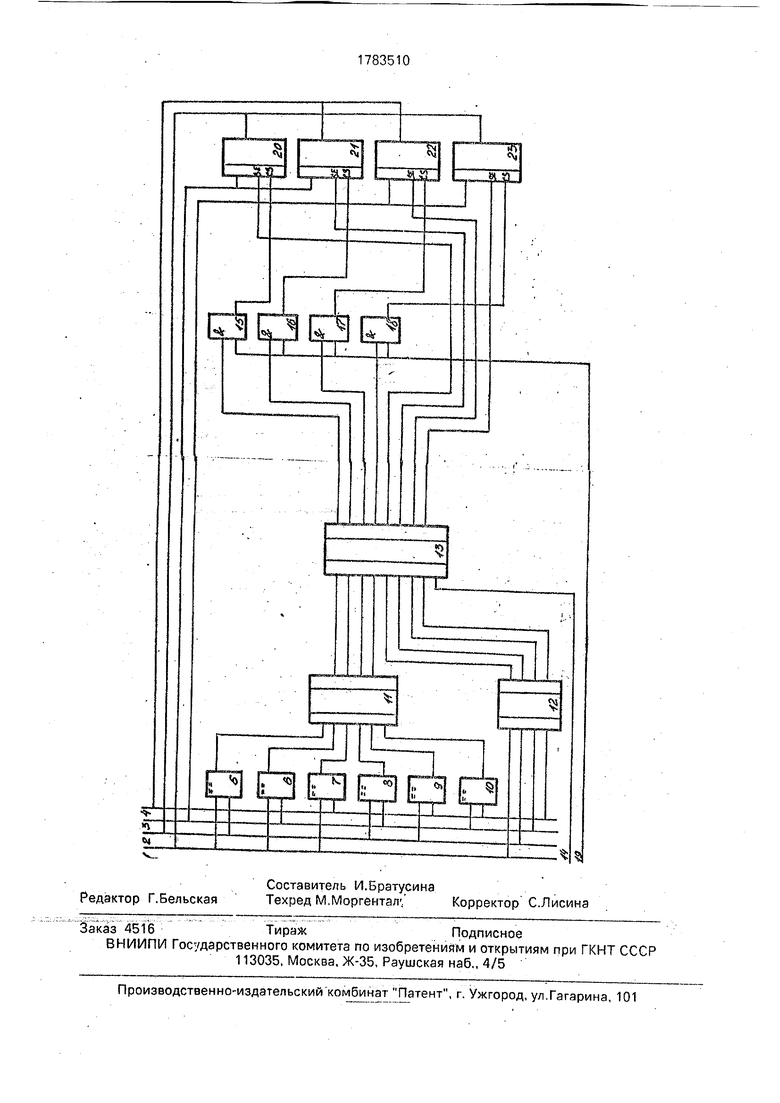

На чертеже дана структурная схема предлагаемой ячейки.

Ячейка матричного коммутатора содержит четыре шины 1-4, шесть схем сравнения 5-10, два шифратора 11 и 12. регистр 13, четыре элемента И 15-18, четыре шинных формирователя 20-23, причем выход 1-го элемента И (i 15, 16, 17, 18) соединен с входом выборки j-ro шинного формирователя (j 20, 21, 22, 23) соответственно, вход выбора направления которого соединен с выходами младших разрядов регистра 13, выход старших разрядов которого соединены с первыми входами.элементов И с 15-го по 18-й, вторые входы которых соединены с

настроечным входом 19 ячейки, тактовый вход 14 которой соединен с тактовым входом регистра 13, входы старших разрядов которого соединены с выходами шифратора 11, входы которого соединены с выходами схем сравнения с 5-й по 10-ю, входы младших разрядов регистра 13 соединены с выходами шифратора 12, входы которого соединены с шинами 1-4 данных ячейки, шина 1 данных которой соединена с первыми входами схем 5-7 сравнения, шина 2 данных ячейки соединена с первыми входами схем 8 и 9 сравнения и вторым входом схемы 5 сравнения, первый вход схемы 10 сравнения соединен с вторыми входами схем 6 и 8 сравнения и шиной 3 данных ячейки, шина 4 данных которой соединена с вторыми входами схем 7, 9 и 10 сравнения, первые двунаправленные входы шинных формирователей 20 и 21 подключены к шине 1 данных, первые-двунаправленные входы шинных формирователей 22 и 23 подключены к шине 3 данных ячейки, шина 2 данных которой соединена с вторыми двунаправленными входами шинных формирователей 20, 23, а шина 4 данных ячейки соединена с вторыми двунаправленными входами шинных формирователей 21, 22.

Ячейка матричного коммутатора работает следующим образом. В начале настройке схемы нулевой потенциал, подаваемый на настроечный вход 19, устанавливает элементы И 15-18 в нулевое состояние, при этом нулевой сигнал снимается с их выходов и поступает на входы выборки шинных формирователей 20- 23, переводя их в состояние высокого импеданса и обеспечивая разрыв связей между шинами данных 1, 2 и 3. 4.

Процесс настройки схемы заключается в следующем. Коды, несущие информацию

0символических именах коммутируемых каналов связи, поступают по шинам данных

1-4. причем старшие (п-1) разрядов поступают на схемы сравнения 5-10, их попарное совпадение на схемах сравнения определяет канал передачи информации, младший разряд каждого кода несет информацию о режиме работы данного канала связи (прием или передача информации). Сигналы с выходов схем сравнения кодов 5-10 поступают в качестве адреса на адресные входы шифратора 11, а младшие разряды символических имен поступают в виде адреса на адресные входы шифратора 12.

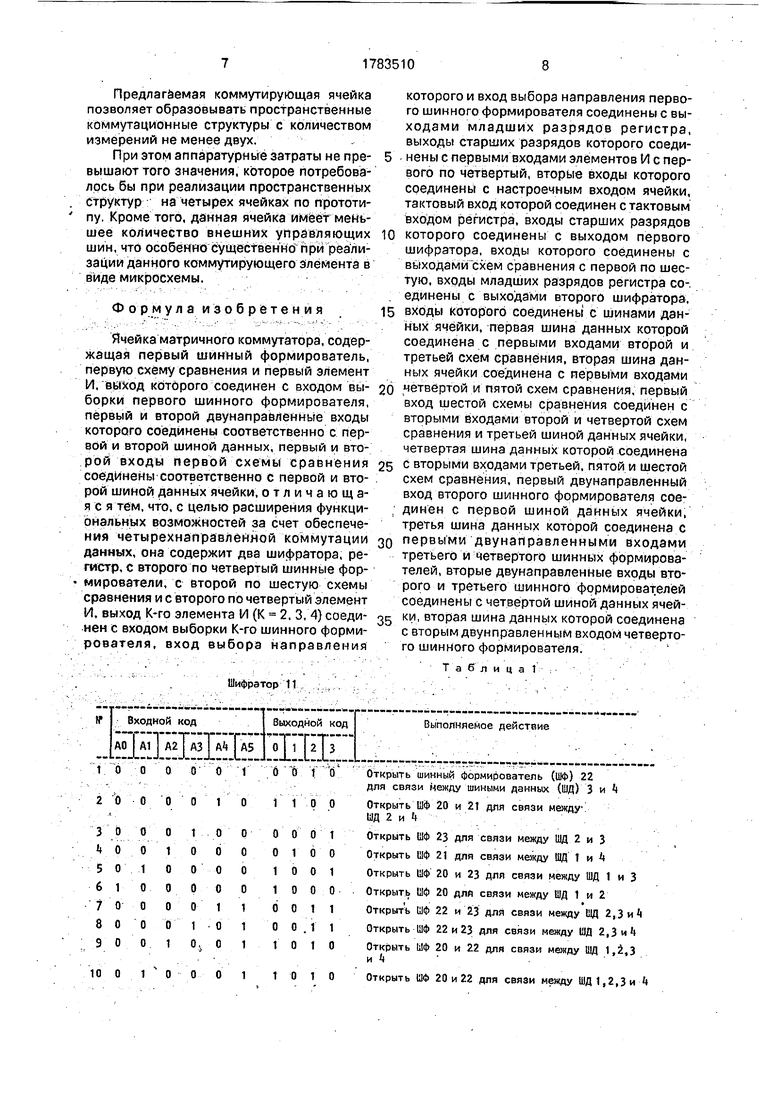

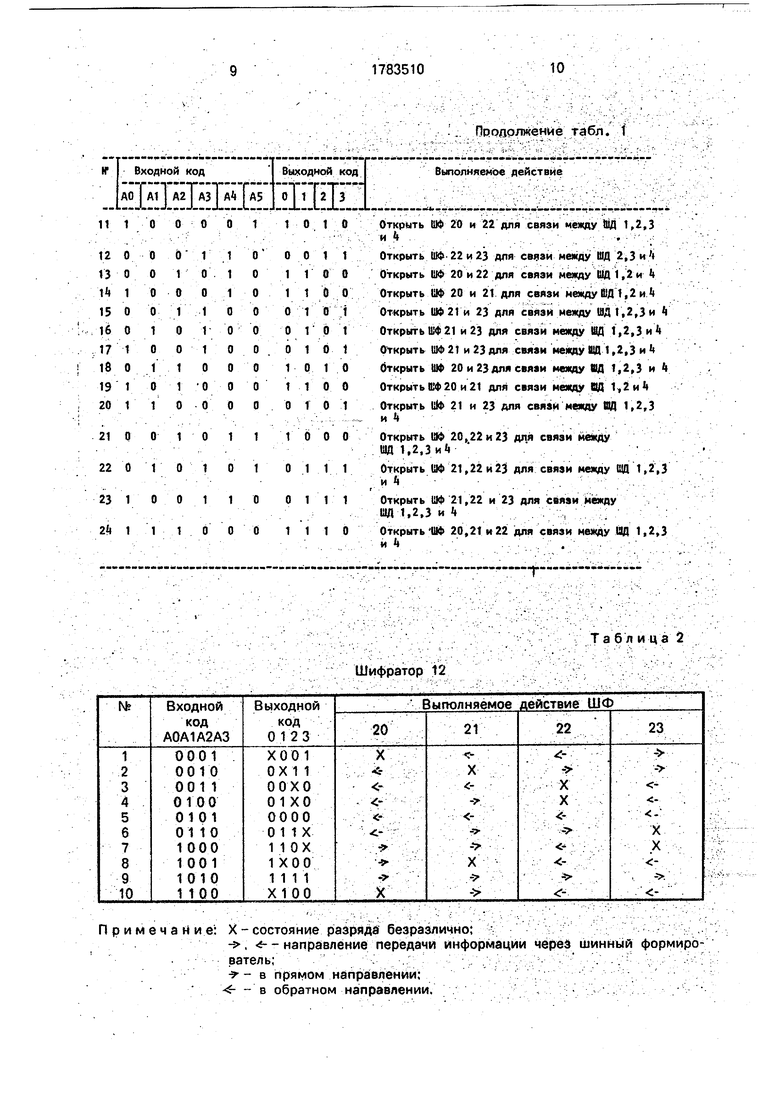

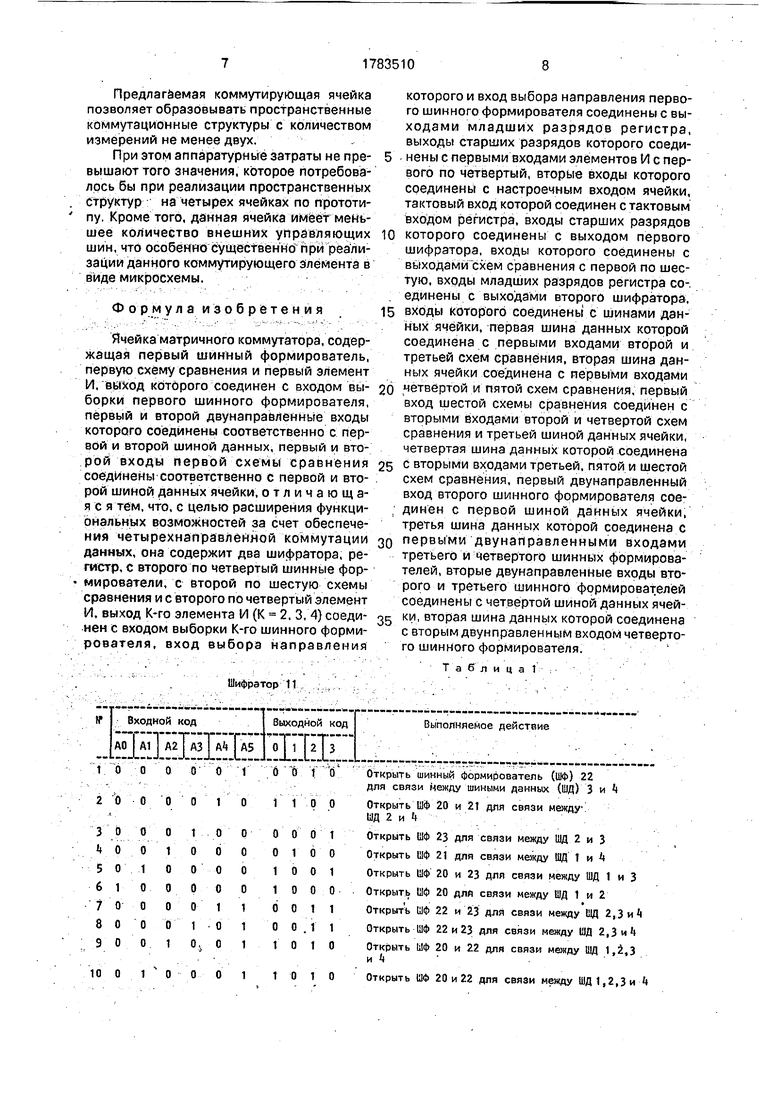

В табл. 1. 2 приведены правила преобразования кода для шифратора 11 и 12 соответственно. Причем заранее предполагается, что конфликтные ситуации исключены

Выходные сигналы шифраторы 11 и 12 поступают на информационные входы регистра 13 и записываются в него синхросигналом с шины 14 синхронизации, тем самым 5 заканчивается режим настройки и сигнал настройки снимается с шины 19.

Теперь по шине 19 настройки высокий потенциал, который поступает на вторые

0 входы элементов 15-18 И. и «а их выходах повторяются сигналы с первых четырех выходов регистра 13. В соответствии со значениями этих сигналов включится соответствующий шинный формирователь,

5 а значения сигналов с вторых выходов регистра 13 определяет направление передачи информации.

Пусть необходимо обеспечить передачу информации из шины 1 в шину 2 Тогда

0 совпадение старших (п-1) разрядов символических имен, поступающих н т схему сравнения 5 с шин 1 и 2, даст на выходе этой схемы единичный сигнал. На адресные входы шифратора 11 поступит код, располо5 женный в шестой строке табл. 1 (100000). Соответствующий ему выходной код 1000 определит включение шинного формирователя 20. Младший разряд передающего канала равен единице.(в данном случае -Шина

Q 1). Искомый код находят в седьмой строке табл. 2 В соответствии с этим кодом на вход задания направления шинного формирователя 20 поступит единичный сигнал, что определит его включение в прямом

5 направлении и передачу информации из шины 1 в шину 2.

Предлагаемая ячейка матричного коммутатора может быть выполнена с использованием элементов различных серий Так,

Q- например, в качестве схемы сравнения кодов могут быть использованы микросхемы К555СН1 и К531СП1, которые позволяют строить схемы сравнения с разрядностью, кратной четырем. В качестве регистра МО- C жет быть использована микросхема К555ИР23. Элементы И могут быть элементами микросхемы К155ДЕ1. Шинные формирователи (другое название этих элементов - магистральные усилители) ис

пользуются для отключения или подключения источников и приемников информации к шинам, так как их информационные выходы имеют три устойчивых состояния Для управления работой микросхемы К580ВА86 имеются два входа: вход, который управляет выборкой кристалла, и вход, который определяет направление передачи информации. Первый и второй преобразователи могут быть реализованы на микросхемах постоянных запоминающих устройств К556РТ4.

Предлагаемая коммутирующая ячейка позволяет образовывать пространственные коммутационные структуры с количеством измерений не менее двух.

При этом аппаратурные затраты не пре- 5 вышают того значения, которое потребовалось бы при реализации пространственных структур на четырех ячейках по прототипу. Кроме того, данная ячейка имеет меньшее количество внешних управляющих 10 шин, что особенно существенно при реализации данного коммутирующего элемента в виде микросхемы.

Формулаизобретения15

Ячейка матричного коммутатора, содержащая первый шинный формирователь, первую схему сравнения и первый элемент И, выход которого соединен с входом вы- 20 борки первого шинного формирователя, первый и второй двунапраёленные входы которого соединены соответственно с первой и второй шиной данных, первый и второй входы первой схемы сравнения 25 соединены соответственно с первой и второй шиной данных ячейки, отличающаяся тем, что, с целью расширения функциональных возможностей за счет обеспечения четырехнаправленяой коммутации зо данных, она содержит два шифратора, регистр, с второго по четвертый шинные фор- мирователи, с второй по шестую схемы сравнения и с второго по четвертый элемент И, выход К-го элемента И (К 2. 3, 4} соеди- 35 нен с входом выборки К-го шинного формирователя, вход выбора направления

Шифратор 11

которого и вход выбора направления первого шинного формирователя соединены с выходами младших разрядов регистра, выходы старших разрядов которого соединены с первыми входами элементов И с первого по четвертый, вторые входы которого соединены с настроечным входом ячейки, тактовый вход которой соединен с тактовым входом регистра, входы старших разрядоЕ которого соединены с выходом первого шифратора, входы которого соединены с выходами схем сравнения с первой по шестую, входы младших разрядов регистра соединены с выходами второго шифратора, входы которого соединены с шинами данных ячейки, первая шина данных которой соединена с первыми входами второй и третьей схем сравнения, вторая шина данных ячейки соединена с первыми входами четвертой и пятой схем сравнения, первый вход шестой схемы сравнения соединен с вторыми входами второй и четвертой схем сравнения и третьей шиной данных ячейки, четвертая шина данных которой соединена с вторыми входами третьей, пятой и шестой схем сравнения, первый двунаправленный вход второго шинного формирователя соединен с первой шиной данных ячейки, третья шина данных которой соединена с первыми двунаправленными входами третьего и четвертого шинных формирователей, вторые двунаправленные входы второго и третьего шинного формирователей соединены с четвертой шиной данных ячейки, вторая шина данных которой соединена с вторым двунправленным входом четвертого шинного формирователя.

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для регистрации сигналов | 1988 |

|

SU1560980A1 |

| Устройство для встроенного тестового контроля | 1986 |

|

SU1324029A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1989 |

|

SU1667090A1 |

| УСТРОЙСТВО АУТЕНТИФИКАЦИИ ПРОГРАММНЫХ МОДУЛЕЙ | 1998 |

|

RU2146834C1 |

| Устройство для контроля знаний обучаемых | 1990 |

|

SU1758658A1 |

| Устройство для сложения | 1984 |

|

SU1265760A1 |

| Устройство для ввода информации | 1989 |

|

SU1682996A1 |

| Устройство для сопряжения датчиков с электронной вычислительной машиной | 1984 |

|

SU1208557A2 |

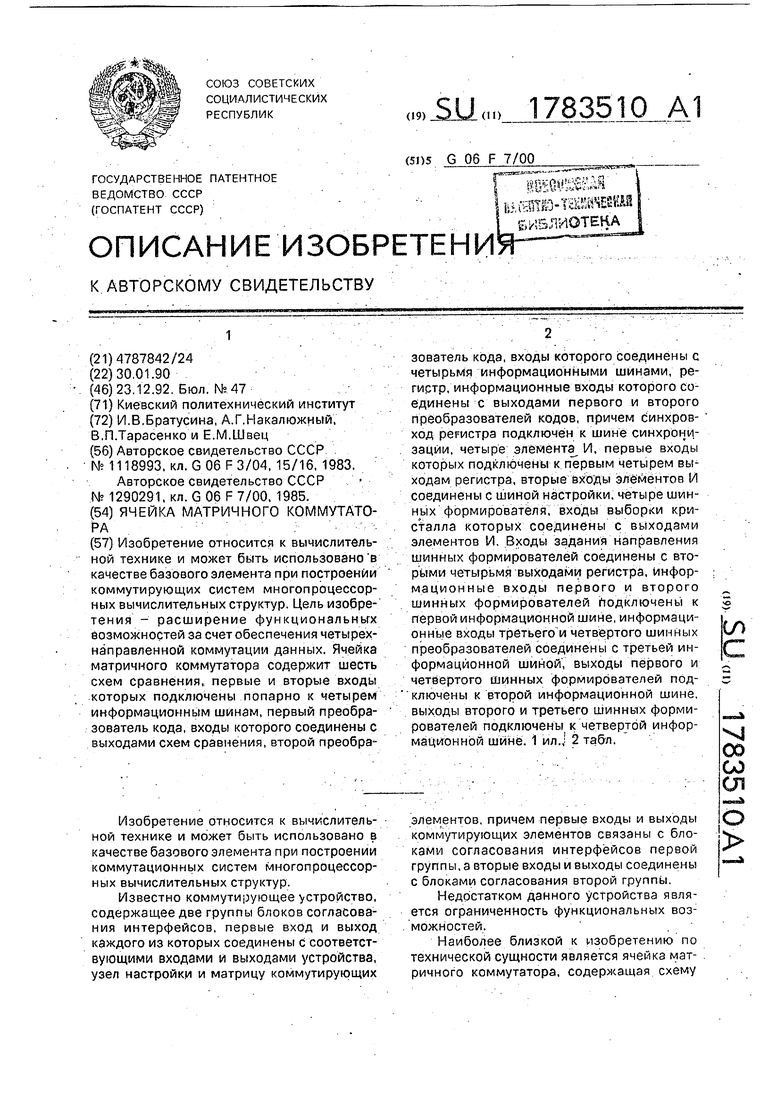

Изобретение относится к вычислительной технике и может быть использовано в качестве базового элемента при построении коммутирующих систем многопроцессорных вычислительных структур. Цель изобре- тения - расширение функциональных возможностей за счет обеспечения четырех- направленной коммутации данных. Ячейка матричного коммутатора содержит шесть схем сравнения, первые и вторые входы которых подключены попарно к четырем информационным шинам, первый преобразователь кода, входы которого соединены с выходами схем сравнения, второй преобраИзобретение относится к вычислительной технике и может быть использовано в качестве базового элемента при построении коммутационных систем многопроцессорных вычислительных структур. Известно коммутирующее устройство, содержащее две группы блоков согласования интерфейсов, первые вход и выход каждого из которых соединены с соответствующими входами и выходами устройства, узел настройки и матрицу коммутирующих зователь кода, входы которого соединены с четырьмя информационными шинами, регистр, информационные входы которого соединены с выходами первого и второго преобразователей кодов, причем синхров- ход регистра подключен к шине синхронизации, четыре элемента И. первые входы которых подключены к первым четырем выходам регистра, вторые входы элементов И соединены с шиной настройки, четыре шинных формирователя, входы выборки кристалла которых соединены с выходами элементов И, Входы задания направления шинных формирователей соединены с вторыми четырьмя выходами регистра, инфор- мационные входы первого и второго шинных формирователей подключены к первой информационной шине, информационные входы третьего и четвертого шинных преобразователей соединены с третьей информационной шиной, выходы первого и четвертого шинных формирователей подключены к второй информационной шине, выходы второго и третьего шинных формирователей подключены к четвертой информационной шине. 1 ил.; 2 та5л. элементов, причем первые входы и выходы коммутирующих элементов связаны с блоками согласования интерфейсов первой группы, а вторые входы и выходы соединены с блоками согласования второй группы. Недостатком данного устройства является ограниченность функциональных возможностей. Наиболее близкой к изобретению по технической сущности является ячейка матричного коммутатора, содержащая схему (Л 00 СО сл I

1000001 2000010

О 0 f О

1100

001

1ОО О 01 000 О 11 0.11 О 1О

10 0 1

1010

Открыть шинный формирователь (ШФ) 22 для связи между шиными данных (ШД) 3 и

Открыть ШФ 20 и 21 для связи между ЫД 2 и f

Открыть ШФ 23 для связи между ШД 2 и 3 Открыть ШФ 21 для связи между ШД 1 и 4 Открыть ШФ 20 и 23 для связи между ШД 1 и 3 Открыть ШФ 20 дли связи между ШД 1 и 2 Открыть ШФ 22 и 23 для связи между ШД 2,3 и Открыть ШФ 22 и 23 для связи между ШД 2,)k

Открыть ЫФ 20 и 22 для связи между ШД 1,2,3 и 4

Открыть ШФ 20 и 22 для связи между ШД 1,2,3 и

11 1

1010 Открыть ШФ 20 и 22 для связи между ШД 1,2,3 и k

Примечание: Х-состояние разряда безразлично:

-, «f- - направление передачи информации черед шинный формирователь;

- в прямом направлении; 4- в обратном направлении.

Таблица 1

Шифратор 12

| Устройство для сопряжения | 1983 |

|

SU1118993A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Ячейка матричного коммутатора | 1985 |

|

SU1290291A1 |

Авторы

Даты

1992-12-23—Публикация

1990-01-30—Подача