1

12511

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах, содержащих накопитель, выполненный на элементах памяти с ограниченным временем хранения информации (например, динамическая память на элементах со структурой металл - диэлектрик - полупроводник), в качестве устройства местного управления указан- ным накопителем.

Цель изобретения - уменьшение энергопотребления устройства,

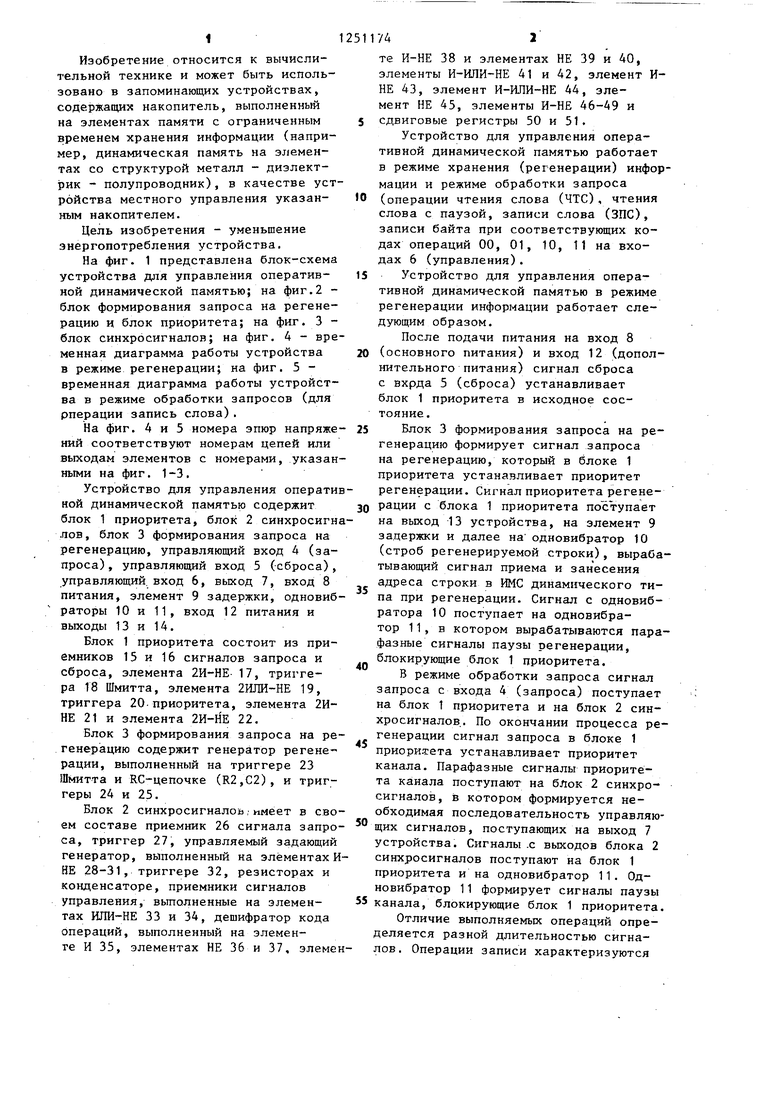

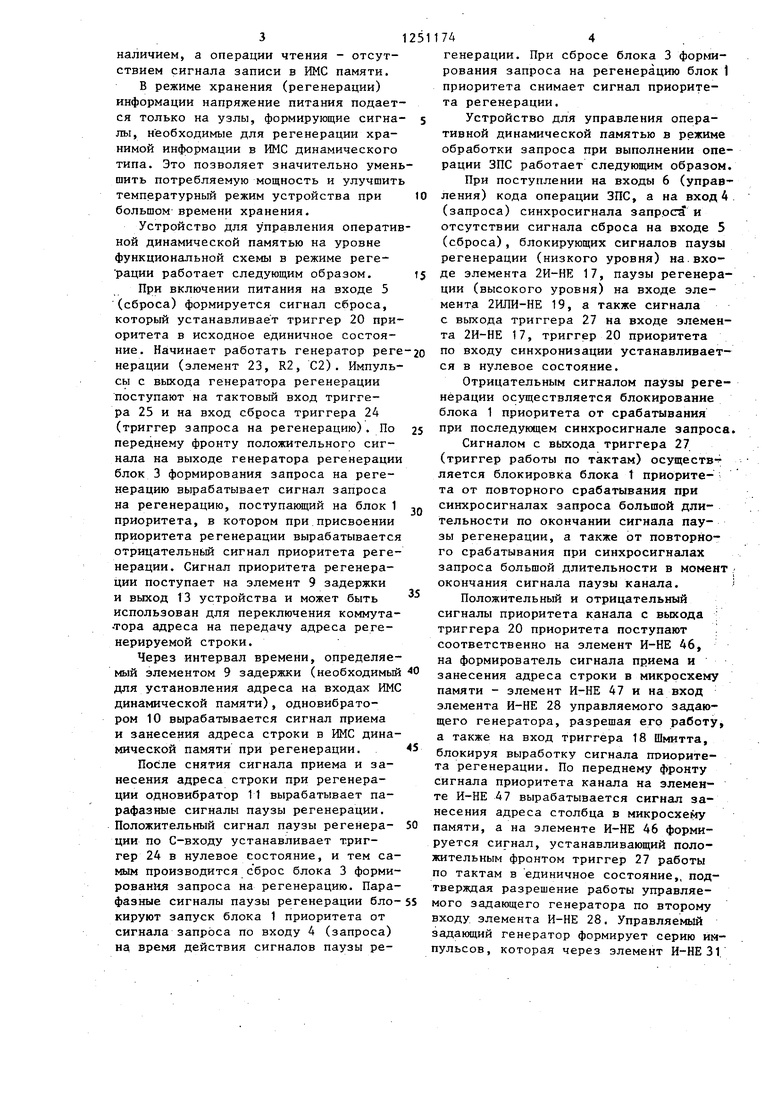

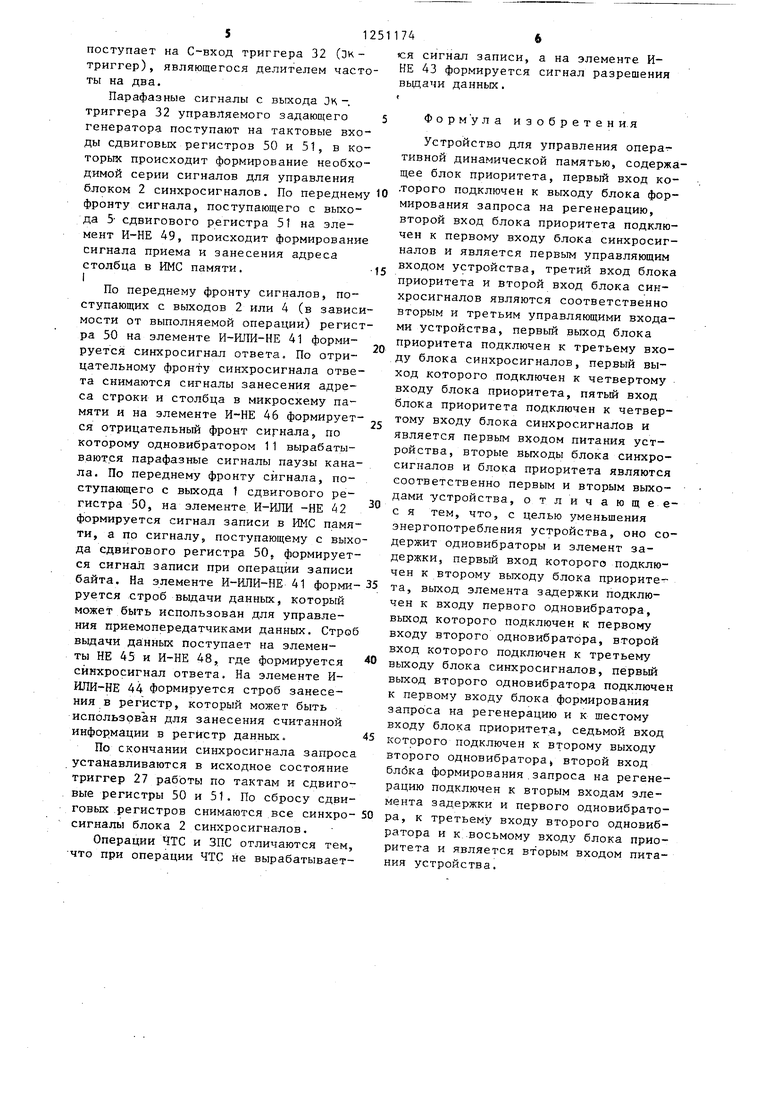

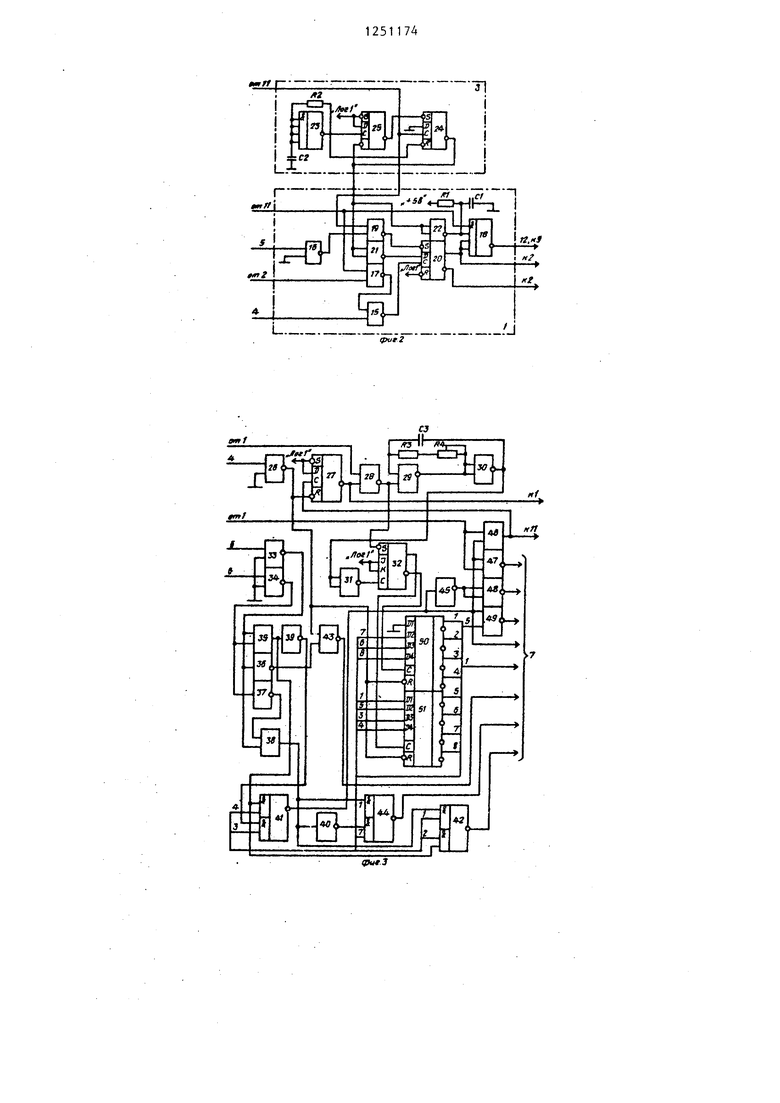

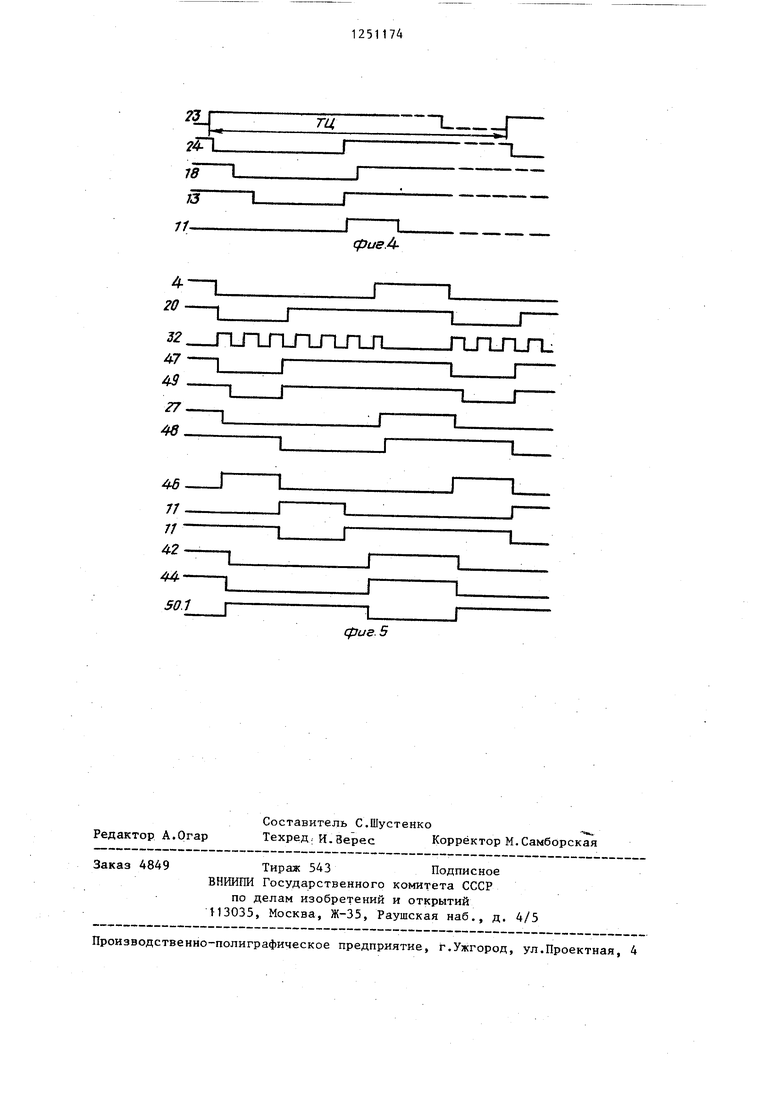

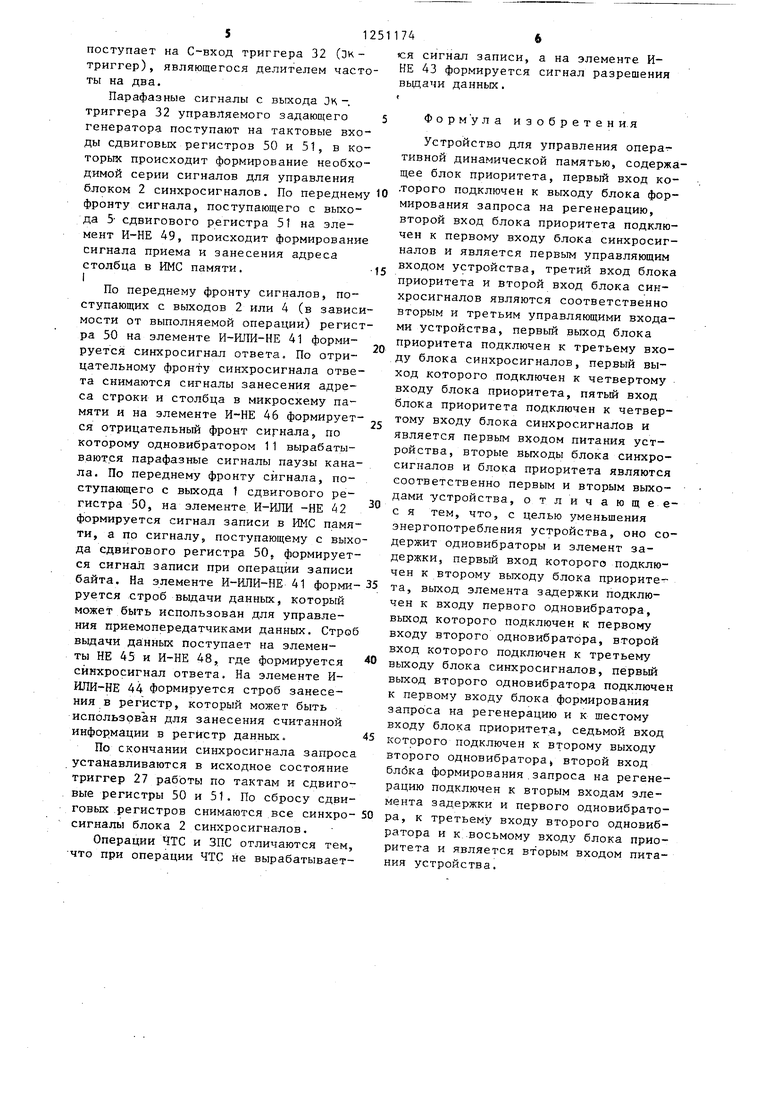

На фиг. 1 представлена блок-схема устройства для управления оператив- ной динамической памятью; на фиг.2 - блок формирования запроса на регенерацию и блок приоритета; на фиг. 3 - блок синхросигналов; на фиг, 4 - временная диаграмма работы устройства в режиме регенерации; на фиг. 5 - временная диаграмма работы устройства в режиме обработки запросов (для рперации запись слова).

На фиг. 4 и 5 номера эпюр напряже НИИ соответствуют номерам цепей или выходам элементов с номерами, указанными на фиг. 1-3,

Устройство для управления оператиной динамической памятью содержит блок 1 приоритета, блок 2 синхросигнлов, блок 3 формирования запроса на регенерацию, управляющий вход 4 (запроса) , управляющий вход 5 (сброса), управляющий, вход 6, выход 7, вход 8 питания, элемент 9 задержки, одновиб раторы 10 и 11, вход 12 питания и выходы 13 и 14.

Блок 1 приоритета состоит из приемников 15 и 16 сигналов запроса и сброса, элемента 2И-НЕ- 17, триггера 18 Шмитта, элемента 2ИЛИ-НЕ 19, триггера 20 приоритета, элемента 2И- НЕ 21 и элемента 2И-НЕ 22.

Блок 3 формирования запроса на ре генер;ацию содержит генератор регенерации, выполненный на триггере 23 Шмитта и КС-цепочке (R2,C2), и триггеры 24 и 25.

Блок 2 синхросигналов;имеет в своем составе приемник 26 сигнала запро са, триггер 27, управляемый задающий генератор, выполненный на элементах P HE 28-31, триггере 32, резисторах и конденсаторе, приемники сигналов управления, вьтолненные на элемен- тах ИЛИ-НЕ 33 и 34, дешифратор кода операций, выполненный на элементе И 35, элементах НЕ 36 и 37, элеме

5

0

5

5

0

7А2

те И-НЕ 38 и элементах НЕ 39 и 40, элементы И-ИЛИ-НЕ 41 и 42, элемент И- НЕ 43, элемент И-ИЛИ-НЕ 44, элемент НЕ 45, элементы И-НЕ 46-49 и сдвиговые регистры 50 и 51.

Устройство для управления оперативной динамической памятью работает в режиме хранения (регенерации) информации и режиме обработки запроса (операции чтения слова (ЧТС), чтения слова с паузой, записи слова (ЗПС), записи байта при соответствующих кодах операций 00, 01, 10, 11 на входах 6 (управления).

Устройство для управления оперативной динамической памятью в режиме регенерации информации работает следующим образом.

После подачи питания на вход 8 (основного питания) и вход 12 (дополнительного питания) сигнал сброса с вхрда 5 (сброса) устанавливает блок 1 приоритета в исходное состояние.

Блок 3 формирования запроса на регенерацию формирует сигнал запроса на регенерацию, который в блоке 1 приоритета устанавливает приоритет регенерации. Сигнал приоритета регенерации с блока 1 приоритета поступает на выход 13 устройства, на элемент 9 задержки и далее на одновибратор 10 (строб регенерируемой строки), вырабатывающий сигнал приема и занесения адреса строки в ИМС динамического типа при регенерации. Сигнал с одновиб- ратора 10 поступает на одновибратор 11, в котором вырабатываются пара- фазные сигналы паузы регенерации, блокирующие блок 1 приоритета.

В режиме обработки запроса сигнал запроса с входа 4 (запроса) поступает на блок 1 приоритета и на блок 2 синхросигналов.. По окончании процесса регенерации сигнал запроса в блоке 1 приоритета устанавливает приоритет канала. Парафазные сигналы приоритета канала поступают на блок 2 синхросигналов, в котором формируется необходимая последовательность управляющих сигналов, поступающих на выход 7 устройства. Сигналы .с выходов блока 2 синхросигналов поступают на блок 1 приоритета и на одновибратор 11. Одновибратор 11 формирует сигналы паузы канала, блокирующие блок 1 приоритета.

Отличие выполняемых операций определяется разной длительностью сигналов. Операции записи характеризуются

3

наличием, а операции чтения - отсутствием сигнала записи в ИМС памяти.

В режиме хранения (регенерации) информации напряжение питания подается только на узлы, формирующие сигна- лы, необходимые для регенерации хранимой информации в ИМС динамического типа. Это позволяет значительно уменьшить потребляемую мощность и улучшить температурный режим устройства при большом-времени хранения.

Устройство для управления оперативной динамической памятью на уровне функциональной схемы в режиме реге- рации работает следующим образом.

При включении питания на входе 5 (сброса) формируется сигнал сброса, который устанавливает триггер 20 приоритета в исходное единичное состояние. Начинает работать генератор реге нерации (злемент 23, R2, С2). Импульсы с выхода генератора регенерации поступают на тактовый вход триггера 25 и на вход сброса триггера 24 (триггер запроса на регенерацию). По переднему фронту положительного сигнала на выходе генератора регенерации блок 3 формирования запроса на регенерацию вырабатывает сигнал запроса на регенерацию, поступающий на блок 1 приоритета, в котором при присвоении приоритета регенерации вырабатывается отрицательньй сигнал приоритета регенерации. Сигнал приоритета регенерации поступает на элемент 9 задержки и выход 13 устройства и может быть использован для переключения коммута- тора адреса на передачу адреса регенерируемой строки.

Через интервал времени, определяемый элементом 9 задержки (необходимый для установления адреса на входах ИМС динамической памяти), одновибрато- ром 10 вырабатывается сигнал приема и занесения адреса строки в ИМС динамической памяти при регенерации.

После снятия сигнала приема и занесения адреса строки при регенерации одновибратор 11 вырабатывает па- рафазные сигналы паузы регенерации. Положительный сигнал паузы регенера- ции по С-входу устанавливает триггер 24 в нулевое состояние, и тем самым производится сброс блока 3 форми- рован11я запроса на регенерацию. Пара- фазные сигналы паузы регенерации бло- кируют запуск блока 1 приоритета от сигнала запроса по входу А (запроса) на время действия сигналов паузы ре

s 10

Т5

20 25 ,„

0 5

0 5

5

1744

генерации. При сбросе блока 3 формирования запроса на регенерацию блок 1 приоритета снимает сигнал приоритета регенерации.

Устройство для управления оперативной динамической памятью в режиме обработки запроса при выполнении операции ЗПС работает следующим образом. При поступлении на входы 6 (управления) кода операции ЗПС, а на вход А (запроса) синхросигнала запроса и отсутствии сигнала сброса на входе 5 (сброса), блокирующих сигналов паузы регенерации (низкого уровня) на.входе элемента 2И-НЕ 17, паузы регенерации (высокого уровня) на входе элемента 2ИЛИ-НЕ 19, а также сигнала с выхода триггера 27 на входе элемента 2И-НЕ 17, триггер 20 приоритета по входу синхронизации устанавливается в нулевое состояние.

Отрицательным сигналом паузы регенерации осуществляется блокирование блока 1 приоритета от срабатывания при последующем синхросигнале запроса.

Сигналом с выхода триггера 27 (триггер работы по тактам) осуществляется блокировка блока 1 приорите- - та от повторного срабатывания при синхросигналах запроса большой длительности по окончании сигнала паузы регенерации, а также от повторного срабатывания при синхросигналах запроса большой длительности в момент окончания сигнала паузы канала.

Положительный и отрицательный сигналы приоритета канала с выхода триггера 20 приоритета поступают . соответственно на элемент И-НЕ 46, на формирователь сигнала приема и занесения адреса строки в микросхему памяти - элемент И-НЕ 47 и на вход элемента И-НЕ 28 управляемого задающего генератора, разрешая его работу, а также на вход триггера 18 Шмитта, блокируя выработку сигнала приоритета регенерации. По переднему фронту сигнала приоритета канала на элементе И-НЕ 47 вырабатывается сигнал занесения адреса столбца в микросхему памяти, а на элементе И-НЕ 46 формируется сигнал, устанавливающий положительным фронтом триггер 27 работы по тактам в единичное состояние,, подтверждая разрешение работы управляемого задающего генератора по второму входу элемента И-НЕ 28. Управляемый задающий генератор формирует серию импульсов, которая через элемент И-НЕ 31,

51

поступает на С-вход триггера 32 (зк - триггер), являющегося делителем частты на два.

Парафазные сигналы с выхода Эк, - триггера 32 управляемого задающего генератора поступают на тактовые входы сдвиговых регистров 50 и 51, в ко торык происходит формирование необходимой серии сигналов для управления блоком 2 синхросигналов. По переднем фронту сигнала, поступающего с выхода 5- сдвигового регистра 51 на элемент И-НЕ 49, происходит формировани сигнала приема и занесения адреса столбца в ИМС памяти.

По переднему фронту сигналов, поступающих с выходов 2 или 4 (в зависмости от выполняемой операции) регисра 50 на элементе И-ШШ-НЕ 41 формируется синхросигнал ответа. По отрицательному фронту синхросигнала ответа снимаются сигналы занесения адреса строки и столбца в микросхему памяти и на элементе И-НЕ 46 формируется отрицательный фронт сигнала, по которому одновибратором 11 вырабатываются парафазные сигналы паузы канала. По переднему фронту сигнала, поступающего с выхода 1 сдвигового регистра 50, на элементе И-ИЛИ -НЕ 42 формируется сигнал записи в ИМС памяти, а по сигналу, поступающему с выхда сдвигового регистра 50, формируется сигнал записи при операции записи байта. На элементе И-ИЛИ-НЕ 41 формируется строб выдачи данных, который может быть использован для управления приемопередатчиками данных. Стро выдачи данных поступает на элементы НЕ 45 и И-НЕ 48, где формируется синхросигнал ответа. На элементе И- ИЛИ-НЕ 44 формируется строб занесения в регистр, который может быть использован для занесения считанной информации в регистр данных.

По скончании синхросигнала запрос устанавливаются в исходное состояние триггер 27 работы по тактам и сдвиговые регистры 50 и 51. По сбросу сдвиговых регистров снимаются все синхро сигналы блока 2 синхросигналов.

Операции ЧТС и ЗПС отличаются тем что при операции ЧТС не вырабатывает

6

ся сигнал записи, а на элементе PI- HE 43 формируется сигнал разрешения выдачи данных.

Формула изобретения

5

0

5

0

15

50

5

0

5

Устройство для управления оперативной динамической памятью, содержащее блок приоритета, первый вход ко- .торого подключен к выходу блока формирования запроса на регенерацию, второй вход блока приоритета подключен к первому входу блока синхросигналов и является первым управляющим входом устройства, третий вход блока приоритета и второй вход блока синхросигналов являются соответственно вторым и третьим управлжощими входами устройства, первый выход блока приоритета подключен к третьему входу блока синхросигналов, первый выход которого подключен к четвертому входу блока приоритета, пятый вход блока приоритета подключен к четвертому входу блока синхросигналов и является первым входом питания устройства, вторые выходы блока синхросигналов и блока приоритета являются соответственно первым и вторым выходами устройства, о т л и ч а ю щ е.е- с я тем, что, с целью уменьшения энергопотребления устройства, оно содержит одновибраторы и элемент задержки, первьм вход которого подключен к второму выходу блока приоритета, выход элемента задержки подключен к входу первого одновибратора, выход которого подключен к первому входу второго одновибратора, второй вход которого подключен к третьему выходу блока синхросигналов, первый выход второго одновибратора подключен к первому входу блока формирования запроса на регенерацию и к шестому входу блока приоритета, седьмой вход которого подключен к второму выходу второго одновибратораJ второй вход блбка формирования,запроса на регенерацию подключен к вторым входам элемента задержки и первого одновибратора, к третьему входу второго одновибратора и к вocьмoмy входу блока приоритета и является вт орым входом питания устройства.

puf3

114 20

JrLr rLrLS

J

J-

(риеЛ

rLn-TLTL

(pua.B

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Устройство для регенерации информации динамической памяти | 1988 |

|

SU1635213A1 |

| Запоминающее устройство | 1985 |

|

SU1256096A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для управления регенерацией информации в динамической памяти | 1986 |

|

SU1377909A1 |

| Устройство для сопряжения каналов ЭВМ с периферийными устройствами | 1990 |

|

SU1732348A1 |

| Устройство для регенерации динамической памяти | 1988 |

|

SU1587594A1 |

| УСТРОЙСТВО ДЛЯ СБОРА, РЕГИСТРАЦИИ И СТАТИСТИЧЕСКОЙ ОБРАБОТКИ ПОЛЕТНОЙ ИНФОРМАЦИИ | 1996 |

|

RU2115163C1 |

Изобретение относится,к вычислительной технике и может быть использовано в запоминающих устройствах, содержащих накопитель, выполненный на элементах памяти с ограниченным временем хранения информации. . Цель изобретения состоит в уменьше- . НИИ энергопотребления устройства. Устройство для управления оперативной динамической памятью содержит блок 1 приоритета, блок 2 синхросигналов, блок 3 формирования запроса на регенерацию, управлякицие входы 4 (запроса), 5 (сброса) и 6, выход 7, вход 8 питания, элемент 9 задержки, одновибраторы 10 и 11, вход 12 питания и выходы 13 и 14. В режиме хранения (регенерации) информации напряжение питания подается только на уз- лы, формирующие сигналы, необходимые для регенерации хранимой информации. 5 ил. (Л |С ел si 1

| Резонансный высоковольтный инвертор | 1987 |

|

SU1424107A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для управления оперативной памятью | 1978 |

|

SU752338A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-15—Публикация

1985-01-21—Подача